dsp 第四章1

- 格式:ppt

- 大小:616.00 KB

- 文档页数:73

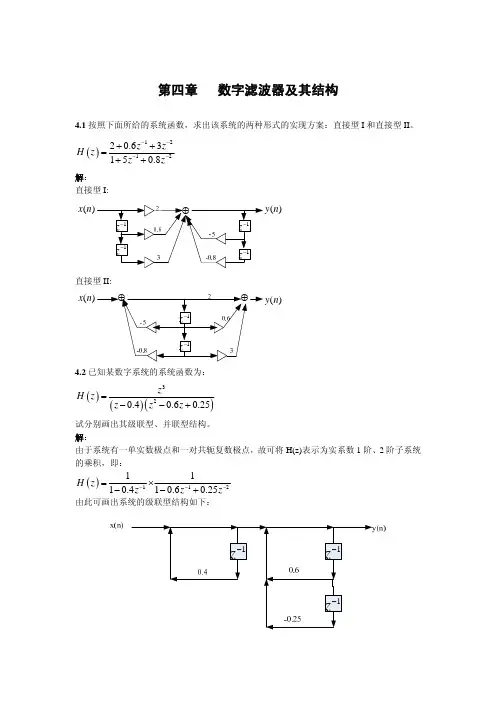

第四章指令系统§4.1 寻址方式§4.2 语法格式§4.3 指令集XCHL《DSP原理及应用》讲稿1§4.1 寻址方式•TMS320提供三种寻址方式:•立即寻址•直接寻址•间接寻址•立即寻址操作数由指令提供,前面加#–短立即数寻址:8位、9位或13位,操作数在指令字中–长立即数寻址:16位,操作数需单独占一个字–返回本章首页XCHL《DSP原理及应用》讲稿2§4.2 语法格式返回本章首页•DSP汇编语言语法操作码【操作数】;【注释】–操作码:表明指令功能的助记符,‘C24X的指令集中共有86种。

–操作数:给出变量或变量的寻址方式–注释•指令中各种符号及其含义参见教材P118表4.3•DSP指令的存储空间指令集中大部分是单字指令,其余都是双字指令,它们的操作数基本都是长立即数。

•DSP指令的执行时间大部分是单周期指令,有部分双周期指令、三周期指令和四周期指令。

XCHL《DSP原理及应用》讲稿6§4.3 指令集按照功能划分,DSP指令集中共有86种指令代码,配合不同的寻址方式,可变化出多条指令。

这些指令大体上可分为四种:•数据传送类:共30种助记符•算术运算类:共22种助记符•逻辑运算类:共13种助记符•分支转移类:共21种助记符返回本章首页XCHL《DSP原理及应用》讲稿7§4.3.1数据传送类指令返回本节首页共30种操作助记符。

其中包括各种寄存器的装载指令14种,寄存器值的存储指令4种,堆栈操作4种,数据或程序存储器的读写6种,I/O单元读写2种。

•装载寄存器•存储寄存器值•堆栈操作•读写数据或程序存储器•读写I/O单元XCHL《DSP原理及应用》讲稿8装载寄存器•装载累加器–LACC:左移装载累加器•LACC dma [,shift]•LACC dma ,16•LACC ind [,shift[,ARn]]•LACC ind ,16[,ARn]•LACC #lk [,shift]–LACL:装载累加器低位并清累加器高位•LACL dma•LACL ind[,ARn]•LACL #k–LACT:按TREG规定左移后再转载入累加器•LACT dma•LACT ind[,ARn]–PAC:用乘积寄存器PREG装载累加器,移位方式由ST1中的PM 确定•PAC返回次节首页XCHL《DSP原理及应用》讲稿9•装载临时寄存器TREG–LT:将指定数据存储器的内容装入TREG。

第4章定时器及硬件中断4.1定时器硬件结构原理TMS320VC5509 DSPs有两个独立20-bit的软件可编程通用减数计数定时器,可用于产生周期中断给CPU或给DMA控制器发送周期同步事件或给外部设备提供周期信号,也可以用于外部事件计数。

20-bit的通用定时器是减数计数器,它由两部分组成:4位预分频计数器(PSC)和16位主计数器(TIM),定时器结构框图如图4-1所示。

4-1通用定时器结构框图预分频计数器PSC由输入时钟驱动,可以是内部CPU时钟或外部时钟(当FUNC=11b时使用外部时钟,从TIN/TOUT引脚输入,当FUNC为其它值时使用内部CPU时钟),每输入一个时钟PSC减1。

每当PSC减到0,主计数器TIM减1,每当TIM 减到0,定时器给CPU发出一个中断请求TINT,一个同步事件TEVT给DMA控制器和一个输出到定时器引脚(如果FUNC=01b)。

定时器输出速率为:)1()1++=PRD TDDR TINT (输入时钟频率频率 式中: )1()1(++PRD TDDR >4预分频寄存器PRSC 由两部分组成:预分频周期寄存器TDDR 和预分频器PSC ,如图4-2所示;预分频器PSC 减到0时,当再有一个输入时钟输入时,预分频器PSC 从预分频周期寄存器TDDR 重新装载预分频器PSC ,当定时器设定为自动装载模式时(ARB=1)。

周期寄存器PRD 和计数器TIM 都为16位寄存器。

计数器TIM 减到0时, TIM 从PRD 重新装载,当定时器设定为自动装载模式时(ARB=1)。

定时器控制寄存器TCR 如图4-3所示,使用它的特定位可以实现对定时器进行配置、启动、停止、装载和重新装载等,表4-1是对定时器控制寄存器TCR 每位进行说明。

R=读 W=写 -n=复位值图4-3 定时器控制寄存器TCR定时器引脚功能模式合法转换如图4-4所示,FUNC 位的某些改变会产生一个错误并反映在ERRTIM 位,FUNC = 01b 到 FUNC = 00b 或 11b ,FUNC = 10b 到 FUNC = 00b 或 11b ,FUNC = 11b 到任意值都会产生一个错误,当ERRTIM = 1,复位DSP 并重新初始化定时器。