DSP 第四章 DMA

- 格式:pdf

- 大小:243.45 KB

- 文档页数:30

DMA-DSP542 http:第一章DSP542控制單板(LH-091)----------------------------1 1-1單板簡介-----------------------------------------------------------11-2單板硬體功能介紹------------------------------------------------5第二章TLC320AC01功能簡介---------------------------------7 第三章TMS320C542與TLC320AC01之連結及控制-----11第四章以C54XCode Explorer環境代數語言實現TLC320 AC01控制實習------------------------------------------15 第五章以Code Composer Studio環境C語言實現TLC 320AC01控制實習------------------------------------21第一章DSP 542控制單板(LH-091)第1章D S P542控制單板(L H-091)1-1 單板簡介一般單晶片對類比訊號處理的精確度在於其ADC及DAC轉換介面及單晶的處理能力、借由本單板以高階之TI C54X系列DSP直接配合TI含有DAC及ADC轉換介面之TCL320AC01晶片而成的單板控制模組,來驗證C54X系列對類比訊號處理的能力及其測試,同時也可從單板上的預留測試座引用訊號線出來做控制測試,實為方便的專題製作工具。

至於單板上也擁有擴接長高科技出品之DSP LAB STN顯示模組及步進馬達模組和同為TI另一系列之AIC模組等等的強大功能。

而TLC320AC01與TLC32044晶片同為德州儀器(Texas Instrument簡稱TI)製造的ADC,DAC轉換的晶片,唯TLC320AC01於處理信號源的時候僅提供+5V單電源,而TLC32044須另提供-5V之雙電源,可由單板上的μ10電源調整IC取得。

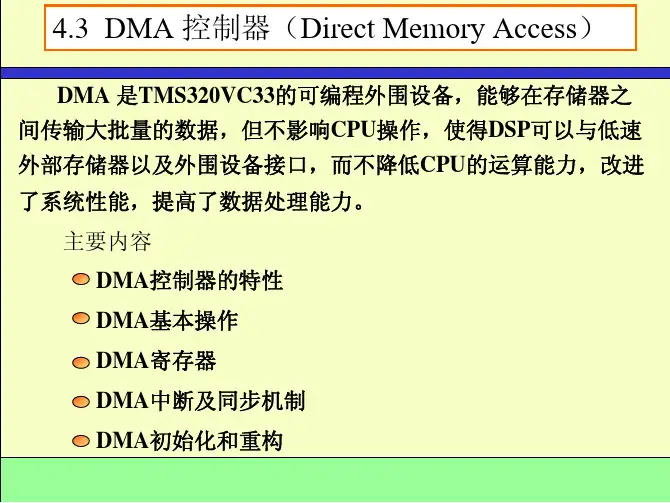

第4章定时器及硬件中断4.1定时器硬件结构原理TMS320VC5509 DSPs有两个独立20-bit的软件可编程通用减数计数定时器,可用于产生周期中断给CPU或给DMA控制器发送周期同步事件或给外部设备提供周期信号,也可以用于外部事件计数。

20-bit的通用定时器是减数计数器,它由两部分组成:4位预分频计数器(PSC)和16位主计数器(TIM),定时器结构框图如图4-1所示。

4-1通用定时器结构框图预分频计数器PSC由输入时钟驱动,可以是内部CPU时钟或外部时钟(当FUNC=11b时使用外部时钟,从TIN/TOUT引脚输入,当FUNC为其它值时使用内部CPU时钟),每输入一个时钟PSC减1。

每当PSC减到0,主计数器TIM减1,每当TIM 减到0,定时器给CPU发出一个中断请求TINT,一个同步事件TEVT给DMA控制器和一个输出到定时器引脚(如果FUNC=01b)。

定时器输出速率为:)1()1++=PRD TDDR TINT (输入时钟频率频率 式中: )1()1(++PRD TDDR >4预分频寄存器PRSC 由两部分组成:预分频周期寄存器TDDR 和预分频器PSC ,如图4-2所示;预分频器PSC 减到0时,当再有一个输入时钟输入时,预分频器PSC 从预分频周期寄存器TDDR 重新装载预分频器PSC ,当定时器设定为自动装载模式时(ARB=1)。

周期寄存器PRD 和计数器TIM 都为16位寄存器。

计数器TIM 减到0时, TIM 从PRD 重新装载,当定时器设定为自动装载模式时(ARB=1)。

定时器控制寄存器TCR 如图4-3所示,使用它的特定位可以实现对定时器进行配置、启动、停止、装载和重新装载等,表4-1是对定时器控制寄存器TCR 每位进行说明。

R=读 W=写 -n=复位值图4-3 定时器控制寄存器TCR定时器引脚功能模式合法转换如图4-4所示,FUNC 位的某些改变会产生一个错误并反映在ERRTIM 位,FUNC = 01b 到 FUNC = 00b 或 11b ,FUNC = 10b 到 FUNC = 00b 或 11b ,FUNC = 11b 到任意值都会产生一个错误,当ERRTIM = 1,复位DSP 并重新初始化定时器。

第二章3、处理器工作方式状态寄存器PMST 中的MP/MC、OVLY 和DROM 三个状态位对C54x的存储空间结构各有何影响?当OVLY= 0 时,程序存储空间不使用内部RAM。

当OVLY= 1 时,程序存储空间使用内部RAM。

内部RAM 同时被映射到程序存储空间和数据存储空间。

当MP/ MC=0 时,4000H~EFFFH 程序存储空间定义为外部存储器;F000H~FEFFH 程序存储空间定义为内部ROM;当MP/ MC=1 时,4000H~FFFFH 程序存储空间定义为外部存储。

DROM=0:0000H~3FFFH——内部RAM ;4000H~FFFFH——外部存储器;DROM=1 :0000H~3FFFH——内部RAM;4000H~EFFFH——外部存储器;F000H~FEFFH——片内ROM;FF00H~FFFFH——保留。

4 、TMS320C54x 芯片的片内外设主要包括哪些电路?①通用I/O 引脚②定时器③时钟发生器④主机接口HPI⑤串行通信接口⑥软件可编程等待状态发生器⑦可编程分区转换逻辑5、TMS320C54x 芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?六个操作阶段:①预取指P;将PC 中的内容加载PAB ②取指F; 将读取到的指令字加载PB③译码D; 若需要,数据1 读地址加载DAB;若需要,数据2 读地址加载CAB;修正辅助寄存器和堆栈指针④寻址A; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB⑤读数R; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB;⑥执行X。

执行指令,写数据加载EB。

6、TMS320C54x 芯片的流水线冲突是怎样产生的?有哪些方法可以避免流水线冲突?答:’C54x 的流水线结构,允许多条指令同时利用CPU 的内部资源。

由于CPU 的资源有限,当多于一个流水线上的指令同时访问同一资源时,可能产生时序冲突。

《DSP原理》教学大纲一、课程基本信息1、课程代码:MI3152、课程名称:DSP原理/ Principle of digital signal processors3、学时/学分:18学时/1学分4、先修课程:信号与系统、微机原理、电子技术基础5、面向对象:电气信息类专业6、开课院(系)、教研室:电子信息与电气工程学院信息检测与仪器系7、教材、教学参考书:《数字信号处理》胡广书,清华大学出版社2001《TMS320C6000 USER’S GUIDE》《TMS320C6000DSP原理及应用》,电子工业出版社2001。

二、课程的性质和任务本课程属于电子信息类本科高年级的专业选修课程。

作为扩大知识面,了解最新的DSP技术的发展趋势以及开发流程。

数字信号处理作为信号和信息处理的一个分支学科,已渗透到科学研究、技术开发、工业生产、国防和国民经济的各个领域。

自70年代末80年代初DSP(数字信号处理)芯片诞生以来,数字信号处理系统的运算速度得到了极大的改善,其实时性已接近甚至超过模拟信号处理系统,DSP芯片,也称数字信号处理器,是一种特别适合进行数字信号处理运算的微处理器。

DSP芯片的出现和发展,促进数字信号处理技术的提高,许多新系统、新算法应运而生,其应用领域不断拓展。

目前,DSP芯片已广泛应用于通信、自动控制、航天航空、军事、医疗等领域。

因此,学习和掌握DSP芯片的基本原理和开发流程,对于将来从事电子信息类工作的工科本科生来说是必不可少的。

通过该门课程的学习,期望学生能了解DSP技术的最新发展,了解其与单片机及通用微机处理器的不同,掌握某些特定的DSP芯片的开发流程和方法,扩展学生的知识面,提高学生快速解决问题的能力。

通过布置相关的上机实验和文献综述,要求学生初步了解TI公司的TMS320系列DSP的选型思路、开发流程等理论和方法。

三、课程的教学内容和要求《DSP原理》的教学内容分为五部分,对不同的内容提出不同的教学要求。