环路跟踪性能

- 格式:pptx

- 大小:2.32 MB

- 文档页数:125

锁相技术(往届部分题目)一、选择题1、为了加大环路的捕获带,应______环路增益或______环路带宽,但提高环路的跟踪性能的要求与之___。

A 、提高、增加、相反B 、提高、增加、相同C 、降低、增加、相反D 、提高、减小、相反2、在二阶锁相环中,在环路滤波器与VCO 之间插入一直流放大器,放大倍数为10,直流放大器使环路参数n ω____,H ω____,p ω______。

A 、减少、增加、增加B 、增加、增加、增加C 、增加、增加、减少D 、减少、减少、增加3、环路对内部VCO 的噪声呈现____-滤波器作用,对外部输入的噪声呈现____-滤波器作用。

A 、带通、低通B 、低通、带通C 、高通、低通D 、低通、高通4、环路的捕获带、同步带和快捕带的关系是:_____A 、H ω>p ω>L ωB 、p ω>L ω>H ωC 、L ω>H ω>p ωD 、p ω>H ω>L ω5、环路锁定时,瞬时频差_____,固有频差______控制频差,相差为_____,控制电压为___.A 、很小的量、等于、0、常数B 、0、大于、很小的量、变量C 、0、小于、很小的量、变量D 、0、等于、很小的量、常数6、相位噪声的时域噪声表示_____,频域表示______,它们的关系是____.A 、方差、功率、拉氏变换B 、功率、方差、傅氏变换C 、方差、功率谱密度、傅氏变换D 、方差、功率谱密度、Z 变换7、在一阶环中,下列哪种情况环路能锁定_______。

A 、环路增益小于固有频差B 、环路增益大于固有频差C、环路增益等于固有频差D、环路增益小于固有频差8、锁相环稳定的条件是:________。

A、理想情况下相位余量为0°,实际情况相位余量60°B、理想情况下相位余量小于0°,实际情况相位余量0°C、理想情况下相位余量为60°,实际情况相位余量0°D、理想情况下相位余量为180°,实际情况相位余量-60°9、当环路的相位裕度接近于0°,在滤波器中增加______来改善环路的稳定性。

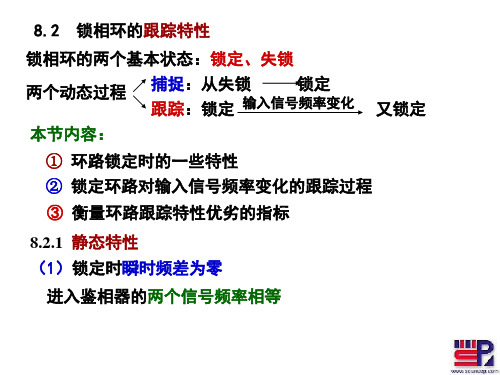

第一章锁相环路的基本工作原理:1.锁相环路是一个闭环的相位控制系统;锁相环路(PLL)是一个相位跟踪系统,它建立了输出信号顺时相位与输入信号瞬时相位的控制关系。

2. 若输入信号是未调载波,θi(t)即为常数,是u i(t)的初始相位;若输入信号时角调制信号(包括调频调相),θi(t)即为时间的函数。

3.ωo是环内被控振荡器的自由振荡角频率;θo(t)是以自由振荡的载波相位ωo t为参考的顺时相位,在未受控制以前它是常数,在输入信号控制之下,θo(t)即为时间的函数。

4. 输入信号频率与环路自由振荡频率之差,称为环路的固有频率环路固有角频差:输入信号角频率ωi与环路自由振荡角频率ωo之差。

瞬时角频差:输入信号频率ωi与受控压控振荡器的频率ωv之差。

控制角频差:受控压控振荡器的频率ωv与自由振荡频率ωo之差。

三者之间的关系:瞬时频差=固有频差-控制频差。

5. 从输入信号加到锁相环路的输入端开始,一直到环路达到锁定的全过程,称为捕获过程。

6. 对一定环路来说,是否能通过捕获而进入同步完全取决于起始频差。

7. 锁定状态又叫同步状态:①同频②相位差固定8. 锁定之后无频差,这是锁相环路独特的优点。

9. 捕获时间T p的大小除决定于环路参数之外,还与起始状态有关。

10.若改变固有频差∆ωo,稳定相差θe(∞)会随之改变。

11.锁相环路基本构成:由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)组成。

12.鉴相器是一个相位比较装置,鉴相器的电路总的可以分为两大类:第一类是相乘器电路,第二类是序列电路。

13.环路滤波器具有低通特性。

常见的环路滤波器有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器三种。

(会推导它们的传输算子)14.电压振荡器是一个电压-频率变换装置,它的振荡频率应随输入控制电压u c(t)线性的变化。

15.压控振荡器应是一个具有线性控制特性的调频振荡器。

要求压控振荡器的开环噪声尽可能低,设计电路时应注意提高有载品质因素和适当增加振荡器激励功率,降低激励级的内阻和振荡管的噪声系数。

1锁相环的基本原理1.1 锁相环的基本构成锁相环路(PLL)是一个闭环的跟踪系统,它能够跟踪输入信号的相位和频率。

确切地讲,锁相环是一个使用输出信号(由振荡器产生的)与参考信号或者输入信号在频率和相位上同步的电路。

在同步(通常称为锁定)状态,振荡器输出信号和参考信号之间的相位差为零,或者保持常数。

如果出现相位误差,一种控制机理作用到振荡器上,使得相位误差再次减小到最小。

在这样的控制系统中,实际输出信号的相位锁定到参考信号的相位,因而我们称之为锁相环。

锁相环在无线电技术的许多领域,如调制与解调、频率合成、数字同步系统等方面得到了广泛的应用,已经成为现代模拟与数字通信系统中不可缺少的基本部件。

锁相环通常由鉴相器(PD),环路滤波器(LF)和压控振荡器(VCO)三个基本部件组成。

如图1-1所示:VCOLFPD图1-1 锁相环的基本构成在PLL中,PD是一个相位比较器,比较基准信号(输入信号)(t)与输出信号(t)之间的相位偏差,并由此产生误差信号;LF是一个低通滤波器,用来滤除中的高频成分,起滤波平滑作用,以保证环路稳定和改善环路跟踪性能,最终输出控制电压;VCO是一个电压/频率变换装置,产生本地振荡频率,其振荡频率受控制,产生频率偏移,从而跟踪输入信号的频率。

整个锁相环路根据输入信号与本地振荡信号之间的相位误差对本地振荡信号的相位进行连续不断的反馈调节,从而达到使本地振荡信号相位跟踪输入信号相位的目的。

1.1.1 鉴相器鉴相器是一个相位比较器,比较两个输入信号的相位,产生误差相位,并转换为误差电压。

鉴相器有多种类型,如模拟乘法器型、取样保持型、边沿触发数字型等,其特性也可以是多种多样的,有正弦特性、三角特性、锯齿特性等,作为原理分析,通常使用正弦特性的鉴相器,理由是正弦理论比较成熟,分析简单方便,实际上各种鉴相特性当信噪比降低时,都趋向于正弦特性。

常用的正弦鉴相器可以用模拟乘法器与低通滤波器的串接作为模型,如图1-2所示。

第九章 PN 码的跟踪pn 码的捕获只能使本地的pn 码与信号的pn 码实现同步,而能使本地的pn 码保持与接收的pn 码精细同步的功能称为pn 码的跟踪,实现pn 码跟踪的基本原理是缩相环原理,主要 环路的稳态跟踪性能,暂态捕获性能及失锁性能,从码跟踪环的的构成形式上可分为三类:全时间码跟踪环,时分的跟踪环和τ摆动环,由于码跟踪环适用于许多不同系统,如测距,授时,时延系统,以及数据传输系统,不同的扩频系统有不同的使用要求,对码跟踪性能要求重点也就不一样,我们着重于在 的应用 9.19.1.1相干码跟踪环————基带的跟踪环所谓相干码跟踪环是指环路中载波码率和相位是精确已知,所以码跟踪环可工作在基带信号上,也就是可把相干的跟踪环看成基带的跟踪环,在 环跟踪未实现前如何 相干在载波,或说载波环已锁定,可这样实现,如果收发码 的误差不很大,且又都很稳定,相 在完成码捕获时,可以使本地的pn 码与接收pn 码的时逆差在0附近,4/π≤t ,这样就可得到解扩信号(相关值接近于1(>3/4)即解扩后信噪比较高)这时栽波环就可进入锁定状态(一是信噪比较高,二是在没有码跟踪环的情况下要求pn 码的准同步保持一下长时间,使载波有足够的时间进入锁定态)相干码跟踪环的构成如图)()(2)(t n T t pn p t y +-=其中n(T)----白高斯噪声的抽样函数 T----接受码相干发射机时延 p----码的时延)2/(c e T t pn pn +-=Λτ)2/(c L T t pn pn --=Λτ)cos(00θω+=t pn r E E)cos(00θω+=t pn r L L其中Λτ是码环时T 的估比值,T c 是码元宽度忽略 ,如果载波的 跟踪已实现,则0'00'0,θω≈=a v)]2/()()[()2/(2)(~c c pw L T T t pn t n s L T T T R p t e --+--=ΛΛ其中L(s)[g(t)]表示对时间乘数g(t)进行Heaviside L(s)即)(*)()()()]()[(t g t l d t g l t g s L =-=⎰+∞∞-τττl(t)是低通滤波特性 且L(s)=£[e(t)] 其中£为拉氏变换 同理可得)]2/()()[()2/()(~c c pw E T T t pn t n s L T T T R p t e +-+--=ΛΛ输入 环路滤波器的误差信号为)()()]2/()2/((2)(t n t n T T T R T T T R p t e L E c pn c pn -++----=ΛΛε式中n E (t)= )]2/()()[(c T T t pn t n s L +-Λn L (t)= )]2/()()[(c T T t pn t n s L --Λ如不考虑n E (t) n L (t),则误差控制信号曲线如图,在-T c /2- T c /2之间S 曲线有 斜率,等于2/T c 线性化的环路分称为L E cn n T pe -+=εε2注意:延迟锁相环完成1。

1锁相环的基本原理1.1 锁相环的基本构成锁相环路(PLL)是一个闭环的跟踪系统,它能够跟踪输入信号的相位和频率。

确切地讲,锁相环是一个使用输出信号(由振荡器产生的)与参考信号或者输入信号在频率和相位上同步的电路。

在同步(通常称为锁定)状态,振荡器输出信号和参考信号之间的相位差为零,或者保持常数。

如果出现相位误差,一种控制机理作用到振荡器上,使得相位误差再次减小到最小。

在这样的控制系统中,实际输出信号的相位锁定到参考信号的相位,因而我们称之为锁相环。

锁相环在无线电技术的许多领域,如调制与解调、频率合成、数字同步系统等方面得到了广泛的应用,已经成为现代模拟与数字通信系统中不可缺少的基本部件。

锁相环通常由鉴相器(PD),环路滤波器(LF)和压控振荡器(VCO)三个基本部件组成。

如图1-1所示:VCOLFPD图1-1 锁相环的基本构成在PLL中,PD是一个相位比较器,比较基准信号(输入信号)(t)与输出信号(t)之间的相位偏差,并由此产生误差信号;LF是一个低通滤波器,用来滤除中的高频成分,起滤波平滑作用,以保证环路稳定和改善环路跟踪性能,最终输出控制电压;VCO是一个电压/频率变换装置,产生本地振荡频率,其振荡频率受控制,产生频率偏移,从而跟踪输入信号的频率。

整个锁相环路根据输入信号与本地振荡信号之间的相位误差对本地振荡信号的相位进行连续不断的反馈调节,从而达到使本地振荡信号相位跟踪输入信号相位的目的。

1.1.1 鉴相器鉴相器是一个相位比较器,比较两个输入信号的相位,产生误差相位,并转换为误差电压。

鉴相器有多种类型,如模拟乘法器型、取样保持型、边沿触发数字型等,其特性也可以是多种多样的,有正弦特性、三角特性、锯齿特性等,作为原理分析,通常使用正弦特性的鉴相器,理由是正弦理论比较成熟,分析简单方便,实际上各种鉴相特性当信噪比降低时,都趋向于正弦特性。

常用的正弦鉴相器可以用模拟乘法器与低通滤波器的串接作为模型,如图1-2所示。