JK触发器真值表

- 格式:doc

- 大小:17.12 KB

- 文档页数:3

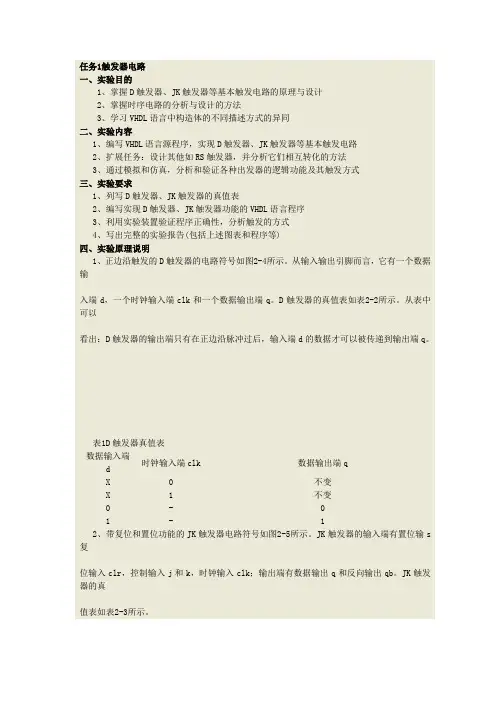

任务1触发器电路一、实验目的1、掌握D触发器、JK触发器等基本触发电路的原理与设计2、掌握时序电路的分析与设计的方法3、学习VHDL语言中构造体的不同描述方式的异同二、实验内容1、编写VHDL语言源程序,实现D触发器、JK触发器等基本触发电路2、扩展任务:设计其他如RS触发器,并分析它们相互转化的方法3、通过模拟和仿真,分析和验证各种出发器的逻辑功能及其触发方式三、实验要求1、列写D触发器、JK触发器的真值表2、编写实现D触发器、JK触发器功能的VHDL语言程序3、利用实验装置验证程序正确性,分析触发的方式4、写出完整的实验报告(包括上述图表和程序等)四、实验原理说明1、正边沿触发的D触发器的电路符号如图2-4所示。

从输入输出引脚而言,它有一个数据输入端d,一个时钟输入端clk和一个数据输出端q。

D触发器的真值表如表2-2所示。

从表中可以看出:D触发器的输出端只有在正边沿脉冲过后,输入端d的数据才可以被传递到输出端q。

表1D触发器真值表数据输入端时钟输入端clk 数据输出端qdX 0 不变X 1 不变0 - 01 - 12、带复位和置位功能的JK触发器电路符号如图2-5所示。

JK触发器的输入端有置位输s 复位输入clr,控制输入j和k,时钟输入clk;输出端有数据输出q和反向输出qb。

JK触发器的真值表如表2-3所示。

表2-3JK触发器真值表输入端输出端st clr clk j k Q qb0 1 X X X 1 01 0 X X X 0 10 0 X X X X X1 1 - 0 1 0 11 1 - 1 1 翻转翻转1 1 - 0 0 保持保持1 1 - 1 0 1 01 1 0 X X 保持保持编辑本段真值表定义表征逻辑事件输入和输出之间全部可能状态的表格。

真值表列出命题公式真假值的表。

通常以1表示真,0 表示假。

命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

74LS90引脚功能及真值表74LS90 是一种常用的中规模集成计数器,在数字电路设计中有着广泛的应用。

下面我们就来详细了解一下 74LS90 的引脚功能和真值表。

74LS90 是一个二五十进制异步计数器,它由四个主从 JK 触发器和一些附加门电路组成。

这款芯片一共有 14 个引脚,每个引脚都有着特定的功能。

引脚 1 是 CP0 输入端,用于接收时钟脉冲信号。

当 CP0 有脉冲输入时,计数器在二进制计数模式下工作。

引脚 2 是 Q0 输出端,它输出二进制计数的最低位。

引脚 3 是 Q1 输出端,输出二进制计数的次低位。

引脚 4 是 Q2 输出端,为二进制计数的第三位。

引脚 5 是 CP1 输入端,用于在五进制计数模式下接收时钟脉冲。

引脚 6 是 Q3 输出端,是二进制计数的最高位。

引脚 7 是地(GND)引脚,连接到电路的零电位参考点。

引脚8 是清零端(R0(1)、R0(2)),当这两个引脚同时为高电平时,计数器被清零,所有输出端都变为低电平。

引脚9 是置9 端(S9(1)、S9(2)),当这两个引脚同时为高电平时,计数器被置为 9 状态,即 Q3Q2Q1Q0 = 1001。

引脚 10 是 Q0' 输出端,是 Q0 的反相输出。

引脚 11 是 Q1' 输出端,是 Q1 的反相输出。

引脚 12 是 Q2' 输出端,是 Q2 的反相输出。

引脚 13 是 Q3' 输出端,是 Q3 的反相输出。

引脚 14 是电源(VCC)引脚,通常连接到+5V 电源。

接下来,我们看一下 74LS90 的真值表。

在二进制计数模式下(CP0 输入时钟脉冲,CP1 悬空),计数顺序为 0 1 2 3 4 5 6 7 0,依次循环。

当计数器达到 7 时,再输入一个时钟脉冲,就会回到 0 重新开始计数。

对应的输出状态如下:| CP0 脉冲数| Q3 | Q2 | Q1 | Q0 ||::|::|::|::|::|| 0 | 0 | 0 | 0 | 0 || 1 | 0 | 0 | 0 | 1 || 2 | 0 | 0 | 1 | 0 || 3 | 0 | 0 | 1 | 1 || 4 | 0 | 1 | 0 | 0 || 5 | 0 | 1 | 0 | 1 || 6 | 0 | 1 | 1 | 0 || 7 | 0 | 1 | 1 | 1 |在五进制计数模式下(CP1 输入时钟脉冲,CP0 悬空),计数顺序为 0 1 2 3 4 0,依次循环。

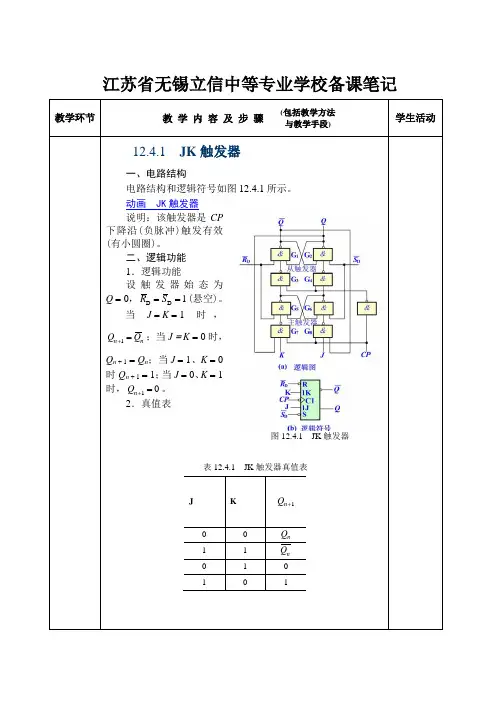

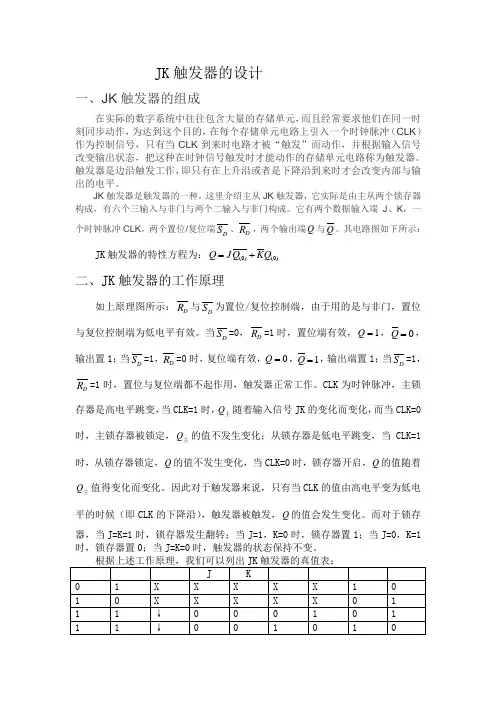

JK 触发器的设计一、JK 触发器的组成在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK )作为控制信号,只有当CLK 到来时电路才被“触发”而动作,并根据输入信号改变输出状态,把这种在时钟信号触发时才能动作的存储单元电路称为触发器。

触发器是边沿触发工作,即只有在上升沿或者是下降沿到来时才会改变内部与输出的电平。

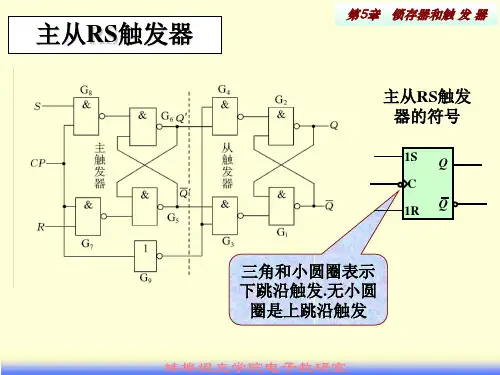

JK 触发器是触发器的一种,这里介绍主从JK 触发器,它实际是由主从两个锁存器构成,有六个三输入与非门与两个二输入与非门构成。

它有两个数据输入端J 、K ,一个时钟脉冲CLK ,两个置位/复位端D S 、D R ,两个输出端Q 与Q 。

其电路图如下所示:JK 触发器的特性方程为:)0()0(Q K Q J Q +=二、JK 触发器的工作原理如上原理图所示:D R 与D S 为置位/复位控制端,由于用的是与非门,置位与复位控制端为低电平有效。

当D S =0,D R =1时,置位端有效,1=Q ,0=Q ,输出置1;当D S =1,D R =0时,复位端有效,0=Q ,1=Q ,输出端置1;当D S =1,D R =1时,置位与复位端都不起作用,触发器正常工作。

CLK 为时钟脉冲,主锁存器是高电平跳变,当CLK=1时,主Q 随着输入信号JK 的变化而变化,而当CLK=0时,主锁存器被锁定,主Q 的值不发生变化;从锁存器是低电平跳变,当CLK=1时,从锁存器锁定,Q 的值不发生变化,当CLK=0时,锁存器开启,Q 的值随着主Q 值得变化而变化。

因此对于触发器来说,只有当CLK 的值由高电平变为低电平的时候(即CLK 的下降沿),触发器被触发,Q 的值会发生变化。

而对于锁存器,当J=K=1时,锁存器发生翻转;当J=1,K=0时,锁存器置1;当J=0,K=1时,锁存器置0;当J=K=0时,触发器的状态保持不变。

74LS90引脚功能及真值表在数字电路中,74LS90 是一种常用的计数器芯片。

了解它的引脚功能和真值表对于正确设计和使用数字电路至关重要。

74LS90 是一款二五十进制异步计数器,它由四个主从 JK 触发器和一些附加门电路组成。

这款芯片具有较为灵活的计数功能,可以实现二进制、五进制和十进制的计数。

先来说说 74LS90 的引脚功能。

它一共有 14 个引脚,分别为:引脚 1 是 CP0,也就是时钟输入 0。

当 CP0 输入脉冲时,芯片内部的二进制计数器会进行计数操作。

引脚 2 是 Q0,是二进制计数器的输出端。

引脚 3 是 Q1,同样是二进制计数器的输出端。

引脚 4 是地(GND),用于芯片的接地连接。

引脚 5 是 CP1,即时钟输入 1。

引脚 6 是 Q2,为五进制计数器的输出端。

引脚 7 是 Q3,也是五进制计数器的输出端。

引脚 8 是电源(VCC),通常连接+5V 电源。

引脚 9 是 R0(1),是复位输入端 1。

引脚 10 是 R0(2),为复位输入端 2。

引脚 11 是 S9(1),是置 9 输入端 1。

引脚 12 是 S9(2),是置 9 输入端 2。

引脚 13 是 Q0',是二进制计数器反相输出端。

引脚 14 是 Q3',是五进制计数器反相输出端。

了解了引脚功能,接下来看看 74LS90 的真值表。

当复位输入端R0(1)和R0(2)同时为“1”时,计数器被复位,Q0、Q1、Q2、Q3 输出均为“0”。

当置 9 输入端 S9(1)和 S9(2)同时为“1”时,计数器被置为“9”,即 Q3、Q2、Q1、Q0 的输出为 1001。

在二进制计数模式下,如果 CP0 输入脉冲,Q0 会按照二进制的规律进行计数,从 0 到 1 变化,Q1 则在 Q0 从 1 变为 0 时发生变化。

在五进制计数模式下,当 CP1 输入脉冲时,Q2 和 Q3 会按照五进制的规律进行计数。

在十进制计数模式下,通过将二进制计数器和五进制计数器级联,可以实现十进制计数。

任务1触发器电路一、实验目的1、掌握D触发器、JK触发器等基本触发电路的原理与设计2、掌握时序电路的分析与设计的方法3、学习VHDL语言中构造体的不同描述方式的异同二、实验内容1、编写VHDL语言源程序,实现D触发器、JK触发器等基本触发电路2、扩展任务:设计其他如RS触发器,并分析它们相互转化的方法3、通过模拟和仿真,分析和验证各种出发器的逻辑功能及其触发方式三、实验要求1、列写D触发器、JK触发器的真值表2、编写实现D触发器、JK触发器功能的VHDL语言程序3、利用实验装置验证程序正确性,分析触发的方式4、写出完整的实验报告(包括上述图表和程序等)四、实验原理说明1、正边沿触发的D触发器的电路符号如图2-4所示。

从输入输出引脚而言,它有一个数据输入端d,一个时钟输入端clk和一个数据输出端q。

D触发器的真值表如表2-2所示。

从表中可以看出:D触发器的输出端只有在正边沿脉冲过后,输入端d的数据才可以被传递到输出端q。

表1D触发器真值表数据输入端时钟输入端clk 数据输出端qdX 0 不变X 1 不变0 - 01 - 12、带复位和置位功能的JK触发器电路符号如图2-5所示。

JK触发器的输入端有置位输s 复位输入clr,控制输入j和k,时钟输入clk;输出端有数据输出q和反向输出qb。

JK触发器的真值表如表2-3所示。

表2-3JK触发器真值表输入端输出端st clr clk j k Q qb0 1 X X X 1 01 0 X X X 0 10 0 X X X X X1 1 - 0 1 0 11 1 - 1 1 翻转翻转1 1 - 0 0 保持保持1 1 - 1 0 1 01 1 0 X X 保持保持编辑本段真值表定义表征逻辑事件输入和输出之间全部可能状态的表格。

真值表列出命题公式真假值的表。

通常以1表示真,0 表示假。

命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。