数字三态门及其应用

- 格式:ppt

- 大小:1.26 MB

- 文档页数:25

【引言】三态门逻辑器件是一种常用于数字电路设计中的重要组件,其能够实现更加复杂的逻辑运算和信号处理。

本文将介绍三态门逻辑器件的基本原理、应用场景以及其在现代电子技术领域中的重要性。

【正文】一、三态门逻辑器件的基本原理三态门逻辑器件是一种具有三个状态的数字逻辑门,它的输出可以处于三种不同的状态:高电平(1)、低电平(0)和高阻态(Z)。

其基本原理是通过控制输入端的使能信号,使输出端的信号能够选择性地连接到高电平、低电平或者高阻态。

二、三态门逻辑器件的种类目前市面上常见的三态门逻辑器件有三态缓冲器(Tri-state Buffer)、三态反相器(Tri-state Inverter)和三态与门(Tri-state AND Gate)等。

它们分别具有不同的功能和特点,根据具体的需求进行选择和应用。

1. 三态缓冲器:三态缓冲器是最常见的三态门逻辑器件之一,其输入端与输出端直接相连。

当使能信号为高电平时,输入信号可以通过三态缓冲器输出;当使能信号为低电平时,三态缓冲器处于高阻态,输出为无效状态。

2. 三态反相器:三态反相器与三态缓冲器类似,不同之处在于其输出端与输入端相反。

当使能信号为高电平时,输入信号经过三态反相器输出的是其反相信号;当使能信号为低电平时,三态反相器处于高阻态,输出为无效状态。

3. 三态与门:三态与门是一种组合逻辑门,其输出信号仅在所有输入信号均为高电平时有效。

当使能信号为高电平时,三态与门的输出信号与输入信号相连;当使能信号为低电平时,三态与门处于高阻态,输出为无效状态。

三、三态门逻辑器件的应用场景三态门逻辑器件在数字电路设计和信号处理中具有广泛的应用场景。

以下列举几个常见的应用场景:1. 总线控制:在计算机系统中,总线是各个模块之间进行数据传输和通信的关键部分。

通过使用三态门逻辑器件,可以实现对总线的控制和管理,提高系统的稳定性和可靠性。

2. 数据选择器:在多路数据选择器设计中,经常需要根据控制信号选择特定的数据输入。

三态门逻辑器件是一种常用的数字电路元件,它可以实现三态输出,即高电平、低电平和高阻态。

在数字电路中,三态门逻辑器件广泛应用于数据选择、数据传输、总线控制等方面。

本文将从以下几个方面对三态门逻辑器件进行介绍。

一、三态门逻辑器件的基本原理三态门逻辑器件通常由一个输入端、一个控制端和一个输出端组成。

其基本原理是利用控制端的信号来控制输出端的状态,当控制端的信号为高电平时,输出端会输出与输入端相同的电平;当控制端的信号为低电平时,输出端会输出与输入端相反的电平;当控制端的信号为高阻态时,输出端处于高阻抗状态,相当于断开了与其他电路的连接。

二、三态门逻辑器件的优点三态门逻辑器件有以下几个优点:1. 可以实现多路数据选择功能。

当控制端的信号为不同的值时,输出端可以选择不同的数据进行输出。

2. 可以实现数据传输功能。

当控制端的信号为高电平时,输入端的数据可以传输到输出端。

3. 可以实现总线控制功能。

当多个设备连接到同一总线时,通过三态门控制输出端的状态,可以实现对总线的控制和管理。

三、三态门逻辑器件的应用三态门逻辑器件在数字电路中有广泛的应用,下面列举几个常见的应用场景:1. 数据选择器:通过控制端的信号,选择不同的数据进行输出。

2. 数据复用器:将多个输入信号复用到一个输出上。

3. 总线控制器:通过控制输出端的状态,实现对总线的控制和管理。

4. 存储器控制器:通过控制输出端的状态,实现对存储器的读写操作。

四、三态门逻辑器件的种类目前主流的三态门逻辑器件有以下几种:1. 74LS244:它是一种8位三态缓冲器,可以实现对8位数据的控制和管理。

2. 74LS245:它是一种8位三态双向缓冲器,可以实现双向数据传输功能。

3. 74LS373:它是一种8位三态锁存器,可以实现对8位数据的存储和控制。

四态门逻辑器件则是在三态门逻辑器件的基础上增加了一个输出状态,即“高阻无效态”,可以实现更多的功能和应用。

五、总结三态门逻辑器件是数字电路中常用的元件之一,它可以实现三态输出,具有多路数据选择、数据传输、总线控制等优点,在数字电路设计中有广泛的应用。

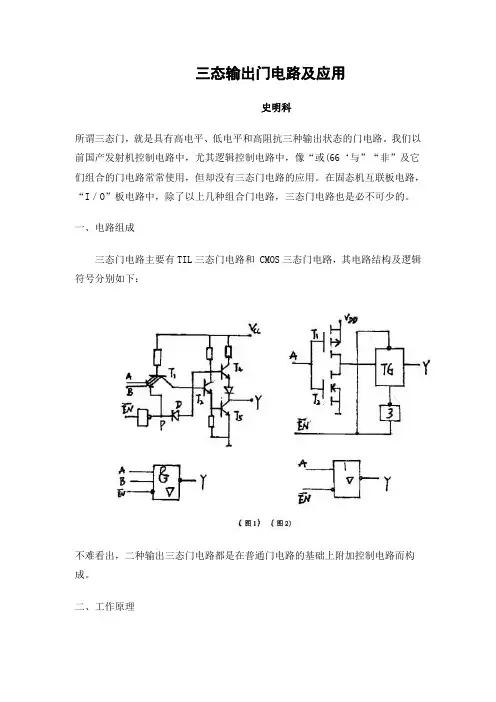

三态输出门电路及应用史明科所谓三态门,就是具有高电平、低电平和高阻抗三种输出状态的门电路。

我们以前国产发射机控制电路中,尤其逻辑控制电路中,像“或(66‘与”“非”及它们组合的门电路常常使用,但却没有三态门电路的应用。

在固态机互联板电路,“I/O”板电路中,除了以上几种组合门电路,三态门电路也是必不可少的。

一、电路组成三态门电路主要有TIL三态门电路和 CMOS三态门电路,其电路结构及逻辑符号分别如下:不难看出,二种输出三态门电路都是在普通门电路的基础上附加控制电路而构成。

二、工作原理(1)TTL三态门电路工作原理图1给出了三态门的电路结构图及图形符号。

其中控制端·EN为低电平时(面=口/,P点为高电平,二极管D截止,电路工作状态和普通的与非门没有区别。

这时Y=·A’B,可能是高电子也可能是低电平,视A、B的状态而定。

而当控制端EN为高电平时(EN=1),P点为低电平,它控制T1发射极,把VBl钳位在1V,使T,、T5载止。

同时二极管D导通,T4的基极电位被钳在1V,使T4载止。

由于T4、T5同时载止,所以输出端呈高阻状态o(2)图2中是将CMOS反相器的输出端同一个模拟开关相串联,即可组成三态门。

图中T,、T2组成反相器,TG和反相器3组成模拟开关,其工作原理是:当控制端电压Ve =1时,由于模拟开关断开,输出端与电源 Vm,输出端与地都相当于开路,故呈现高阻抗状态。

当Ve=OV时,模拟开关闭合,输出电压VY 取决于反相器的输入电压。

若V4= OV,则T1截止,T2导通,VY=VDD,输出高电平;若Va=1,则Tl导通,T2载止,VY=OV,输出低电平。

上述电路中,控制端EN为低电平时与非门处于工作状态,所以该电路为低电平有效同样还有高电平有效控制电路。

三、三态门电路的应用(1)多路信号分时传递在一些复杂的数字系统(象固态机的互联板,U0板等)中,为了减少各个单元电路之间连线的数目,希望能在同一条导线上分时传递若干个门电路的输出信号。

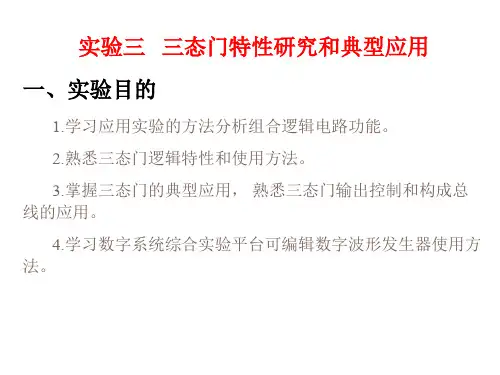

实验三三态门实验三三态门一、实验目的1.熟悉计三态输出门的逻辑功能和使用方法。

2.掌握用三态门构成公共总线的特点和方法。

二、实验器材1.数字逻辑实验箱2.双踪示波器3.与非门74LS00(1片)、三态门74LS125(1片)三、预习要求1.复习三态门有关知识,了解其逻辑功能及管脚。

2.复习三态门实现总线传输的方法。

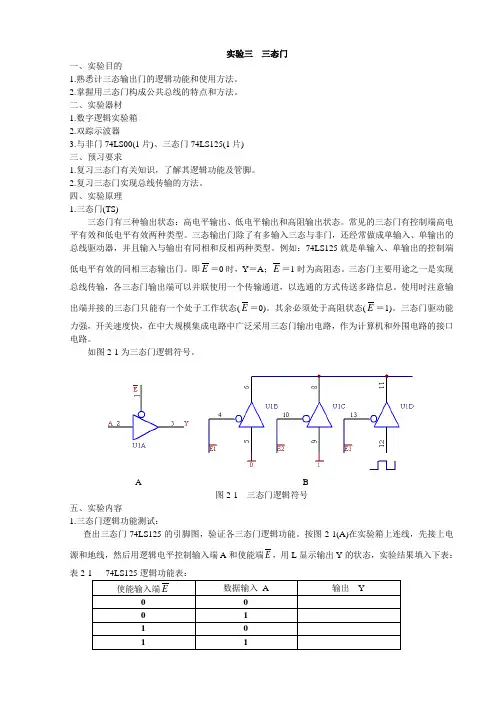

四、实验原理1.三态门(TS)三态门有三种输出状态:高电平输出、低电平输出和高阻输出状态。

常见的三态门有控制端高电平有效和低电平有效两种类型。

三态输出门除了有多输入三态与非门,还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。

例如:74LS125就是单输入、单输出的控制端低电平有效的同相三态输出门。

即E=0时,Y=A;E=1时为高阻态。

三态门主要用途之一是实现总线传输,各三态门输出端可以并联使用一个传输通道,以选通的方式传送多路信息。

使用时注意输出端并接的三态门只能有一个处于工作状态(E=0)。

其余必须处于高阻状态(E=1)。

三态门驱动能力强,开关速度快,在中大规模集成电路中广泛采用三态门输出电路,作为计算机和外围电路的接口电路。

如图2-1为三态门逻辑符号。

AB图2-1三态门逻辑符号五、实验内容1.三态门逻辑功能测试:查出三态门74LS125的引脚图,验证各三态门逻辑功能。

按图2-1(A)在实验箱上连线,先接上电源和地线,然后用逻辑电平控制输入端A和使能端E,用L显示输出Y的状态,实验结果填入下表:表2-174LS125逻辑功能表:使能输入端E0011数据输入A0101输出Y2.用三态门74LS125构成公共总线:要求:用三个三态门构成一条公共总线,参考图21(B)。

使三个输入端状态分别为“0”、“1”、CP,观测公共总线输出状态。

(1)按上述要求画出公共总线的逻辑图。

(2)在实验箱上连线:A1、0(GND),A2、1(Vcc),A3、CP(1KHz或100KHz信号源输出),三个使能端E1??E3分别由三个逻辑开关控制其电平的高低。

实验三三态门一、实验目的1.熟悉计三态输出门的逻辑功能和使用方法。

2.掌握用三态门构成公共总线的特点和方法。

二、实验器材1.数字逻辑实验箱2.双踪示波器3.与非门74LS00(1片)、三态门74LS125(1片)三、预习要求1.复习三态门有关知识,了解其逻辑功能及管脚。

2.复习三态门实现总线传输的方法。

四、实验原理1.三态门(TS)三态门有三种输出状态:高电平输出、低电平输出和高阻输出状态。

常见的三态门有控制端高电平有效和低电平有效两种类型。

三态输出门除了有多输入三态与非门,还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。

例如:74LS125就是单输入、单输出的控制端低电平有效的同相三态输出门。

即E=0时,Y=A;E=1时为高阻态。

三态门主要用途之一是实现总线传输,各三态门输出端可以并联使用一个传输通道,以选通的方式传送多路信息。

使用时注意输出端并接的三态门只能有一个处于工作状态(E=0)。

其余必须处于高阻状态(E=1)。

三态门驱动能力强,开关速度快,在中大规模集成电路中广泛采用三态门输出电路,作为计算机和外围电路的接口电路。

如图2-1为三态门逻辑符号。

A B图2-1 三态门逻辑符号五、实验内容1.三态门逻辑功能测试:查出三态门74LS125的引脚图,验证各三态门逻辑功能。

按图2-1(A)在实验箱上连线,先接上电源和地线,然后用逻辑电平控制输入端A和使能端E,用L显示输出Y的状态,实验结果填入下表:表2-1 74LS125逻辑功能表:2.用三态门74LS125构成公共总线:要求:用三个三态门构成一条公共总线,参考图21(B)。

使三个输入端状态分别为“0”、“1”、CP,观测公共总线输出状态。

(1)按上述要求画出公共总线的逻辑图。

(2)在实验箱上连线:A1、0(GND),A2、1(Vcc),A3、CP(1KHz或100KHz信号源输出),三个使能端E1……E3分别由三个逻辑开关控制其电平的高低。

三态门的逻辑功能

三态门是数字电路中常用的逻辑门之一,具有三种状态:高电平、低电平和高阻态。

它们的逻辑功能在很多应用中都是必不可少的。

首先,三态门可以用来实现数据选择器。

在这种应用中,三态门是一种能够将多个输入信号中的一个输出到一个输出端口的器件。

在数据选择器中,三态门的三种状态代表着不同的输入信号源,它们可以通过控制信号来选择一个信号源输出到输出端口。

其次,三态门可以用来实现毫秒级的延迟。

当需要在数字电路中加入一定的延迟时,三态门可以通过积极和消极的逻辑状态来实现。

通过将三态门的控制信号设置为间歇性的高低电平,可以在输入和输出之间加入一定的延迟。

最后,三态门还可以用来实现电源隔离。

在某些电路中,需要将电路的输入和输出隔离开来以保证安全性。

在这种情况下,三态门可以作为隔离器件来实现电源隔离。

通过控制三态门的控制信号,可以使输入和输出之间隔离开来,从而保证了电路的安全性。

总之,三态门具有多种逻辑功能,可以实现数据选择、延迟、电源隔离等应用。

在数字电路中,三态门是一种重要的器件,其应用极为广泛。

- 1 -。

三态门表现的三种状态三态门是数字电子技术中常用的逻辑门之一,它可以表现三种不同的逻辑状态:低电平、高电平和不确定状态。

在本文中,我们将详细介绍三态门的三种状态及其应用。

第一种状态是低电平。

当输入信号为低电平时,三态门的输出信号也为低电平。

这种状态下,三态门的输出端与地相连,电流可以顺利流通,从而使得输出信号保持低电平。

低电平状态常用于控制电路中的关闭操作,例如开关电源中的电源关闭。

第二种状态是高电平。

当输入信号为高电平时,三态门的输出信号也为高电平。

这种状态下,三态门的输出端与正电源相连,电流可以顺利流通,从而使得输出信号保持高电平。

高电平状态常用于控制电路中的打开操作,例如开关电源中的电源打开。

第三种状态是不确定状态。

当输入信号为无效或不确定信号时,三态门的输出信号将处于不确定状态。

这种状态下,三态门的输出端既不与地相连,也不与正电源相连,电流无法流通,从而使得输出信号的状态不确定。

不确定状态常出现在电路中的故障或异常情况下,需要通过排除故障和修复电路来解决。

三态门作为一种特殊的逻辑门,具有广泛的应用。

其中一个主要的应用是在数据总线中。

数据总线是计算机系统中用于传输数据的一组导线,而三态门可以实现多个设备对同一组数据总线的共享。

当某个设备需要传输数据时,它的输出信号为高电平,从而使得数据总线的状态为高电平;当其他设备不需要传输数据时,它们的输出信号为低电平,从而使得数据总线的状态为低电平。

通过这种方式,多个设备可以共享同一组数据总线,提高了计算机系统的数据传输效率。

三态门还可以用于实现数据选择器和数据缓冲器等功能。

数据选择器是一种多输入、一输出的逻辑电路,它可以根据控制信号选择某一个输入信号作为输出信号。

而数据缓冲器是一种能够放大信号并提供较大输出电流的电路,它可以提高信号的传输能力。

三态门在这些功能电路中起到了重要的作用,能够有效地控制信号的选择和传输。

三态门可以表现三种不同的逻辑状态,即低电平、高电平和不确定状态。

三态门逻辑符号及其意义摘要:一、三态门的基本概念1.三态门的结构2.三态门的分类二、三态门的逻辑符号1.与门、或门、非门的三态符号2.异或门的三态符号3.其他复合逻辑门的三态符号三、三态门的意义与应用1.在数字电路中的作用2.在计算机系统中的运用3.实际应用案例正文:三态门是数字电路中常见的一种逻辑门,它具有三种状态:高电平(H)、低电平(L)和无效电平(Z)。

在三态门中,输入信号和输出信号之间存在一定的逻辑关系,通过不同的输入组合可以得到不同的输出结果。

根据电路结构和功能的差异,三态门可分为多种类型,如与门、或门、非门等。

一、三态门的基本概念1.三态门的结构三态门由多个基本逻辑门组成,如与门、或门、非门等。

通过合理地连接这些基本逻辑门,可以实现三态门的结构。

在实际应用中,为了提高电路的性能和稳定性,通常会采用多个基本逻辑门进行级联。

2.三态门的分类根据输入输出关系,三态门可分为与门、或门、非门等。

此外,还有异或门、数据选择器等复合逻辑门。

下面分别介绍这些常见三态门的逻辑符号及其意义。

二、三态门的逻辑符号1.与门、或门、非门的三态符号与门、或门、非门是数字电路中最基本的逻辑门,它们的三态符号如下:- 与门:当所有输入信号都为高电平时,输出为高电平;其他情况下,输出为低电平。

- 或门:当任意一个输入信号为高电平时,输出为高电平;所有输入信号都为低电平时,输出为低电平。

- 非门:输入信号为高电平时,输出为低电平;输入信号为低电平时,输出为高电平。

2.异或门的三态符号异或门的三态符号如下:- 异或门:当两个输入信号相同时,输出为低电平;当两个输入信号不同时,输出为高电平。

3.其他复合逻辑门的三态符号其他复合逻辑门,如数据选择器、译码器等,它们的逻辑符号根据具体电路结构和功能而定。

三、三态门的意义与应用1.在数字电路中的作用三态门在数字电路中具有重要作用,它可以实现多个数字信号之间的逻辑运算,并将结果输出。

三态门和 OC 门的应用一、实验目的:通过对三态门和 OC门测试,一方面巩固万用表和示波器的操作,另一方面加深对门电路的逻辑功能认识和探索它们的实际应用。

二、实验内容:1.静态测试三态门的逻辑功能与参数的关系2.动态测试三态门的逻辑功能。

完整记录波形图。

3.静态测试OC 门的逻辑功能,总结电阻的 R 作用。

4.用多个三态门构造一个传输门。

5.用两个 OC 门构造一个门控器,正半周输出 100KHz 的脉冲,负半周输出 500KHz 的脉冲。

三、实验步骤:1.三态门 74LS125 的静态测试:用万用表测量三态门的输入输出电压。

列表记录测量结果。

G A Ylogic V(V) logic V(V) logic V(V)0 0 1 3.99 1 3.590 0 0 0 0 0.0831 3.99 1 3.99 高阻 2.471 3.99 0 0 高阻 2.472.测试两输入 OC 与非门 74LS03 的逻辑功能。

说明 OC 门输出端接上拉电阻 R 的作用。

分析 R 值过大或过小,对输出产生的影响。

(1)A logicBlogicYlogic V(V)0 0 高阻 2.470 1 0 0.141 0 高阻 2.471 1 0 0.15(2)上拉电阻:2.5kΩ到7.03kΩ3.三态门 74LS125 的动态测试:给三态门输入端加脉冲信号,用示波器观测输入输出波形。

完整记录波形。

测试电路:周期(us)峰峰值(V)占空比(%)输入400 4 50输出400 4 75 李萨如合成(X-Y)结果:7.用两个 OC 门组成一个门控开关,控制信号用 100KHz 脉冲信号,控制信号的正半周显示 500KHz,负半周显示 1MHz 的脉冲信号。

设计电路的原理图:(因为软件中没有74125元件,所以用7400代替其逻辑)利用QUARTUSⅡ功能模拟电路:波形模拟:实际外部电路连接:实验得到的波形图:信号源:实验箱上的200KHz和1MHz,信号发生器100KHz波形数据:周期(us)峰峰值(v)占空比(%)输入10.4 4 50输出10.4 2.8 50四、实验中遇到的问题1、第一次做出第7题时,遇到很多麻烦,首先是自己给自己找了麻烦,把原理图画成了这个样子:后来发现下面的或门被上面的非门屏蔽掉了(或者说写出方程后,这一项就可以约掉)。

三态门输出高阻态时输出电阻三态门输出高阻态时输出电阻【导言】三态门是数字电路中常见的逻辑门之一,其具备三种输出状态:高电平、低电平和高阻态。

在三态门输出高阻态时,输出电阻的性质成为了我们关注的焦点。

本文将以三态门输出高阻态时输出电阻为主题,深入探讨其原理、性质及应用。

【正文】1. 什么是三态门输出高阻态?三态门是一种具有三种输出状态的数字逻辑门。

在其输入信号为特定条件下,输出会进入高阻态。

高阻态的特点是输出信号处于不确定状态,相当于一个高电阻的状态。

在高阻态下,输出电阻对外电路扮演了重要角色。

2. 高阻态下输出电阻的性质输出电阻是描述输出端对外电路的负载能力的物理量。

在三态门输出高阻态时,输出电阻会呈现出以下性质:(1) 高电阻值:在高阻态下,输出电阻具有较高的电阻值。

这是因为在高阻态时,输出端口与外部电路之间的连接被断开,输出端口相当于一根不导电的电缆,因而产生高电阻。

(2) 模拟信号传输:由于高阻态下的输出电阻较高,三态门在该状态下可以实现对模拟信号的传输。

这一特点在一些特定应用领域中具有重要意义,例如在数据总线中,高阻态的使用可以实现多个设备的数据共享,提高系统的灵活性和效率。

3. 三态门的应用三态门输出高阻态时输出电阻的特性在许多应用领域中得到了广泛的应用。

以下是几个常见的应用示例:(1) 数据总线驱动:在多个设备需要共享数据的场景下,三态门的高阻态可以实现数据的多路切换和并行传输,提高系统的数据传输效率。

(2) 多路选择器:通过控制三态门的高阻态,则可以实现多个输入信号的选择和输出,从而实现多路选择器的功能。

(3) 总线冲突解决:在并行数据传输中,如果同时有多个设备向总线上发送数据,可能会引发总线冲突。

而利用三态门的高阻态,可以通过控制总线上各设备为高阻态或低电平,从而避免总线冲突的发生。

【个人观点】三态门输出高阻态时输出电阻的特性在数字电路设计中具有重要的意义。

高阻态的应用可以实现数据的灵活传输和选择,同时也能够解决总线冲突等问题。

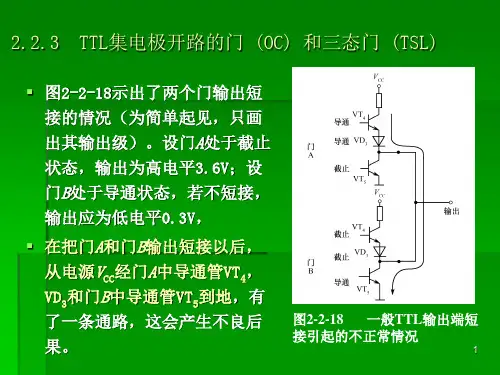

2.2 三态门1.基本原理在数字系统中,常常需要把多个门电路的输出端连接在一起,比如接到数据总线上。

但一般的门电路都只有两个输出状态:输出高电平状态与输出低电平状态。

把这些门电路的输出端连接在一起,在某一个时刻,可能会出现一个以上的门电路的输出同时为高电平状态或者低电平状态,这样就会引起逻辑电平的不确定。

使用三态门可以很好地解决这个问题。

三态门电路有三个输出状态:输出高电平状态、输出低电平状态,以及输出高阻状态。

当三态门电路输出为高阻状态时,三态门的输出端相当于开路,对总线上连接的其它器件没有影响。

我们可以利用三态门的这个优点对需要通过总线的数据进行分时传送,这样数据的传送就不会出现混乱了。

简单的三态门电路如图2.2.1a所示,图2.2.1b是它的代表符号。

其中EN为片选信号输入端,A为数据输入端,L为数据输出端。

图2.2.1 三态门电路(a) 电路图(b) 代表符号当EN=0时,TP2和TN2同时导通,为正常的非门,输出L=-A;当EN=1时,TP2和TN2同时截止,输出为高阻状态。

所以,这是一个低电平有效的三态门。

三态门的真值表如表2.2.1所示。

由真值表可以得出逻辑表达式:当EN=0时,L=-A;当EN=1时,L=Z。

其中Z表示高阻状态。

表2.2.1 三态门的真值表2.实现方案通过FPGA来实现三态门的功能有以下几种方式:(1) 用case语句和if….else语句来实现。

先判断EN是否等于1,如果EN 等于1,则输出端L=Z;如果不等于1,再判断A是否等于0,如果等于0,则输出端L=1,如果不等于0,则输出端L=0。

(2) 用if….else语句来实现。

先判断EN是否等于1,如果EN等于1,则输出端L=Z;如果不等于1,则输出L=~A。

(3) 用“?:”语句来实现,输出端L=EN ? 1’bZ : (~A)。

3.FPGA的实现下面以第三种方案为例来进行FPGA的实现。

(1) 创建工程并设计输入①在E:\project\目录下,新建名为notif的新工程器件族类型(Device Family)选择“Virtex2P”,器件型号(Device)选“XC2VP30 ff896 -7”,综合工具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator(VHDL/Verilog)”。

三态门输出的三种状态在数字电路中,三态门是一种特殊类型的逻辑门。

与其他逻辑门不同的是,三态门可以产生三种不同的输出状态:高电平(1)、低电平(0)和高阻抗状态(Z)。

在本文中,我们将详细介绍三态门的三种输出状态及其应用。

高电平输出(1)当三态门的控制端(通常被标记为使能端)接收到高电平信号时,三态门将产生高电平输出(1)。

在这种状态下,三态门的输出端与输入端之间的电路会形成一条低阻抗路径,从而使得输入信号能够通过三态门并传递到输出端。

这种状态下的三态门可以看作是一个开关,允许信号在电路中传输。

高电平输出状态的三态门常用于电路中的数据传输,例如总线系统中的数据线。

在总线传输中,只有一个设备能够向总线上发送数据,而其他设备则需要将输出设置为高阻抗状态,以避免发生数据冲突。

因此,使用三态门可以有效地控制信号的传输。

低电平输出(0)当三态门的控制端接收到低电平信号时,三态门将产生低电平输出(0)。

与高电平输出状态相反,低电平输出状态下的三态门会将输出端与输入端之间的电路断开,形成一个高阻抗状态。

在这种状态下,输入信号无法通过三态门传递到输出端,输出端相当于与外部断开连接。

低电平输出状态的三态门通常用于电路中的信号拉低操作。

例如,在串行通信中,发送方需要将输出设置为低电平状态,以便在通信线上传输二进制数据的低位。

在接收方接收数据时,输出端的高阻抗状态会使得数据不会受到发送方的输出干扰。

高阻抗状态(Z)当三态门的控制端未接收到任何信号时,三态门将处于高阻抗状态(Z)。

在这种状态下,三态门的输出端与输入端之间的电路断开,形成一个高阻抗路径。

在高阻抗状态下,三态门不对信号进行放大或传递,而是让信号自由通过三态门周围的电路。

高阻抗状态的三态门常用于电路中的总线控制。

例如,在多个设备共享同一条总线的系统中,只有一个设备能够向总线发送数据,其他设备将输出设置为高阻抗状态。

这样做可以避免不同设备之间的数据冲突,并确保总线上的数据传输正常进行。