三态门电路

- 格式:ppt

- 大小:202.00 KB

- 文档页数:3

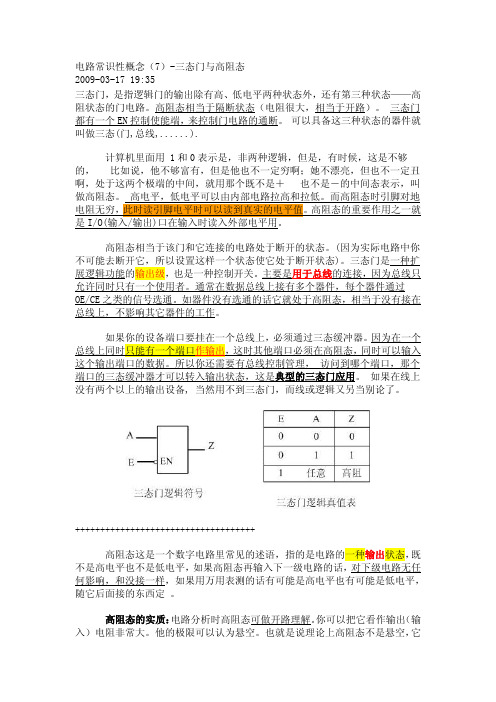

电路常识性概念(7)-三态门与高阻态2009-03-1719:35三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。

高阻态相当于隔断状态(电阻很大,相当于开路)。

三态门都有一个EN控制使能端,来控制门电路的通断。

可以具备这三种状态的器件就叫做三态(门,总线,......).计算机里面用1和0表示是,非两种逻辑,但是,有时候,这是不够的,比如说,他不够富有,但是他也不一定穷啊;她不漂亮,但也不一定丑啊,处于这两个极端的中间,就用那个既不是+也不是―的中间态表示,叫做高阻态。

高电平,低电平可以由内部电路拉高和拉低。

而高阻态时引脚对地电阻无穷,此时读引脚电平时可以读到真实的电平值。

高阻态的重要作用之一就是I/O(输入/输出)口在输入时读入外部电平用。

高阻态相当于该门和它连接的电路处于断开的状态。

(因为实际电路中你不可能去断开它,所以设置这样一个状态使它处于断开状态)。

三态门是一种扩展逻辑功能的输出级,也是一种控制开关。

主要是用于总线的连接,因为总线只允许同时只有一个使用者。

通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。

如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

如果你的设备端口要挂在一个总线上,必须通过三态缓冲器。

因为在一个总线上同时只能有一个端口作输出,这时其他端口必须在高阻态,同时可以输入这个输出端口的数据。

所以你还需要有总线控制管理,访问到哪个端口,那个端口的三态缓冲器才可以转入输出状态,这是典型的三态门应用。

如果在线上没有两个以上的输出设备,当然用不到三态门,而线或逻辑又另当别论了。

++++++++++++++++++++++++++++++++++++高阻态这是一个数字电路里常见的述语,指的是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。

集成门电路功能测试实验报告一实验内容1 三态门的静态逻辑功能测试。

2 动态测试三台门。

并画出三态门的输出特性曲线。

输入为CP矩形波。

3 测试三态门的传输延迟时间。

4 动态测试三态门的电压传输特性曲线。

输入为三角波。

二实验条件硬件基础实验箱,函数信号发生器,双踪示波器,数字万用表,74LS125。

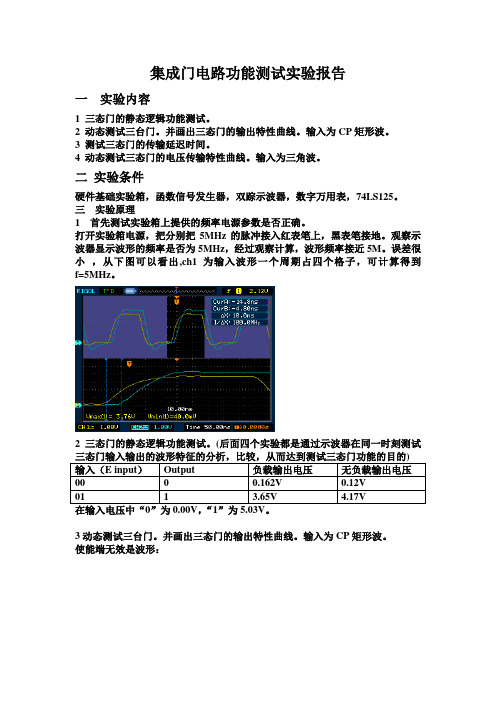

三实验原理1 首先测试实验箱上提供的频率电源参数是否正确。

打开实验箱电源,把分别把5MHz的脉冲接入红表笔上,黑表笔接地。

观察示波器显示波形的频率是否为5MHz,经过观察计算,波形频率接近5M。

误差很小,从下图可以看出,ch1为输入波形一个周期占四个格子,可计算得到f=5MHz。

2 三态门的静态逻辑功能测试。

(后面四个实验都是通过示波器在同一时刻测试3动态测试三台门。

并画出三态门的输出特性曲线。

输入为CP矩形波。

使能端无效是波形:使能端有效时输出波形4 测试三态门的传输延迟时间。

通过测量同一时刻的输入输出波形,可以观察到三态门的输出延迟。

得到波形图为CH1,CH2分别为输入输出波形,可以看出在上升沿的输出延迟为10ns然而下降沿的时候的截图已经丢失了,依稀记得在实验时候,测得是数据下降沿的输出延迟与上升沿的不一致,并且比上升沿的短。

为9.6ns,其传输延迟为两个延迟的平均值9.8ns。

5 测试三态门的电压传输特性曲线。

输入为三角波。

得到输入输出波形为:CH1为输入,CH2为输出。

得到阀值电压为0.92V。

四总结这次实验基本上和上次实验的方法一样,没遇到什么大的问题。

就是还是粗心。

五评价实验效果挺好。

巩固了对逻辑器件的功能测试的方法和操作。

三态门输出的三种状态

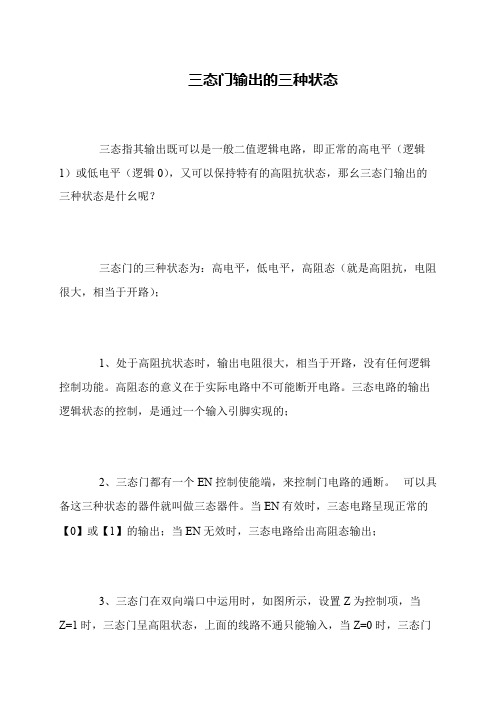

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态,那幺三态门输出的三种状态是什幺呢?

三态门的三种状态为:高电平,低电平,高阻态(就是高阻抗,电阻很大,相当于开路);

1、处于高阻抗状态时,输出电阻很大,相当于开路,没有任何逻辑控制功能。

高阻态的意义在于实际电路中不可能断开电路。

三态电路的输出逻辑状态的控制,是通过一个输入引脚实现的;

2、三态门都有一个EN控制使能端,来控制门电路的通断。

可以具备这三种状态的器件就叫做三态器件。

当EN有效时,三态电路呈现正常的【0】或【1】的输出;当EN无效时,三态电路给出高阻态输出;

3、三态门在双向端口中运用时,如图所示,设置Z为控制项,当

Z=1时,三态门呈高阻状态,上面的线路不通只能输入,当Z=0时,三态门。

三态门电路具有的三种状态一、引言在数字电子电路中,逻辑门是最基本的构建模块。

它们可以接受一个或多个输入并产生一个输出,根据输入和门的类型,输出的值将根据特定的真值表进行计算。

三态门是一种特殊的逻辑门,与传统的逻辑门不同的是,它具有三种状态,分别是低电平状态、高电平状态和高阻态。

本文将深入探讨三态门电路的三种状态及其特性。

二、低电平状态低电平状态是三态门电路的一种状态,此时输入信号并未能够激活门电路的工作。

以下是低电平状态的特点:1.输入信号:在低电平状态下,输入信号为低电平(通常为逻辑0)。

2.输出信号:三态门在低电平状态下,输出信号为低电平。

3.门电路状态:在低电平状态下,门电路处于非激活状态,不进行任何操作。

三、高电平状态高电平状态是三态门电路的另一种状态,此时门电路经过激活,输出信号受到输入信号的控制。

以下是高电平状态的特点:1.输入信号:在高电平状态下,输入信号为高电平(通常为逻辑1)。

2.输出信号:三态门在高电平状态下,输出信号为高电平。

3.门电路状态:在高电平状态下,门电路处于激活状态,进行逻辑运算并将输出信号传递给下一个电路。

四、高阻态高阻态是三态门电路的第三种状态,此时门电路处于一种不决定的状态,既不为低电平也不为高电平。

以下是高阻态的特点:1.输入信号:在高阻态下,输入信号可以是任意电平,电路不对输入信号做任何操作。

2.输出信号:在高阻态下,门电路的输出信号变为高阻态,即输出端变为高阻抗状态,不会对其他电路造成影响。

3.门电路状态:在高阻态下,门电路处于激活状态,但是不进行逻辑运算,也不传递输出信号。

五、三态门的应用三态门由于具有高阻态的特性,因此在许多应用中发挥着重要作用。

以下是三态门的一些常见应用:1.总线传输:在计算机系统中,三态门常用于数据总线的传输。

当多个设备连接到总线时,当某个设备需要传输数据时,它会打开三态门,而其他设备则保持高阻态,以避免冲突。

2.存储器控制:在存储器中,三态门用于控制地址和数据线。

三态门的工作原理三态门(Three-state gate)是一种数字逻辑门,用于在某些情况下控制输出线路的导通或断开。

三态门有三个输出状态,分别为高电平、低电平和高阻抗状态。

高阻抗状态相当于输出开路或断路,因此该状态下的输出端的电压等于输入端的电压,但电流几乎为零。

1.三态门的基本结构三态门由一个基本的逻辑门和一个控制电路组成。

基本的逻辑门通常是一个反相器或一个与非门。

控制电路由一个使能端EN和一个反相器组成,该电路的作用是控制逻辑门的输出状态。

2.三态门的输出控制端使能端EN是三态门的输出控制端,该端口的电平决定了三态门的输出状态。

当EN为高电平(1)时,三态门处于正常工作状态,输出状态取决于输入信号。

如果输入信号为高电平(1),则输出为高电平(1),如果输入信号为低电平(0),则输出为低电平(0)。

当EN为低电平(0)时,三态门处于高阻抗状态,输出相当于开路或断路。

此时,输出端的电压等于输入端的电压,但电流几乎为零。

禁用端和使能端是相互独立的控制端,它们可以在同一个三态门上实现不同的控制作用。

禁用端用于禁止输出,当禁用端为高电平(1)时,三态门处于正常工作状态,当禁用端为低电平(0)时,三态门被禁止输出。

3.三态门的输出状态当EN为高电平(1)时,三态门处于正常工作状态,输出状态取决于输入信号。

如果输入信号为高电平(1),则输出为高电平(1),如果输入信号为低电平(0),则输出为低电平(0)。

当EN为低电平(0)时,三态门处于高阻抗状态,输出相当于开路或断路。

此时,输出端的电压等于输入端的电压,但电流几乎为零。

4.三态门的应用三态门在计算机和数字系统中被广泛应用。

例如,在计算机的总线结构中,多个三态门可以连接在同一条总线线上,当某些三态门需要向总线传输数据时,可以通过控制使能端使其处于正常工作状态,而其他不需要传输数据的三态门可以使能端处于高阻抗状态,从而避免总线冲突。

此外,三态门还可以用于实现逻辑电路的复杂组合,例如实现具有“或”和“与”逻辑功能的组合电路。

![三态门_数字逻辑电路基础_[共2页]](https://img.taocdn.com/s1/m/3ca371e85727a5e9846a61c3.png)

55 第2章 门电路和集成逻辑门V CC 上串接的电阻R L 的数值不能选得过大,其最大值应按照下式选择。

CCOH L((max)OH IHV U R nI mI =+- (2.1) 在式(2.1)中,I OH 是每个OC 门输出三极管截止时的灌电流,I IH 是负载门每个输入端的高电平输入电流。

当“线与”的OC 门中只有一个导通时,负载电流将全部流入导通的那个OC 门,因此R L 的数值又不能选得过小,以确保流入导通OC 门的电流不至超过最大允许的负载电流I LM 。

R L 最小值应按照下式选择。

CC OL L((min)LM IL'V U R I m I −=− (2.2) 在式(2.2)中,U OL 是规定的输出低电平,m ′是负载门的个数,I IL 是每个负载门输入端的低电平输入电流。

(如果负载门为或非门,则m ′是输入端数。

)最后选定的R L 电阻数值应介于上述两个公式规定的最大值和最小值之间。

除了与非门和反相器以外,与门、或门、或非门等都可以做成集电极开路的输出结构,而且外接负载电阻的计算方法与上述方法相同。

2.3.4 三态门三态门简称作TSL (tristatelogic )门,是在普通逻辑门的基础上,加上使能控制信号和控制电路构成的。

其电路如图2.21所示。

图2.21 三态门输出的电路图和图符号图腾结构的TTL 与非门有两个输出状态,即逻辑0或逻辑1,这两个状态都是低阻输出。

三态门除具有这两个状态外,还有高阻输出的第三种状态。

图2.21(a )为三态输出的TTL 与非门电路。

可以看出,三态门是在普通TTL 与非门电路的基础上增加一个带有控制端EN 的控制电路。

由一级反相器和一个钳位二极管构成的控制电路为低电平有效;由两级反相器和一个钳位二极管构成的控制电路为高电平有效。

当控制端起作用时,三态门处高阻状态,其输出端相当于和其他电路断开。

三态门的逻辑图符号如图2.21(b )和图2.21(c )所示。

三态门的逻辑功能

三态门是数字电路中常用的逻辑门之一,具有三种状态:高电平、低电平和高阻态。

它们的逻辑功能在很多应用中都是必不可少的。

首先,三态门可以用来实现数据选择器。

在这种应用中,三态门是一种能够将多个输入信号中的一个输出到一个输出端口的器件。

在数据选择器中,三态门的三种状态代表着不同的输入信号源,它们可以通过控制信号来选择一个信号源输出到输出端口。

其次,三态门可以用来实现毫秒级的延迟。

当需要在数字电路中加入一定的延迟时,三态门可以通过积极和消极的逻辑状态来实现。

通过将三态门的控制信号设置为间歇性的高低电平,可以在输入和输出之间加入一定的延迟。

最后,三态门还可以用来实现电源隔离。

在某些电路中,需要将电路的输入和输出隔离开来以保证安全性。

在这种情况下,三态门可以作为隔离器件来实现电源隔离。

通过控制三态门的控制信号,可以使输入和输出之间隔离开来,从而保证了电路的安全性。

总之,三态门具有多种逻辑功能,可以实现数据选择、延迟、电源隔离等应用。

在数字电路中,三态门是一种重要的器件,其应用极为广泛。

- 1 -。

三态门mos电路

三态门(MOS电路)是一种常用的数字逻辑门电路,由金属氧化物半导体场效应管(MOS管)构成。

它可以实现与门、或门、非门等逻辑功能,被广泛应用于数字电路设计中。

三态门的核心是MOS管的三种工作状态:导通状态、截止状态和高阻态。

在导通状态下,MOS管的导通电阻很小,电流可以通过。

而在截止状态下,MOS管的导通电阻很大,电流无法通过。

高阻态是一种特殊的状态,当输入信号为高电平时,MOS管进入高阻态,输出端的电压不受控制,即高阻态是一种无输出状态。

三态门的工作原理可以通过一个简单的例子来说明。

假设有两个输入信号A和B,输出信号为Y。

当A为低电平、B为高电平时,MOS管处于截止状态,输出信号Y为低电平。

当A为高电平、B为低电平时,MOS管也处于截止状态,输出信号Y仍为低电平。

而当A和B均为高电平时,MOS管进入高阻态,输出信号Y为高阻态,即无输出。

通过这种方式,三态门可以实现多种逻辑功能的实现。

三态门在数字电路设计中具有重要的作用。

它可以实现数据的选择、存储和传输等功能,广泛应用于计算机存储器、总线控制和输入输出接口等领域。

三态门的设计和优化对于提高数字电路的性能和可靠性具有重要意义。

三态门是一种常用的数字逻辑门电路,通过MOS管的不同工作状态

实现逻辑功能的实现。

它在数字电路设计中具有广泛的应用,是提高数字电路性能和可靠性的重要手段之一。

通过合理的设计和优化,可以充分发挥三态门的作用,实现更复杂的数字电路功能。

电路常识性概念之——三态门与高阻态的概念及应用我们都知道,三态门是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。

高阻态相当于隔断状态(电阻很大,相当于开路)。

三态门都有一个EN控制使能端,来控制门电路的通断。

可以具备这三种状态的器件就叫做三态门。

计算机里面用1和0表示是,非两种逻辑,但是有时候这是不够的。

比如说,他不够富有但是他也不一定穷啊;她不漂亮但也不一定丑啊,处于这两个极端的中间,就用那个既不是+也不是―的中间态表示,叫做高阻态。

高电平,低电平可以由内部电路拉高和拉低。

而高阻态时引脚对地电阻无穷,此时读引脚电平时可以读到真实的电平值。

高阻态的重要作用之一就是I/O(输入/输出)口在输入时读入外部电平用。

高阻态相当于该门和它连接的电路处于断开的状态。

(因为实际电路中你不可能去断开它,所以设置这样一个状态使它处于断开状态)。

三态门是一种扩展逻辑功能的输出级,也是一种控制开关。

主要是用于总线的连接,因为总线只允许同时只有一个使用者。

通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。

如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

如果你的设备端口要挂在一个总线上,必须通过三态缓冲器。

因为在一个总线上同时只能有一个端口作输出,这时其他端口必须在高阻态,同时可以输入这个输出端口的数据。

所以你还需要有总线控制管理,访问到哪个端口,那个端口的三态缓冲器才可以转入输出状态,这是典型的三态门应用。

如果在线上没有两个以上的输出设备, 当然用不到三态门,而线或逻辑又另当别论了。