三态输出电路

- 格式:doc

- 大小:31.00 KB

- 文档页数:2

三态输出八位双向收发器电路设计罗晟;欧阳雪【摘要】文章介绍了一款全定制三态输出八位双向收发器电路的设计过程,包括电路的原理分析、逻辑设计、电路仿真及版图设计。

该电路的设计采用了全定制正向设计流程,选用了0.6μmCMOS工艺流片。

根据电路的应用场合和应用要求,其具有高速、大驱动的特点。

电路工作电源为5V,输入电平为TTL兼容,输出驱动为高电平12mA,低电平48mA,输入输出间延时为1.5ns~7.5ns。

芯片功能和参数通过仿真和验证确认,经流片封装测试后,均满足设计要求。

%The paper describes the design flow of a octal bidirectional transceiver withTRI-STATE outputs, including the transceiver's theory, logic design, simulation and the layout design. The transceiver's design is based onthe full custom design flow and 0.6μm CMOS techn ology. The circuit is high speed and high drive. The working voltage is 5V, TTL level input. Output high current is 12mA, low current is 48mA, input to output delay is 1.5ns -7.5ns. The transceiver met all of the parameters.【期刊名称】《电子与封装》【年(卷),期】2012(012)006【总页数】2页(P16-17)【关键词】双向收发器;输出三态;全定制设计【作者】罗晟;欧阳雪【作者单位】中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035【正文语种】中文【中图分类】TN4021 设计要求与原理本文介绍了一款全定制三态输出八位双向收发器电路的设计过程,包括电路的原理分析、逻辑设计、电路仿真及版图设计。

三态门高阻态输出电压-概述说明以及解释1.引言1.1 概述引言部分是一篇长文的开端,通常用来向读者介绍文章的背景和目的。

在本文中,引言部分的1.1小节是关于文章概述的内容,下面是一个可能的写作示例:概述部分旨在为读者提供关于本文主题的整体认识。

本文将探讨三态门高阻态输出电压的相关概念和特性。

在现代电子技术的发展中,三态门作为一种重要的逻辑门电路,在数字电路设计中扮演着重要角色。

同时,高阻态输出电压具有独特的特性和应用,为数字电路的设计和功能增加了更多的灵活性。

在本文的后续部分,我们将首先介绍三态门的基本定义和工作原理,重点探讨其在数字电路中的功能和应用。

随后,我们将进一步讨论高阻态输出电压在电路设计中的特点和优势,以及其在通信、嵌入式系统、存储器等领域的实际应用。

通过详细的分析和实例展示,本文旨在深入阐述三态门高阻态输出电压的相关概念和特性,以期为读者提供对此技术的全面理解和应用指导。

在掌握了这些基础知识之后,读者将能够更好地应用三态门和高阻态输出电压的特性,为数字电路设计提供更多的可能性和创新思路。

在接下来的章节中,我们将逐步展开对三态门和高阻态输出电压的详细讨论,并结合具体实例,深入剖析它们的作用和应用领域。

希望本文能够激发读者的思考,并为读者在实际工作和学习中提供有益的指导和启迪。

文章结构部分的内容可以写作如下:1.2 文章结构本文共包含三个主要部分:引言、正文和结论。

引言部分将对整篇文章进行概述,包括三态门高阻态输出电压的背景和重要性。

同时,会介绍文章结构以及本文的目的。

正文部分将详细探讨三态门的定义和高阻态输出电压的特点。

首先,会对三态门的基本概念进行介绍,包括其作用和原理。

其次,会重点讨论高阻态输出电压的特点,如其电压范围、输出特性等。

此外,为了更好地理解高阻态输出电压,可能还会介绍相关的实验和实例。

结论部分将对整篇文章进行总结,并提出对三态门作用的归纳和探讨高阻态输出电压的应用。

通过总结文章的主要观点和论证内容,可以再次强调三态门和高阻态输出电压的重要性,并提出对未来研究和应用的展望。

《数字电路与逻辑设计》仿真实验报告仿真实验1 三态输出门实现总线传输1. 仿真实验内容试用74LS125三态输出门和3-8译码器74LS138(或其它门电路),实现4路十进制数(BCD 码)的循环显示,4路显示数字可自行设定,显示效果如图1所示。

图1 仿真实验效果图总线传输4路十进制(BCD 码)信号示意图如图2所示。

总线输出图2 总线传输多路信号示意图2. 仿真实验电路设计(1)设计原理十进制数以二进制码表示需要4位,所以需要4根总线。

以四路1位数据总线为例,其原理电路如图3所示。

74LS125三态输出门的控制端为低电平有效,如EN 1’=0,EN 2’ =EN 3’ =EN 4’=1,则数据A 12传到总线上,而其余的3个三态门处于高阻状态;以此类推,若各门的控制端轮流处于低电平,其余3个控制端处于高电平,则可实现4路数据的总线传输。

可以用3-8译码器74LS138的四个输出信号Y 0’~ Y 3’作为控制信号,仿真时可以用仿真软件的字发生器从00~11循环产生,从而实现4个控制信号的自动循环有效。

总线输出图3 四路1位数据总线原理电路D 41D 31D 21D 11EN 4'EN 3'EN 2'1+VccA 1A 0 (2)仿真实验电路根据以上设计原理,设计的仿真实验电路如图4所示。

图4 仿真实验电路4. 仿真实验结果及分析(1)当字发生器输出为00时,总线数据为A12 A13A14 A15 =0010,数码管显示2,和设置的传输数据1一致,仿真实验结果如图5所示。

图5 仿真实验结果(2)当字发生器输出为01时,总线数据为A12 A13A14 A15 =0101,数码管显示5,与设置的传输数据一致,仿真实验结果如图6所示。

图6 仿真实验结果(3)当字发生器输出为10时,总线数据为A12 A13A14 A15 =0110,数码管显示6,与设置的传输数据一致,仿真实验结果如图7所示。

三态门逻辑器件是一种常用的数字电路元件,它可以实现三态输出,即高电平、低电平和高阻态。

在数字电路中,三态门逻辑器件广泛应用于数据选择、数据传输、总线控制等方面。

本文将从以下几个方面对三态门逻辑器件进行介绍。

一、三态门逻辑器件的基本原理三态门逻辑器件通常由一个输入端、一个控制端和一个输出端组成。

其基本原理是利用控制端的信号来控制输出端的状态,当控制端的信号为高电平时,输出端会输出与输入端相同的电平;当控制端的信号为低电平时,输出端会输出与输入端相反的电平;当控制端的信号为高阻态时,输出端处于高阻抗状态,相当于断开了与其他电路的连接。

二、三态门逻辑器件的优点三态门逻辑器件有以下几个优点:1. 可以实现多路数据选择功能。

当控制端的信号为不同的值时,输出端可以选择不同的数据进行输出。

2. 可以实现数据传输功能。

当控制端的信号为高电平时,输入端的数据可以传输到输出端。

3. 可以实现总线控制功能。

当多个设备连接到同一总线时,通过三态门控制输出端的状态,可以实现对总线的控制和管理。

三、三态门逻辑器件的应用三态门逻辑器件在数字电路中有广泛的应用,下面列举几个常见的应用场景:1. 数据选择器:通过控制端的信号,选择不同的数据进行输出。

2. 数据复用器:将多个输入信号复用到一个输出上。

3. 总线控制器:通过控制输出端的状态,实现对总线的控制和管理。

4. 存储器控制器:通过控制输出端的状态,实现对存储器的读写操作。

四、三态门逻辑器件的种类目前主流的三态门逻辑器件有以下几种:1. 74LS244:它是一种8位三态缓冲器,可以实现对8位数据的控制和管理。

2. 74LS245:它是一种8位三态双向缓冲器,可以实现双向数据传输功能。

3. 74LS373:它是一种8位三态锁存器,可以实现对8位数据的存储和控制。

四态门逻辑器件则是在三态门逻辑器件的基础上增加了一个输出状态,即“高阻无效态”,可以实现更多的功能和应用。

五、总结三态门逻辑器件是数字电路中常用的元件之一,它可以实现三态输出,具有多路数据选择、数据传输、总线控制等优点,在数字电路设计中有广泛的应用。

三态输出触发器和锁存器实验报告有数据1. 理解三态输出触发器和锁存器的工作原理;2. 掌握三态输出触发器和锁存器的实验方法;3. 熟悉使用示波器进行实验测量和数据分析。

实验器材:- 简易逻辑实验箱- 三态输出触发器芯片(例如74LS373)- 锁存器芯片(例如74LS175)- 计时器芯片(例如555)- 示波器- 电源和电线等其他辅助器材实验原理:1. 三态输出触发器(Tri-state Output Flip-Flop):三态输出触发器是一种特殊的双稳态触发器,其输出可以处于三种状态之一: 高电平、低电平和高阻态(High-Z)。

利用一个使能端(Enable)来控制输出状态,当使能端为低电平时,输出处于高阻态,此时输出不受触发器的状态控制;当使能端为高电平时,输出由触发器的状态决定。

74LS373是一种广泛使用的三态输出触发器芯片,其引脚功能如下(以16位为例):- D0 ~ D15: 数据输入端,用于输入要存储的数据;- OE:输出使能端,用于控制输出状态;- LE:锁存使能端,用于控制存储操作;- Q0 ~ Q15: 输出端,输出存储的数据。

实验中,我们将通过控制OE和LE端的电平来实现三态输出触发器的控制和数据存储。

2. 锁存器(Latch):锁存器是一种具有存储功能的触发器,可以通过控制使能端来实现数据的锁存和释放。

常见的锁存器有SR锁存器和D锁存器等。

74LS175是一种广泛使用的锁存器芯片,其引脚功能如下(以四位为例):- D0 ~ D3: 数据输入端,用于输入要存储的数据;- EN: 使能端,用于控制存储操作;- Q0 ~ Q3: 输出端,输出存储的数据。

实验中,我们将通过控制EN端的电平来实现锁存器的控制和数据存储。

实验步骤:实验一: 三态输出触发器实验1. 连接电路: 将74LS373芯片插入实验箱中,并按照引脚功能连接电路,包括数据输入端、输出端、输出使能端和锁存使能端等。

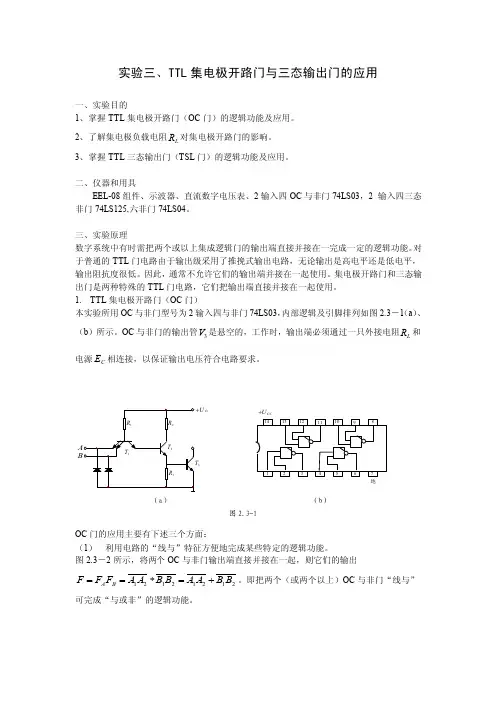

实验三、TTL集电极开路门与三态输出门的应用一、实验目的1、掌握TTL集电极开路门(OC门)的逻辑功能及应用。

R对集电极开路门的影响。

2、了解集电极负载电阻L3、掌握TTL三态输出门(TSL门)的逻辑功能及应用。

二、仪器和用具OL iH I —负载门高电平输入电流(<50uA ) iL I —负载门低电平输入电流(<1.6mA )C E —L R 外接电源电压n —OC 门个数 N —负载门个数m —接入电路的负载门输入端总个数L R 值须小于max L R ,否则OH U 将下降,L R 值须大于min L R ,否则L R OL U 将上升,又由于LR 的大小会影响输出波形的边沿时间,在工作速度较高时,L R 应尽量选取接近min L R . 2. TTL 三态输出门(TSL 门)TTL 三态输出门是一种特殊的门电路,它与普通的TTL 门电路结构不同,它的输出端除了通常的高电平、低电平两种状态外(这两种状态均为低阻状态),还有第三种输出状态—高阻状态,处于高阻状态时,电路与负载之间相当于开路。

图2.3-4是三态输出四总线缓冲器的逻辑符号,它有一个控制端(又称禁止端或使能端)E ,E =0为正常工作状态,实现Y=A 的逻辑功能;E =1为禁止状态,输出Y 呈高阻状态。

这种在控制端加低电平电路才能正常工作的工作方式称低电平使能。

三态输出门按逻辑功能及控制方式分有各种不同的类型,在实验中所用的三态门的型号是74LS125,引脚图如图2.3-5所示。

三态电路主要用途之一是实现总线传输,即用一个传输通道以选通方式传送多路信息。

图3-6所示,电路把若干个三态TTL 电路输出端直接连接在一起构成三态门总线,使用时,要求只有需要传输信息的三态控制端处于使能态,其余各门都处于禁止状态。

四、实验内容1. TTL 集电极开路与非门74LS03负载电阻L R 的确定用两个集电极开路与非门“线与”使用驱动一个TTL 非门,负载电阻由一个200Ω电阻和一个470k Ω电位器串接而成,取C E =5V ,OH U =3.6V ,OL U =0.3V ,OL U 按图3-7连接实验电路,接通电源,用逻辑开关改变两个OC 门的输入状态,先使OC 门“线与”输出高电平,调节P R 使OH U =3.5V ,测得此时的L R 即为max L R ,再使电路输出低电平用两个集电极开路与非门“线与”使用驱动一个TTL 非门,负载电阻由一个200Ω电阻和一个470k Ω电位器串接而成,取C E =5V ,OH U =3.6V ,OL U =0.3V ,OL U 按图3-7连接实验345TitleNum berSize B Date:13-Dec-2003File :F:\T UXIN G\ZSW.ddbYA123443211413121110981234567E3CCU +A 1E1地Y1E2A 2Y2Y3Y4E4A3A4图2.3-4 图2.3-5E321DCBA1413121110981234567ABCD6543TitleNum ber RevisionSize 数 据 总 线nA nE 1E CCU +1A 2A .. .2E 地图2.3-6 图2.3-774LS 04电路,接通电源,用逻辑开关改变两个OC 门的输入状态,先使OC 门“线与”输出高电平,调节P R 使OH U =3.5V ,测得此时的L R 即为max L R ,再使电路输出低电平OL U =0.3V ,测得此时的L R 即为min L R ,图2.3-8所示。

三态门输出高阻态时输出电阻这里是写手为你撰写的文章:【主题】三态门输出高阻态时输出电阻1. 引言三态门是数字电路中常见的一种逻辑门,其在不同输入情况下能够产生三种不同的输出状态:高电平、低电平和高阻态。

本文将以三态门输出高阻态时的电阻作为主题,深入探讨其在数字电路中的广泛应用和重要作用。

2. 三态门基本原理三态门是一种特殊的逻辑门,其输出端具有三种状态:输出高电平、输出低电平和高阻态。

当三态门处于高阻态时,它的输出端相当于一个高阻抗的电路。

这种特性使得三态门在数字电路中扮演着重要的角色,能够灵活地控制信号的传输和处理。

3. 三态门输出高阻态的应用在数字电路设计中,三态门的高阻态输出具有广泛的应用。

它可以用于构建数据总线、实现多路复用器和解复用器、控制信号的传输和选择,以及实现电路的抗干扰和隔离等功能。

在大规模集成电路中,三态门的高阻态输出能够有效地减少电路的功耗和提高系统的可靠性,因此被广泛应用于存储器、总线和控制电路等领域。

4. 输出电阻的影响因素三态门在高阻态下的输出电阻是影响其性能的重要指标之一。

输出电阻的大小受到多种因素的影响,包括器件参数、工作状态、温度等。

在实际应用中,需要合理选型和设计,以确保三态门在高阻态下具有合适的输出电阻,满足电路的要求。

5. 个人观点和理解在我的观点和理解中,三态门输出高阻态时的输出电阻对于数字电路的性能和可靠性具有重要影响。

合理设计和应用三态门,控制其高阻态时输出电阻的大小,能够有效提高数字电路的工作效率和稳定性,同时降低功耗和信号失真。

在实际工程中,需要充分考虑三态门的高阻态输出特性,以确保电路的正常运行和可靠传输。

6. 总结本文对三态门输出高阻态时的输出电阻进行了全面的评估和探讨。

通过深入分析其基本原理、应用领域和输出电阻的影响因素,希望能够加深读者对该主题的理解和认识。

在未来的工程设计中,可以根据本文提供的思路和方法,更好地应用和优化三态门的高阻态输出特性,提升数字电路的性能和可靠性。

三态门工作原理

三态门工作原理是通过控制输入端和输出端的电压拉高或拉低来实现逻辑电路的功能。

其中,输入端有两个信号输入端A 和B,输出端为一个信号输出端Y。

三态门有三种状态:高电平、低电平和高阻态。

在高电平状态下,当输入端A和输入端B都为高电平时,输出端Y为高电平;当输入端A和输入端B中只要有一个为低电平时,输出端Y保持高电平状态。

在低电平状态下,无论输入端A和输入端B是什么电平,输出端Y都为低电平。

在高阻态下,输出端Y与输入端A和输入端B之间并没有连接,此时输出端Y的电平与之前的状态无关。

三态门的工作原理是通过使输出端Y能够在高电平、低电平和高阻态之间进行切换,从而实现对逻辑电路的控制。

当需要输出信号时,输入端A和输入端B的电平决定了输出端Y的电平;当不需要输出信号时,可以将输出端Y置于高阻态,使其与其他电路断开连接,以防止干扰。

三态门常用于多路选择器、存储器等电路中,可以有效地控制信号的传输和切换,提高电路的灵活性和可靠性。

三态输入逻辑电路(原创实用版)目录1.引言2.三态逻辑电路的定义和特点3.三态逻辑电路的输入和输出4.三态逻辑电路的应用5.结论正文1.引言在数字电路中,逻辑门电路和组合逻辑电路是常见的电路类型。

然而,有一种名为三态逻辑电路的电路类型,它不仅具有逻辑门电路和组合逻辑电路的功能,还具有更多的特性。

本文将对三态逻辑电路进行介绍,包括其定义、特点、输入和输出以及应用等方面。

2.三态逻辑电路的定义和特点三态逻辑电路,又称为三态门电路,是一种特殊的逻辑电路,具有三种状态:高电平、低电平和无效。

一般情况下,逻辑电路只有两种状态:高电平和低电平。

三态逻辑电路的这种特性使得它在某些应用场景中具有独特的优势。

3.三态逻辑电路的输入和输出三态逻辑电路的输入和输出都可以是高电平、低电平或者无效。

当输入为高电平时,输出可以是高电平、低电平或者无效;当输入为低电平时,输出可以是高电平、低电平或者无效;当输入为无效时,输出可以是高电平、低电平或者无效。

这种特性使得三态逻辑电路在应对不确定的输入信号时具有更好的稳定性。

4.三态逻辑电路的应用由于三态逻辑电路具有三种状态以及输入和输出的不确定性,它在实际应用中具有广泛的应用前景。

例如,在计算机系统中,三态逻辑电路可以用于控制数据的传输,防止数据丢失或者错误;在通信系统中,三态逻辑电路可以用于控制信号的传输,提高信号的可靠性;在模拟电路中,三态逻辑电路可以用于模拟信号的处理,提高信号的精度等。

5.结论综上所述,三态逻辑电路是一种具有特殊特性的逻辑电路,具有三种状态和输入输出的不确定性。

这种特性使得三态逻辑电路在实际应用中具有广泛的应用前景,可以用于控制数据和信号的传输,提高系统的可靠性和精度。

三态门输出高阻态时输出电阻三态门输出高阻态时输出电阻【导言】三态门是数字电路中常见的逻辑门之一,其具备三种输出状态:高电平、低电平和高阻态。

在三态门输出高阻态时,输出电阻的性质成为了我们关注的焦点。

本文将以三态门输出高阻态时输出电阻为主题,深入探讨其原理、性质及应用。

【正文】1. 什么是三态门输出高阻态?三态门是一种具有三种输出状态的数字逻辑门。

在其输入信号为特定条件下,输出会进入高阻态。

高阻态的特点是输出信号处于不确定状态,相当于一个高电阻的状态。

在高阻态下,输出电阻对外电路扮演了重要角色。

2. 高阻态下输出电阻的性质输出电阻是描述输出端对外电路的负载能力的物理量。

在三态门输出高阻态时,输出电阻会呈现出以下性质:(1) 高电阻值:在高阻态下,输出电阻具有较高的电阻值。

这是因为在高阻态时,输出端口与外部电路之间的连接被断开,输出端口相当于一根不导电的电缆,因而产生高电阻。

(2) 模拟信号传输:由于高阻态下的输出电阻较高,三态门在该状态下可以实现对模拟信号的传输。

这一特点在一些特定应用领域中具有重要意义,例如在数据总线中,高阻态的使用可以实现多个设备的数据共享,提高系统的灵活性和效率。

3. 三态门的应用三态门输出高阻态时输出电阻的特性在许多应用领域中得到了广泛的应用。

以下是几个常见的应用示例:(1) 数据总线驱动:在多个设备需要共享数据的场景下,三态门的高阻态可以实现数据的多路切换和并行传输,提高系统的数据传输效率。

(2) 多路选择器:通过控制三态门的高阻态,则可以实现多个输入信号的选择和输出,从而实现多路选择器的功能。

(3) 总线冲突解决:在并行数据传输中,如果同时有多个设备向总线上发送数据,可能会引发总线冲突。

而利用三态门的高阻态,可以通过控制总线上各设备为高阻态或低电平,从而避免总线冲突的发生。

【个人观点】三态门输出高阻态时输出电阻的特性在数字电路设计中具有重要的意义。

高阻态的应用可以实现数据的灵活传输和选择,同时也能够解决总线冲突等问题。

2.2 三态门1.基本原理在数字系统中,常常需要把多个门电路的输出端连接在一起,比如接到数据总线上。

但一般的门电路都只有两个输出状态:输出高电平状态与输出低电平状态。

把这些门电路的输出端连接在一起,在某一个时刻,可能会出现一个以上的门电路的输出同时为高电平状态或者低电平状态,这样就会引起逻辑电平的不确定。

使用三态门可以很好地解决这个问题。

三态门电路有三个输出状态:输出高电平状态、输出低电平状态,以及输出高阻状态。

当三态门电路输出为高阻状态时,三态门的输出端相当于开路,对总线上连接的其它器件没有影响。

我们可以利用三态门的这个优点对需要通过总线的数据进行分时传送,这样数据的传送就不会出现混乱了。

简单的三态门电路如图2.2.1a所示,图2.2.1b是它的代表符号。

其中EN为片选信号输入端,A为数据输入端,L为数据输出端。

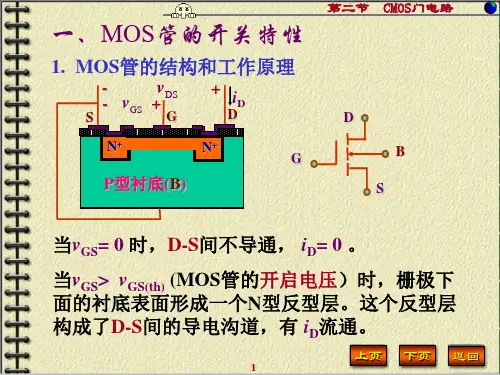

图2.2.1 三态门电路(a) 电路图(b) 代表符号当EN=0时,TP2和TN2同时导通,为正常的非门,输出L=-A;当EN=1时,TP2和TN2同时截止,输出为高阻状态。

所以,这是一个低电平有效的三态门。

三态门的真值表如表2.2.1所示。

由真值表可以得出逻辑表达式:当EN=0时,L=-A;当EN=1时,L=Z。

其中Z表示高阻状态。

表2.2.1 三态门的真值表2.实现方案通过FPGA来实现三态门的功能有以下几种方式:(1) 用case语句和if….else语句来实现。

先判断EN是否等于1,如果EN 等于1,则输出端L=Z;如果不等于1,再判断A是否等于0,如果等于0,则输出端L=1,如果不等于0,则输出端L=0。

(2) 用if….else语句来实现。

先判断EN是否等于1,如果EN等于1,则输出端L=Z;如果不等于1,则输出L=~A。

(3) 用“?:”语句来实现,输出端L=EN ? 1’bZ : (~A)。

3.FPGA的实现下面以第三种方案为例来进行FPGA的实现。

(1) 创建工程并设计输入①在E:\project\目录下,新建名为notif的新工程器件族类型(Device Family)选择“Virtex2P”,器件型号(Device)选“XC2VP30 ff896 -7”,综合工具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator(VHDL/Verilog)”。

三态与非门原理三态与非门原理是数字逻辑电路中常用的两种基本逻辑门。

他们的应用广泛,不仅在计算机领域,也在其他电子设备中得到了广泛的应用。

下面将详细介绍三态与非门原理的工作原理和应用。

三态门是一种具有三种输出状态的逻辑门,它的输出可以是高电平、低电平或高阻态。

三态门的一个典型应用是在总线系统中。

在总线系统中,多个设备需要共享同一个总线进行通信。

而如果多个设备同时向总线发送信号,就会出现信号冲突的问题。

为了解决这个问题,可以使用三态门。

三态门的工作原理如下:当输入信号为逻辑“0”时,输出信号为低电平;当输入信号为逻辑“1”时,输出信号为高电平;当输入信号为高阻态时,输出信号为高阻态,即不对总线产生任何影响。

这样,当某个设备需要向总线发送信号时,将输出信号设置为逻辑“1”;而其他设备需要向总线发送信号时,将输出信号设置为高阻态。

这样就能够有效地避免信号冲突,实现多设备共享总线的通信。

非门是一种最简单的逻辑门,它只有一个输入和一个输出。

非门的输出与输入相反,即当输入为逻辑“1”时,输出为逻辑“0”;当输入为逻辑“0”时,输出为逻辑“1”。

非门常常用于逻辑电路的反相和逻辑运算中。

非门的工作原理如下:当输入信号为逻辑“1”时,输出信号为逻辑“0”;当输入信号为逻辑“0”时,输出信号为逻辑“1”。

非门的应用非常广泛,可以用于逻辑电路中的反相操作,也可以用于逻辑运算中的非运算。

三态与非门原理是数字逻辑电路中常用的两种基本逻辑门。

它们都具有简单、高效、可靠的特点,在电子设备中得到了广泛的应用。

通过合理的使用三态与非门,可以实现复杂的逻辑运算和数据处理,为现代电子技术的发展提供了强大的支持。

三态输出电路

就是具有高电平、低电平和高阻抗三种输出状态的门电路,又称三态门输出电路。

在固态机互联板电路,“I/O”板电路中,除了以上几种组合门电路,三态门电路也是必不可少的。

一、电路组成

三态门电路主要有TTL三态门电路和CMOS三态门电路.

不难看出,二种输出三态门电路都是在普通门电路的基础上附加控制电路而构成.

二、工作原理

(1)TTL三态门电路工作原理图1给出了三态门的电路结构图及图形符号。

其中控制端·EN为低电平时(面=口/,P点为高电平,二极管D截止,电路工作状态和普通的与非门没有区别。

这时Y=·A’B,可能是高电子也可能是低电平,视A、B的状态而定。

而当控制端EN为高电平时(EN=1),P点为低电平,它控制T1发射极,把VBl钳位在1V,使T,、T5载止。

同时二极管D导通,T4的基极电位被钳在1V,使T4载止。

由于T4、T5同时载止,所以输出端呈高阻状态o

(2)图2中是将CMOS反相器的输出端同一个模拟开关相串联,即可组成三态门。

图中T,、T2组成反相器,TG和反相器3组成模拟开关,其工作原理是:当控制端电压Ve =1时,由于模拟开关断开,输出端与电源Vm,输出端与地都相当于开路,故呈现高阻抗状态。

当Ve=OV时,模拟开关闭合,输出电压VY取决于反相器的输入电压。

若V4= OV,则T1截止,T2导通,VY=VDD,输出高电平;若Va=1,则Tl导通,T2载止,VY=OV,输出低电平。

上述电路中,控制端EN为低电平时与非门处于工作状态,所以该电路为低电平有效同样还有高电平有效控制电路。

三、三态门电路的应用

(1)多路信号分时传递

在一些复杂的数字系统(象固态机的互联板,U0板等)中,为了减少各个单元电路之间连线的数目,希望能在同一条导线上分时传递若干个门电路的输出信号。

这时可采用图3所示的连接方式。

图中G1-Gn。

均为三态与非门。

只要在工作时控制各个门的En端轮流等于“1”,而且任何时候仅有一个等于“1”就可以把各个门的输出信号轮流送到公共的传输线一总线上而互不干扰。

(2)用作双向传输的总线接收器

利用三态输出门电路还能实现数据的双向传输。

固态机数据传送这种功能也是常用的。

在图4电路中,当E。

=1时,C:工作而C2为高阻抗,数据D。

经C1反相后送到总线上去。

当皿=0时,C2工作而C1为高阻抗,来自总线的数据经C2反相后由D,送出。

三态输出门电路(TS(Three-state output Gate)门)

右图为三态门输出门电路的原理图。

在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。

普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。

T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。

三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。

因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(vcc)阻抗无穷大。

因此这第三种状态也称高阻状态。