8位串入并出移位寄存器简介

- 格式:doc

- 大小:49.17 KB

- 文档页数:2

移位寄存器串入并出与并入串出在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。

这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。

实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

移位寄存器的输入、输出都可以是并行或串行的。

它们经常被配置成串入并出(serial-in, parallel-out, SIPO)的形式或并入串出(parallel-in, serial-out, PISO),这样就可以实现并行数据和串行数据的转换。

当然,也有输入、输出同时为串行或并行的情况。

此外,还有一些移位寄存器为双向的,也就是说它允许数据来回传输,输入端同时可以作为输出端,输出端同时也可以作为输入端。

如果把移位寄存器的串行输入端,和并行输出端的最后一位连接起来,还可以构成循环移位寄存器(circular shift register),用来实现循环计数功能。

串入并出串入并出形式的移位寄存器接法,可以将输入的串行数据以并行格式输出。

串行通信要求的几位数据完成输入之后,就可以在输出端的各位同时读出并行数据。

并入串出并入串出形式的移位寄存器接法,通过下图所示D1-D4并行输入段接收4位外部并行数据,而Q为串行输出的引脚。

为了将数据写入到寄存器中,写/移位控制线必须保持低电平。

写入完成,需要移位时,写/移位控制线则必须处于高电平,而且必须给予时间脉冲,每提供一个时间脉冲,向左(或向右)移动一位。

8位移位寄存器的设计1.设计原理:8位移位寄存器由8个D触发器组成,每个触发器都有一个数据输入端和一个时钟输入端。

在时钟上升沿到达时,将数据输入端的值传递到输出端,同时由上一个触发器的输出端传递给下一个触发器的输入端。

这样,在每个时钟周期内,数据会从寄存器的一端移动到寄存器的另一端。

2.功能:-数据存储:将输入的8位数据存储在寄存器中。

-数据移位:可以将寄存器中的数据向左或向右移动一位。

-数据传输:可以将寄存器中的数据传递给其他元件或模块。

3.设计步骤:设计一个8位移位寄存器的步骤如下:1)确定需要的数据输入和输出端口数量和类型。

2)选择合适的D触发器,每个触发器都有一个数据输入端D和一个控制输入端CLK。

3)将8个D触发器按照顺序连接起来,每个触发器的输出端连接到下一个触发器的输入端,形成一个移位寄存器。

4)定义时钟信号的激活边沿(上升沿或下降沿)。

5)设计时钟信号的生成电路,以便控制数据的移位操作。

6)连接数据输入端口和时钟信号的生成电路到移位寄存器的各个触发器。

7)连接数据输出端口到移位寄存器最后一个触发器的输出端。

4.应用:-数据缓存:将来自外部设备的数据存储在寄存器中,然后按需传递给其他模块。

-数据传输:通过移位寄存器将数据从一个模块传递到另一个模块,以实现数据通信。

-时序操作:通过移位寄存器来生成时序信号,控制其他模块的状态和行为。

-数据处理:通过移位寄存器将数据进行移位、旋转、倒序等操作,并输出结果。

-逻辑运算:通过移位寄存器将数据进行逻辑与、逻辑或、逻辑异或等操作。

总结:8位移位寄存器是一种常见且实用的数字逻辑元件,用于存储和移动8位二进制数据。

通过8个D触发器的组合,可以实现数据的存储、移位和传输等功能。

在数字电子系统中,8位移位寄存器被广泛应用于数据缓存、数据传输、时序操作、数据处理和逻辑运算等场景。

设计和理解8位移位寄存器对于数字电子系统的开发和优化是非常重要的。

实验八简单寄存器及移位寄存器设计一、 实验前准备1.EXCD-1可编程片上系统开发板;2.下载线;3.5V电源。

二、 实验目的进一步学习VHDL语言,并学会利用ISE进行移位寄存器的设计与仿真,掌握移位寄存器的工作原理。

三、 实验原理移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左右移的控制信号便可实现双向移位要求。

根据寄存器存取信息的方式不同,寄存器可分为:串入串出、串入并出、并入串出、并入并出四种形式。

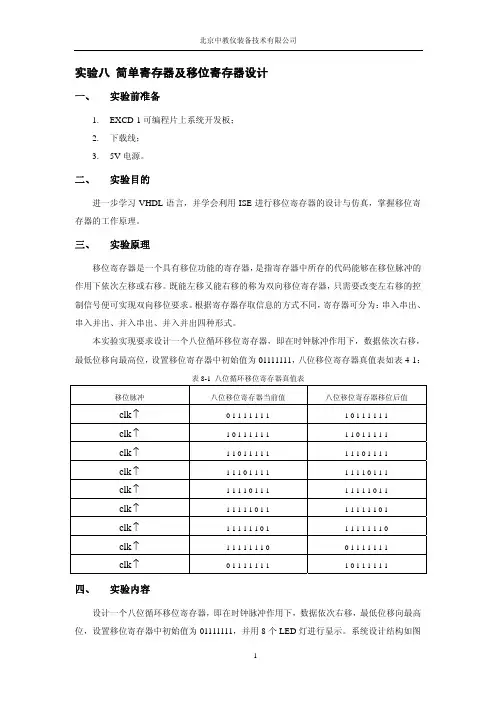

本实验实现要求设计一个八位循环移位寄存器,即在时钟脉冲作用下,数据依次右移,最低位移向最高位,设置移位寄存器中初始值为01111111,八位移位寄存器真值表如表4-1:表8-1 八位循环移位寄存器真值表移位脉冲八位移位寄存器当前值八位移位寄存器移位后值clk↑0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1clk↑ 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1clk↑ 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1clk↑ 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1clk↑ 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1clk↑ 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1clk↑ 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0clk↑ 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1clk↑0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1四、 实验内容设计一个八位循环移位寄存器,即在时钟脉冲作用下,数据依次右移,最低位移向最高位,设置移位寄存器中初始值为01111111,并用8个LED灯进行显示。

系统设计结构如图8-1所示:图8-1 循环移位寄存器设计结构图该系统包括分频模块和移位模块。

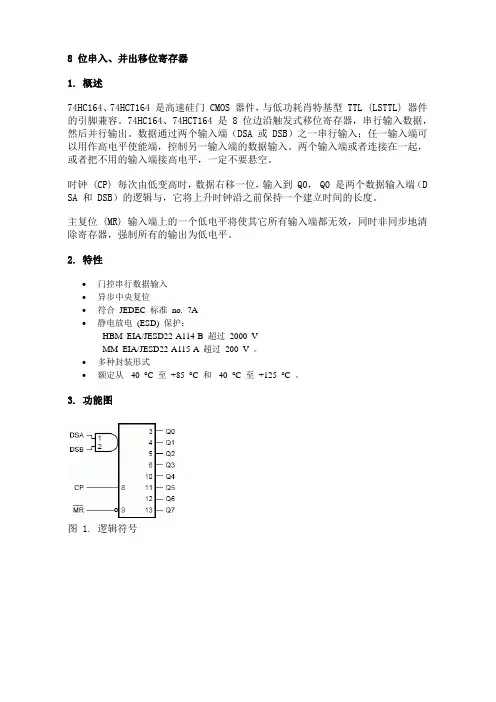

8 位串入、并出移位寄存器

1. 概述

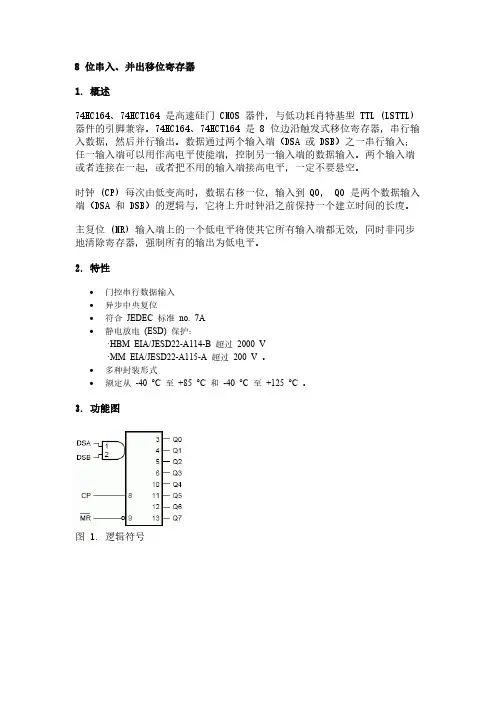

74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性

∙门控串行数据输入

∙异步中央复位

∙符合JEDEC 标准no. 7A

∙静电放电(ESD) 保护:

·HBM EIA/JESD22-A114-B 超过2000 V

·MM EIA/JESD22-A115-A 超过200 V 。

∙多种封装形式

∙额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

3. 功能图

图 1. 逻辑符号

图 2. IEC 逻辑符号

图 3. 逻辑图

图 4. 功能图

4. 引脚信息

图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置引脚说明。

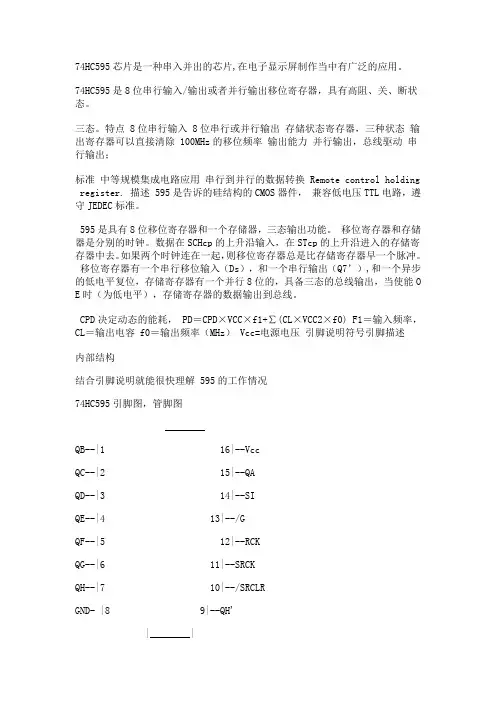

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote control holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能O E时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况74HC595引脚图,管脚图________QB--|1 16|--VccQC--|2 15|--QAQD--|3 14|--SIQE--|4 13|--/GQF--|5 12|--RCKQG--|6 11|--SRCKQH--|7 10|--/SRCLRGND- |8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

8 位串入、并出移位寄存器1. 概述74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(D SA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性•门控串行数据输入•异步中央复位•符合JEDEC 标准no. 7A•静电放电(ESD) 保护:·HBM EIA/JESD22-A114-B 超过2000 V·MM EIA/JESD22-A115-A 超过200 V 。

•多种封装形式•额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

3. 功能图图 1. 逻辑符号图 2. IEC 逻辑符号图 3. 逻辑图图 4. 功能图4. 引脚信息图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置引脚说明符号引脚说明DSA 1数据输入DSB 1数据输入Q0~Q3 3~6输出GND7 地(0 V)CP 8时钟输入(低电平到高电平边沿触发)/M/R 9中央复位输入(低电平有效)Q4~Q710~13输出VCC14正电源罗74HC164中文资料(功能,真值表,引脚图及电气参数介绍)SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

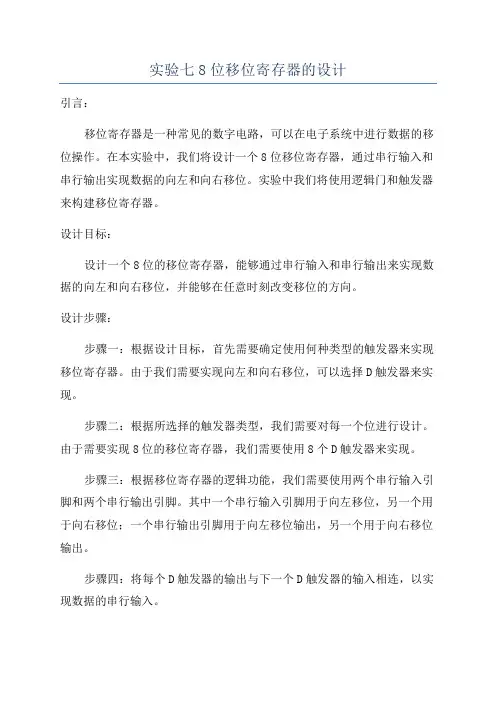

实验七8位移位寄存器的设计引言:移位寄存器是一种常见的数字电路,可以在电子系统中进行数据的移位操作。

在本实验中,我们将设计一个8位移位寄存器,通过串行输入和串行输出实现数据的向左和向右移位。

实验中我们将使用逻辑门和触发器来构建移位寄存器。

设计目标:设计一个8位的移位寄存器,能够通过串行输入和串行输出来实现数据的向左和向右移位,并能够在任意时刻改变移位的方向。

设计步骤:步骤一:根据设计目标,首先需要确定使用何种类型的触发器来实现移位寄存器。

由于我们需要实现向左和向右移位,可以选择D触发器来实现。

步骤二:根据所选择的触发器类型,我们需要对每一个位进行设计。

由于需要实现8位的移位寄存器,我们需要使用8个D触发器来实现。

步骤三:根据移位寄存器的逻辑功能,我们需要使用两个串行输入引脚和两个串行输出引脚。

其中一个串行输入引脚用于向左移位,另一个用于向右移位;一个串行输出引脚用于向左移位输出,另一个用于向右移位输出。

步骤四:将每个D触发器的输出与下一个D触发器的输入相连,以实现数据的串行输入。

步骤五:将第一个D触发器的输入与移位方向引脚相连,以确定移位方向。

步骤六:将最后一个D触发器的输出与移位输出引脚相连,以实现数据的串行输出。

步骤七:对每个D触发器的时钟输入引脚进行控制,以实现移位操作的时序。

结果分析:通过上述步骤所设计的8位移位寄存器,我们可以实现数据的向左和向右移位操作,并可以通过串行输入和串行输出进行控制和观测。

移位寄存器在很多应用中都有广泛的应用,例如串行通信、数据压缩、图像处理等。

总结:通过本次实验,我们了解了移位寄存器的基本原理和设计方法。

通过串行输入和串行输出实现数据的移位,可以有效地利用数字电路来实现数据处理任务。

移位寄存器作为一种重要的数字电路,为我们提供了一种灵活和便捷的数据存储和处理方式。

在今后的学习和实际应用中,我们可以进一步深入了解移位寄存器的其他应用和扩展。

74HC1648位串入并出移位寄存器产品说明书说明书发行履历:第 1 页共11 页74HC164是高速CMOS电路,管脚与低功耗肖特基TTL(LSTTL)系列兼容。

74HC164是8位的串入并出、边沿触发的移位寄存器,串入数据由DSA、DSB输入,在每个时钟CP的上升沿数据向右移一位,数据由DSA和DSB相与而成,且在上升沿到来之前已满足了建立时间。

低电平有效的复位信号将直接把寄存器清零而输出为低。

其主要特点如下:●较宽的工作电压:2~6V●相与的串行输入,直接的清零信号●输出能驱动10个LSTTL负载●封装型式:DIP14 / SOP142、功能框图及引脚说明2.4、功能说明h:时钟上升沿前建立起来的高电平电压L:低电平l:时钟上升沿前建立起来的低电平电压q:对应于时钟上升沿时,前面一个寄存器的状态↑:时钟上升沿3、电特性3.1、极限参数除非另有规定,T amb=25℃第 3 页共11 页3.3、电气特性除非另有规定,T amb=25℃第4 页共11 页第 5 页共11 页CCV CC=6.0V 35 85 - MHzV M=50%; V I=GND~VCC图1.时钟(CP)到输出端(Qn)的传输延时、时钟脉宽、输出传输时间和最大时钟频率V M=50%; V I=GND~VCC图2.主复位(MR)脉宽,主复位到输出端(Qn)的传输延时、主复位结束到时钟(CP)的响应时间第 6 页共11 页V M=50%; V I=GND~VCC图3. Dn输入前的数据建立时间和保持时间图4.测试开关时间的负载电路注:RT:终端电阻须与信号发生器的输出阻抗匹配CL:负载电容须包括夹具有探针电容第7 页共11 页第8 页共11 页4. 1、DIP14外形图与封装尺寸第9 页共11 页第10 页共11 页5.1、产品中有毒有害物质或元素的名称及含量第11 页共11 页。

移位寄存器串入出与并入串出————————————————————————————————作者:————————————————————————————————日期:移位寄存器串入并出与并入串出在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。

这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。

实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

移位寄存器的输入、输出都可以是并行或串行的。

它们经常被配置成串入并出(serial-in, parallel-out, SIPO)的形式或并入串出(parallel-in, serial-out, PISO),这样就可以实现并行数据和串行数据的转换。

当然,也有输入、输出同时为串行或并行的情况。

此外,还有一些移位寄存器为双向的,也就是说它允许数据来回传输,输入端同时可以作为输出端,输出端同时也可以作为输入端。

如果把移位寄存器的串行输入端,和并行输出端的最后一位连接起来,还可以构成循环移位寄存器(circular shift register),用来实现循环计数功能。

串入并出串入并出形式的移位寄存器接法,可以将输入的串行数据以并行格式输出。

串行通信要求的几位数据完成输入之后,就可以在输出端的各位同时读出并行数据。

并入串出并入串出形式的移位寄存器接法,通过下图所示D1-D4并行输入段接收4位外部并行数据,而Q为串行输出的引脚。

为了将数据写入到寄存器中,写/移位控制线必须保持低电平。

写入完成,需要移位时,写/移位控制线则必须处于高电平,而且必须给予时间脉冲,每提供一个时间脉冲,向左(或向右)移动一位。

74ls595原理2( 移位锁存器74ls595原理74ls595为 8位输出锁存移位寄存器RESET: 复位信号shitf clock:移位时钟serial data input:串行数据输入output enable:输出使能latch clock:锁存时钟595有3层结构:第一层为移位D触发器;第二层为锁存D触发器;第三层为输出3态门;当复位信号为0时,移位D触发器清0;当移位脉冲从L->H时,第一个移位D触发器的Q=D;其它的Qn=Qn-1;当锁存脉冲从0->1时,第二层为锁存D触发器的输出=/输入; 当OE=1时,595的输出为高阻态;当OE=0时,595的输出为第二层为锁存D触发器的输出的反相; 74595的数据端:QA--QH: 八位并行输出端,可以接点阵的8列。

QH': 级联输出端。

将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SCLR(10脚): 低电平时将移位寄存器的数据清零。

通常将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

通常都选微秒级) RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

通常将RCK置为低电平,当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

通常都选微秒级),更新显示数据。

/G(13脚): 高电平时禁止输出(高阻态)。

如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。

比通过数据端移位控制要省时省力。

注:74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。

74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。

74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。

CD4000 双3输入端或非门+单非门 TICD4001 四2输入端或非门 HIT/NSC/TI/GOL CD4002 双4输入端或非门 NSCCD4006 18位串入/串出移位寄存器 NSCCD4007 双互补对加反相器 NSCCD4008 4位超前进位全加器 NSCCD4009 六反相缓冲/变换器 NSCCD4010 六同相缓冲/变换器 NSCCD4011 四2输入端与非门 HIT/TICD4012 双4输入端与非门 NSCCD4013 双主-从D型触发器 FSC/NSC/TOS CD4014 8位串入/并入-串出移位寄存器 NSC CD4015 双4位串入/并出移位寄存器 TICD4016 四传输门 FSC/TICD4017 十进制计数/分配器 FSC/TI/MOTCD4018 可预制1/N计数器 NSC/MOTCD4019 四与或选择器 PHICD4020 14级串行二进制计数/分频器 FSC CD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器 NSC/MOTCD4023 三3输入端与非门 NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门 NSC/MOT/TICD4026 十进制计数/7段译码器 NSC/MOT/TI CD4027 双J-K触发器 NSC/MOT/TICD4028 BCD码十进制译码器 NSC/MOT/TI CD4029 可预置可逆计数器 NSC/MOT/TICD4030 四异或门 NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器 NSC/TICD4033 十进制计数/7段译码器 NSC/TICD4034 8位通用总线寄存器 NSC/MOT/TI CD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TICD4038 三串行加法器 NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器 NSC/MOT/TICD4042 四锁存D型触发器 NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TICD4046 锁相环 NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TICD4048 4输入端可扩展多功能门 NSC/HIT/TI CD4049 六反相缓冲/变换器 NSC/HIT/TICD4050 六同相缓冲/变换器 NSC/MOT/TICD4051 八选一模拟开关 NSC/MOT/TICD4052 双4选1模拟开关 NSC/MOT/TICD4053 三组二路模拟开关 NSC/MOT/TICD4054 液晶显示驱动器 NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TICD4056 液晶显示驱动器 NSC/HIT/TICD4059 “N”分频计数器 NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOTCD4063 四位数字比较器 NSC/HIT/TICD4066 四传输门 NSC/TI/MOTCD4067 16选1模拟开关 NSC/TICD4068 八输入端与非门/与门 NSC/HIT/TI CD4069 六反相器 NSC/HIT/TICD4070 四异或门 NSC/HIT/TICD4071 四2输入端或门 NSC/TICD4072 双4输入端或门 NSC/TICD4073 三3输入端与门 NSC/TICD4075 三3输入端或门 NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门 HITCD4078 8输入端或非门/或门CD4081 四2输入端与门 NSC/HIT/TICD4082 双4输入端与门 NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/STCD4094 8位移位存储总线寄存器 NSC/TI/PHI CD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器 NSC/MOT/TICD4099 8位可寻址锁存器 NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器 NSC\TICD40107 双2输入端与非缓冲/驱动器HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器 NSC\MOTCD40160 可预置BCD加计数器 NSC\MOTCD40161 可预置4位二进制加计数器NSC\MOTCD40162 BCD加法计数器 NSC\MOTCD40163 4位二进制同步计数器 NSC\MOT CD40174 六锁存D型触发器 NSC\TI\MOT CD40175 四D型触发器 NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TICD40193 可预置4位二进制加/减计数器NSC\TICD40194 4位并入/串入-并出/串出移位寄存NSC\MOTCD40195 4位并入/串入-并出/串出移位寄存NSC\MOTCD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐) CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器。

74hc595的引脚功能和作用描述74HC59574HC595是硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

74HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SHcp 的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

[编辑本段]特点8位串行输入/8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率[编辑本段]输出能力并行输出,总线驱动;串行输出;标准中等规模集成电路595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

[编辑本段]参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压[编辑本段]引脚说明符号引脚描述Q0…Q7 15,1,7 并行数据输出GND 8 地Q7’9 串行数据输出MR 10 主复位(低电平)SHCP 11 移位寄存器时钟输入STCP 12 存储寄存器时钟输入OE 13 输出有效(低电平)DS 14 串行数据输入VCC 16 电源[编辑本段]功能表输入输出功能SHCP STCP OE MR DS Q7’Qn ××L ↓×L NC MR为低电平时仅仅影响移位寄存器×↑L L ×L L 空移位寄存器到输出寄存器××H L ×L Z 清空移位寄存器,并行输出为高阻状态↑×L H H Q6 NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

8位移位寄存器的设计数字电路与逻辑设计实验报告班级信息安全2班姓名张亮学号20110806228一、实验目的熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言设计8位移位寄存器。

并且掌握组合逻辑电路的功能测试和时序仿真;学会运用逻辑图设计电路。

二、实验内容用VHDL语言设计由边沿触发式D触发器构成的8位串入并出移位寄存器,并进行仿真与分析;(查找相应资料)三、实验原理? 逻辑电路的原理在数字电路中,用来存放二进制数据或代码的电路称为寄存器。

寄存器是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储一位二进制代码,存放N位二进制代码的寄存器,需用n个触发器来构成。

按功能可分为:基本寄存器和移位寄存器。

移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

目前常用的集成移位寄存器种类很多,如74164、74165、74166、74595均为八位单向移位寄存器,74195为四位单向移存器,74194为四位双向移存器,74198为八位双向移存器。

逻辑图如图所示:逻辑功能表? 通过实验实现逻辑的原理在CMOS移位寄存器中,有的品种只具有串行或并行中的一种输入方式,但也有些品种同时兼有串行和并行两种输入方式。

串行输入的数据加到第一个寄存单元的D端,在时钟脉冲的作用下输入,数据传送速度较慢;并行输入的数据一般由寄存单元的R、S端送入,传送速度较快。

移位数字电路与逻辑设计实验报告寄存器的移位方向有右移和左移之分。

右移是指数据由左边最低位输入,依次由右边的最高位输出;左移时,右边的第一位为最低位,最左边的则为最高位,数据由低位的右边输入,由高位的左边输出。

四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII 软件仿真平台。

8位串入并出移位寄存器电路的设计姓名:林蔼龄学号:1060601007 班级:物理系BTEC电子信息工程A班8位串入并出移位寄存器电路的设计一、实验内容用VHDL语言实现8位串入并出移位寄存器电路的设计。

二、程序建立文本编辑新窗口,在文件编辑窗口中输入如下程序: LIBRARY IEEE; USE IEEE.Std_logic_1164.all; ENTITY text ISPORT (a, b, clr, clock: IN BIT;q : BUFFER BIT_VECTOR(0 TO 7)); END text;ARCHITECTURE one OF text IS BEGINPROCESS (a,b,clr,clock)BEGINIF clr = '0' THENq <= "00000000";ELSEIF clock'EVENT AND clock = '1'THENFOR i IN q'RANGE LOOPIF i = 0 THEN q (i) <= (a AND b);ELSEQ (i) <= q(i-1);END IF;END LOOP;END IF;END IF;END PROCESS;END one;保存本文本。

三、仿真结果建立仿真波形文件,进行时序防震,得到的仿真结果如下图1所示:图1下面的是2016年经典励志语录,需要的朋友可以欣赏,不需要的朋友下载后可以编辑删除~~谢谢~~1、有来路,没退路;留退路,是绝路。

2、为目标,晚卧夜半,梦别星辰,脚踏实地,凌云舍我其谁!3、做一题会一题,一题决定命运。

4、静下来,铸我实力;拼上去,亮我风采。

5、拼一载春秋,搏一生无悔。

6、狠抓基础是成功的基础,持之以恒是胜利的保证。

7、把汗水变成珍珠,把梦想变成现实!8、拧成一股绳,搏尽一份力,狠下一条心,共圆一个梦。

8位移位寄存器,串行输入时经_____个脉冲后,8位数码全部移入寄存

器中。

8位移位寄存器,串行输入时经8个脉冲后,8位数码全部移入寄存器中。

8位移位寄存器串行输入时经8个脉冲后全部移入寄存器中。

寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类。

基本寄存器只能并行送入数据,也只能并行输出。

移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,或串行输入、并行输出,十分灵活,用途也很广。

8位串入并出移位寄存器电路的设计姓名:林蔼龄学号:1060601007班级:物理系BTEC电子信息工程A班8位串入并出移位寄存器电路的设计• 一、实验内容用VHDL语言实现8位吊入并出移位寄存器电路的设计。

二、程序建立文本编辑新窗口,在文件编辑窗口中输入如下程序:LIBRARY IEEE; USE IEEE. Std_logic_1164. all; ENTITY text ISPORT (a, b, clr, clock: IN BIT;q : BUFFER BIT_VECTOR(O TO 7)); END text;ARCHITECTURE one OF text IS BEGINPROCESS (a, b, clr, clock)BEGINIF clr = ' O' THENq <= "00000000";ELSEIF clock, EVENT AND clock = T'THENFOR i IN q' RANGE LOOPIF i = 0 THEN q (i) <= (a AND b);ELSEQ (i) <= Q(i-1);END IF;END LOOP;END IF;END IF;END PROCESS:END one;保存本文本。

三、仿真结果建立仿真波形文件,进行时序防震,得到的仿真结果如下图1所示:图1下面的是2016年经典励志语录,需要的朋友可以欣赏,不需要的朋友下载后可以编辑删除〜〜谢谢〜〜1、 有来路,没退路;留退路,是绝路。

2、 为目标,晚卧夜半,梦别星辰,脚踏实地,凌云舍我其谁!3、做一题会一 题,一题决定命运。

4、 静下来,铸我实力;拼上去,亮我风采。

爭 ip4 • V<w BU frXF^ --------Iliaal ・*E Btfwitt VtvrVef M !« >|y n ^Ntbitr ST ・ in <h ・rvU 口刃 皿口・,SFl. 诃•口尸"彳 2 KA M.JU I ----- 1 用 ®8SOSS©£«5X 询焕_ jm.__rrn5、拼一载春秋,搏一生无悔。

8 位串入、并出移位寄存器

1. 概述

74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性

门控串行数据输入?异步中央复位?符合JEDEC 标准no. 7A ?静电放电(ESD) 保护:?·HBM EIA/JESD22-A114-B 超过2000 V

·MM EIA/JESD22-A115-A 超过200 V 。

多种封装形式?额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

?3. 功能图

逻辑符号 1. 图

图 2. IEC 逻辑符号

图 3. 逻辑图

图 4. 功能图

引脚信息4.

封装的引脚配置和 TSSOP14 5. DIP14图、SO14、SSOP14

引脚说明符号引脚说明

数据输入DSA1

数据输入1DSB

3~6输出Q0~Q3 地7 (0 V)GND

8时钟输入(低电平到高电平边沿触发)CP 9中央复位输入(低电平有效)/M/输10~1Q4~Q 正电1VC。