8位移位寄存器的电路设计与版图实现

- 格式:doc

- 大小:1.36 MB

- 文档页数:27

8位移位寄存器原理8位移位寄存器(8-bit shift register)是一种经典的数字电路元件,在计算机和电子系统中被广泛应用。

它能够将输入数据按位进行移动和暂时存储,并且可以通过控制信号来控制移位方向和操作模式。

本文将详细介绍8位移位寄存器的工作原理及其应用。

1.基本原理8位移位寄存器由8个触发器组成,每个触发器负责存储并传输一个位数据。

这些触发器可以是D触发器、JK触发器或T触发器,具体根据设计的需要来确定。

移位寄存器将相邻触发器的输出与输入连接起来,形成一个环形结构。

2.移位操作(1)串行移位:在串行移位模式下,数据从最低位(LSB)依次向最高位(MSB)移动。

数据可以从一个输入端(如D输入)输入,也可以从上一个触发器输出传输过来。

通过控制时钟输入信号,每个时钟周期,数据向左或向右移动一个位,新的数据进入移位寄存器的最低位,最高位的数据被移出。

移入的数据可以是新的输入数据,也可以是上一个触发器的输出数据。

这样,移位寄存器就可以暂时存储输入数据,并实现数据的移动,同时保持之前的数据不变。

(2)并行移位:在并行移位模式下,整个数据可以一次性输入或输出。

可以通过并行输入信号一次性输入8位数据,或者通过并行输出信号一次性输出8位数据。

3.移位方向4.控制信号控制信号是控制8位移位寄存器工作的重要因素,主要有以下几个:(1)时钟信号:用于控制数据的移动速度和时序,每个时钟周期移动一个位。

(2) 重置信号(Reset):用于清除移位寄存器中存储的数据,将所有触发器的输出设为0。

(3) 并行输入信号(Shift/Load):用于选择是进行串行移位还是并行移位。

当选择串行移位时,输入信号会逐位移入,否则,输入信号通过并行输入端一次性加载到移位寄存器。

(4) 移位方向信号(Shift Left/Right):用于选择移位方向。

当设置为左移时,数据从最低位向最高位移动;当设置为右移时,数据从最高位向最低位移动。

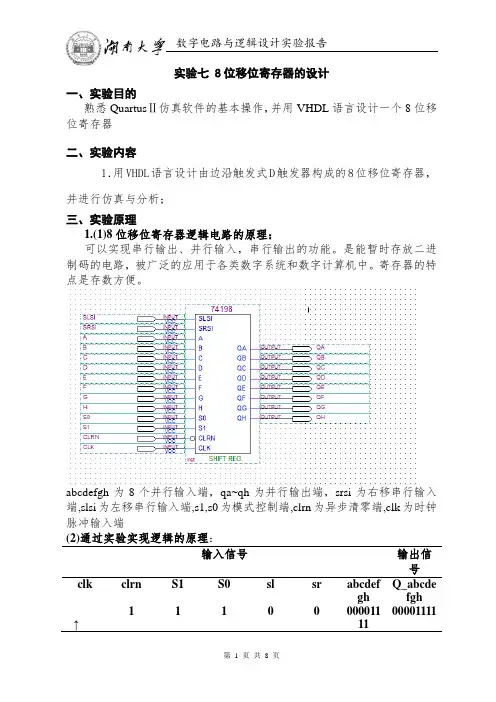

实验七 8位移位寄存器的设计一、实验目的熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言设计一个8位移位寄存器二、实验内容1.用VHDL语言设计由边沿触发式D触发器构成的8位移位寄存器,并进行仿真与分析;三、实验原理1.(1)8位移位寄存器逻辑电路的原理:可以实现串行输出、并行输入,串行输出的功能。

是能暂时存放二进制码的电路,被广泛的应用于各类数字系统和数字计算机中。

寄存器的特点是存数方便。

abcdefgh为8个并行输入端,qa~qh为并行输出端,srsi为右移串行输入端,slsi为左移串行输入端,s1,s0为模式控制端,clrn为异步清零端,clk为时钟脉冲输入端(2)通过实验实现逻辑的原理:输入信号输出信号clk clrn S1 S0 sl sr abcdefgh Q_abcdefgh↑1 1 1 0 0 0000111100001111↑ 1 1 0 1 0 0000111100011111 ↑ 1 1 0 1 0 0001111100111111 ↑ 1 1 0 0 0 0011111101111110 ↑ 1 1 0 0 0 011111111111100 ↑ 1 0 0 0 0 111111011111100 ↑ 1 0 1 0 1 111111011111110 ↑ 1 0 1 0 1 111111111111111 ↑ 1 0 1 0 0 1111111101111111 ↑ 1 0 1 0 0 0111111100111111↑0 0 0 0 0 00111111 0000000四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:1、编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

8位移位寄存器的设计1.设计原理:8位移位寄存器由8个D触发器组成,每个触发器都有一个数据输入端和一个时钟输入端。

在时钟上升沿到达时,将数据输入端的值传递到输出端,同时由上一个触发器的输出端传递给下一个触发器的输入端。

这样,在每个时钟周期内,数据会从寄存器的一端移动到寄存器的另一端。

2.功能:-数据存储:将输入的8位数据存储在寄存器中。

-数据移位:可以将寄存器中的数据向左或向右移动一位。

-数据传输:可以将寄存器中的数据传递给其他元件或模块。

3.设计步骤:设计一个8位移位寄存器的步骤如下:1)确定需要的数据输入和输出端口数量和类型。

2)选择合适的D触发器,每个触发器都有一个数据输入端D和一个控制输入端CLK。

3)将8个D触发器按照顺序连接起来,每个触发器的输出端连接到下一个触发器的输入端,形成一个移位寄存器。

4)定义时钟信号的激活边沿(上升沿或下降沿)。

5)设计时钟信号的生成电路,以便控制数据的移位操作。

6)连接数据输入端口和时钟信号的生成电路到移位寄存器的各个触发器。

7)连接数据输出端口到移位寄存器最后一个触发器的输出端。

4.应用:-数据缓存:将来自外部设备的数据存储在寄存器中,然后按需传递给其他模块。

-数据传输:通过移位寄存器将数据从一个模块传递到另一个模块,以实现数据通信。

-时序操作:通过移位寄存器来生成时序信号,控制其他模块的状态和行为。

-数据处理:通过移位寄存器将数据进行移位、旋转、倒序等操作,并输出结果。

-逻辑运算:通过移位寄存器将数据进行逻辑与、逻辑或、逻辑异或等操作。

总结:8位移位寄存器是一种常见且实用的数字逻辑元件,用于存储和移动8位二进制数据。

通过8个D触发器的组合,可以实现数据的存储、移位和传输等功能。

在数字电子系统中,8位移位寄存器被广泛应用于数据缓存、数据传输、时序操作、数据处理和逻辑运算等场景。

设计和理解8位移位寄存器对于数字电子系统的开发和优化是非常重要的。

8位移位寄存器原理8位移位寄存器是一种数字电路器件,用于在计算机和通信系统中实现数据的有序传输和存储。

它主要用于数据的移位操作,可以将输入信号按照一定的规律传输到输出端,同时可以在寄存器内部存储数据。

接下来,我将详细介绍8位移位寄存器的原理及其工作原理。

1.原理概述8位移位寄存器由8个单独的存储元件(例如D触发器)连接而成。

每个存储元件可以存储一个二进制位。

这些存储元件串联在一起,形成一个移位寄存器。

通过给移位寄存器提供时钟信号和控制信号,可以实现数据的移位操作。

2.功能模块-数据输入:接受外部输入信号,将数据加载到移位寄存器中。

通常通过并行输入引脚实现。

-数据输出:将移位寄存器中的数据输出到外部。

-移位控制:控制数据在移位寄存器中的各个存储元件之间的传输方向。

-时钟控制:提供时钟信号的输入,用于控制数据的移位操作。

3.工作原理-并行加载:首先将需要加载的数据同时输入到移位寄存器的每个存储元件中。

这可以通过并行输入引脚实现。

然后,通过时钟信号将数据写入存储元件。

-数据输出:通过将存储元件之一的输出引脚连接到输出端口,可以将移位寄存器中的数据输出到外部。

-时序控制:通过时钟信号的控制,可以确定数据在移位寄存器中传输和存储的时钟周期。

4.应用-数据传输:移位寄存器在通信系统中常用于将数据从输入端传输到输出端,通过移位操作可以实现数据的有序传输。

比如,在串行通信中,数据先经过并行串行转换器,然后通过移位寄存器按位传输。

-编码和解码:移位寄存器可以用于编码和解码操作。

通过移位操作和逻辑门电路,可以将输入的数据编码为特定的编码形式。

反之,也可以通过类似的方式将编码数据解码成普通二进制数据。

-时序控制:移位寄存器在时序电路中也经常被使用。

通过移位操作和时钟信号的控制,可以实现各种时序控制功能,如计数器、状态机等。

总结:8位移位寄存器是一种常见的数字电路器件,用于实现数据的有序传输和存储。

它由8个存储元件连接而成,可以通过移位控制和时钟控制实现数据的移位和存储操作。

移位寄存器的设计及实现移位寄存器(Shift Register)是一种常用的数字逻辑电路器件,它能够将数据按照输入和输出的时序进行移位操作。

通过移位寄存器,我们可以实现数据的串行传输、并行-串行或者串行-并行转换、数据延迟等功能。

本文将对移位寄存器的设计与实现进行介绍。

一、移位寄存器的设计1.串行输入、串行输出的移位寄存器这种移位寄存器称为串行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过一个输入端串行输入,然后通过触发器依次移位,最后从输出端串行输出。

2.并行输入、并行输出的移位寄存器这种移位寄存器称为并行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过n个输入端并行输入到各个触发器,然后通过控制信号进行同步移位。

最后从n个输出端并行输出。

3.并行输入、串行输出的移位寄存器这种移位寄存器称为并行-串行移位寄存器,它先从n个输入端并行输入数据,然后通过控制信号进行同步移位,并将移位结果通过一个输出端串行输出。

4.串行输入、并行输出的移位寄存器这种移位寄存器称为串行-并行移位寄存器,它先从一个输入端串行输入数据,然后通过触发器进行移位,最后将移位结果从n个输出端并行输出。

1.触发器选择由于是8位移位寄存器,需要选择8个触发器。

常用的触发器有D触发器、JK触发器等,可以根据实际需求选择合适的触发器。

2.输入输出端口设计设计一个输入端口用于串行输入数据。

由于是串行输入,需要一个时钟信号和一个使能信号进行同步移位操作。

同时,设计一个输出端口用于串行输出数据。

3.控制信号电路设计根据串行输入、串行输出的要求,需要设计一个时钟信号和一个使能信号的电路。

使能信号在移位过程中保持逻辑高电平,只有当8位数据全部移位完成时才将使能信号置为逻辑低电平。

二、移位寄存器的实现1.设计一个8位移位寄存器电路,并连接8个D触发器。

2.将串行输入信号与D触发器的数据端相连,时钟信号与D触发器的时钟端相连,使能信号与D触发器的使能端相连。

实验七8位移位寄存器的设计引言:移位寄存器是一种常见的数字电路,可以在电子系统中进行数据的移位操作。

在本实验中,我们将设计一个8位移位寄存器,通过串行输入和串行输出实现数据的向左和向右移位。

实验中我们将使用逻辑门和触发器来构建移位寄存器。

设计目标:设计一个8位的移位寄存器,能够通过串行输入和串行输出来实现数据的向左和向右移位,并能够在任意时刻改变移位的方向。

设计步骤:步骤一:根据设计目标,首先需要确定使用何种类型的触发器来实现移位寄存器。

由于我们需要实现向左和向右移位,可以选择D触发器来实现。

步骤二:根据所选择的触发器类型,我们需要对每一个位进行设计。

由于需要实现8位的移位寄存器,我们需要使用8个D触发器来实现。

步骤三:根据移位寄存器的逻辑功能,我们需要使用两个串行输入引脚和两个串行输出引脚。

其中一个串行输入引脚用于向左移位,另一个用于向右移位;一个串行输出引脚用于向左移位输出,另一个用于向右移位输出。

步骤四:将每个D触发器的输出与下一个D触发器的输入相连,以实现数据的串行输入。

步骤五:将第一个D触发器的输入与移位方向引脚相连,以确定移位方向。

步骤六:将最后一个D触发器的输出与移位输出引脚相连,以实现数据的串行输出。

步骤七:对每个D触发器的时钟输入引脚进行控制,以实现移位操作的时序。

结果分析:通过上述步骤所设计的8位移位寄存器,我们可以实现数据的向左和向右移位操作,并可以通过串行输入和串行输出进行控制和观测。

移位寄存器在很多应用中都有广泛的应用,例如串行通信、数据压缩、图像处理等。

总结:通过本次实验,我们了解了移位寄存器的基本原理和设计方法。

通过串行输入和串行输出实现数据的移位,可以有效地利用数字电路来实现数据处理任务。

移位寄存器作为一种重要的数字电路,为我们提供了一种灵活和便捷的数据存储和处理方式。

在今后的学习和实际应用中,我们可以进一步深入了解移位寄存器的其他应用和扩展。

设计8位双向移位寄存器电路双向移位寄存器是一种能够在输入数据上进行向左或向右移位的电路。

它能够在输入端接收一串数据,并将这些数据连续地向左或向右移位,同时将当前移位的结果输出。

我们可以设计一个8位双向移位寄存器电路,以满足这个需求。

下面是如何设计这个电路的详细步骤:1.确定电路的基本结构:首先,我们需要确定电路的基本功能模块,包括输入输出模块、移位控制模块和移位寄存器模块。

2.输入输出模块:该模块用于接收输入数据并驱动输出数据。

我们需要提供一个8位输入端和一个8位输出端。

输入端可以是一个按钮或开关,用于输入要移位的数据。

输出端可以是一组LED灯,用于显示当前移位的结果。

3.移位控制模块:该模块用于控制移位方向和移位次数。

我们可以使用一个开关来选择移位方向(向左或向右)。

此外,我们需要一个计数器来控制移位次数。

当计数器达到8时,移位操作完成,将重新开始。

4.移位寄存器模块:该模块用于存储输入数据并进行移位操作。

我们可以使用8个D触发器来实现移位寄存器,其中每个D触发器都能够存储一个位的数据。

我们需要将每个D触发器的输出与其相邻的D触发器的输入连接起来,以实现数据的移位。

5.连接各个模块:将输入输出模块、移位控制模块和移位寄存器模块连接在一起,形成一个完整的电路。

确保每个模块的输入输出正确连接,并且信号能够正确传递。

6.进行测试:使用合适的输入数据测试电路。

先选择移位方向,然后输入要移位的数据,观察输出结果是否符合预期。

7.优化电路:根据测试结果来优化电路的性能和稳定性。

可能需要对电路布局进行调整,优化时序逻辑,以确保电路能够在正确的时钟频率下正常工作。

双向移位寄存器电路的设计过程需要考虑许多细节,包括输入输出接口的选择、移位控制逻辑的实现、移位寄存器的构建以及电路的布局和时序。

尽管这里只提供了一个简要的设计步骤,但是通过深入研究每个步骤,我们可以开始设计和实现一个功能完善且可靠的8位双向移位寄存器电路。

目录摘要 (1)1 多功能双向移位寄存器 (2)1.1 基本工作原理 (2)1.2 基本实现方案 (2)2 电路图设计 (4)2.1 电路结构 (4)2.2 真值表 (4)3 Verilog描述8位双向移位寄存器 (6)4 程序仿真 (8)5 总结 (10)参考文献 (11)摘要移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。

在本设计中,使用硬件描述语言Verilog,在EDA工具QuartussII中,设计8位双向移位寄存器硬件电路,根据设计语言进行功能时序仿真,验证设计的正确性与可行性。

关键字:Verilog QuartusII 移位寄存器8位双向移位寄存器电路设计1 多功能双向移位寄存器1.1 基本工作原理移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。

在本设计中定义移位寄存器中的数据从低位触发器移向高位为右移,移向低位为左移。

为了扩展逻辑功能和增加使用的灵活性,某些双向移位寄存器集成电路产品又附加了并行输入、并行输出等功能。

如图1所示是上述几种工作模式的简化示意图。

并行输入并行输出右移串行输入(D IR 左移串行输出(D OL 右移串行输出(D OR ) D IL )0123图1 多功能移位寄存器工作模式简图1.2 基本实现方案图2所示是实现数据保持、右移、左移、并行置入和并行输出的一种电路方案。

图中的D 触发器m FF 是N 为移位寄存器中的第m 位触发器,在其数据输入端插入了一个4选1数据选择器m MUX ,用2位编码输入10S S 、控制m MUX ,来选择触发器输入信号m D 的来源。

当100S S ==时,选择该触发器本身输出的m Q ,次态为1m n nm mQ D Q +==,使触发器保持状态不变;当100,1S S ==时,触发器1m FF -的输出1m Q -被选中,故CP 脉冲上升沿到来时,m FF 存入1m FF -此前的逻辑值,即1m 1n n m Q Q +-=,而1m +1n nm Q Q +=,从而实现右移功能;类似地,当101,0S S ==时,m MUX 选择1m Q +,实现左移功能;而当101S S ==时,则选中并行输入数据m DI ,其次态1n m m Q DI +=,从而完成并行数据的置入功能。

8位移位寄存器的设计数字电路与逻辑设计实验报告班级信息安全2班姓名张亮学号20110806228一、实验目的熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言设计8位移位寄存器。

并且掌握组合逻辑电路的功能测试和时序仿真;学会运用逻辑图设计电路。

二、实验内容用VHDL语言设计由边沿触发式D触发器构成的8位串入并出移位寄存器,并进行仿真与分析;(查找相应资料)三、实验原理? 逻辑电路的原理在数字电路中,用来存放二进制数据或代码的电路称为寄存器。

寄存器是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储一位二进制代码,存放N位二进制代码的寄存器,需用n个触发器来构成。

按功能可分为:基本寄存器和移位寄存器。

移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

目前常用的集成移位寄存器种类很多,如74164、74165、74166、74595均为八位单向移位寄存器,74195为四位单向移存器,74194为四位双向移存器,74198为八位双向移存器。

逻辑图如图所示:逻辑功能表? 通过实验实现逻辑的原理在CMOS移位寄存器中,有的品种只具有串行或并行中的一种输入方式,但也有些品种同时兼有串行和并行两种输入方式。

串行输入的数据加到第一个寄存单元的D端,在时钟脉冲的作用下输入,数据传送速度较慢;并行输入的数据一般由寄存单元的R、S端送入,传送速度较快。

移位数字电路与逻辑设计实验报告寄存器的移位方向有右移和左移之分。

右移是指数据由左边最低位输入,依次由右边的最高位输出;左移时,右边的第一位为最低位,最左边的则为最高位,数据由低位的右边输入,由高位的左边输出。

四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII 软件仿真平台。

8位移位寄存器原理

8位移位寄存器是一种数字电路,用于将8位数据进行位移操作,通常包括左移(Shift Left)和右移(Shift Right)操作。

这种寄存器的原理如下:

1.寄存器结构:8位移位寄存器由8个触发器(Flip-Flop)组成,每个触发器存储一个位的数据。

这些触发器按顺序连接,构成一个8位的寄存器。

2.输入数据:8位数据输入进入寄存器的最低位(LSB),同时高位数据可能丢失或移动到其他地方,取决于具体的位移操作。

3.位移操作:寄存器可以执行两种常见的位移操作,即左移和右移。

-左移(Shift Left):数据向左移动一位,最高位被丢弃,最低位被填充零。

-右移(Shift Right):数据向右移动一位,最低位被丢弃,最高位被填充零。

4.控制逻辑:8位移位寄存器需要一个控制逻辑来确定位移方向和步数。

通常,它包括一个控制输入,可以指示是左移还是右移,并且可以指定连续的位移操作。

5.输出数据:8位移位寄存器的输出可以用于其他电路或处理器的输入,或者它可以被连接到其他寄存器以进行进一步的数据处理。

8位移位寄存器常用于数字信号处理、微处理器中的移位指令、数据加密等应用,因为它们可以方便地执行位移操作。

通过控制寄存器的位移方向和步数,可以实现不同的位移效果,从而满足不同的应用需求。

8 位串入、并出移位寄存器1. 概述74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性•门控串行数据输入•异步中央复位•符合JEDEC 标准no. 7A•静电放电(ESD) 保护:·HBM EIA/JESD22-A114-B 超过2000 V·MM EIA/JESD22-A115-A 超过200 V 。

•多种封装形式•额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

3. 功能图图 1. 逻辑符号图 2. IEC 逻辑符号图 3. 逻辑图图 4. 功能图4. 引脚信息图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置引脚说明符号引脚说明DSA 1数据输入DSB 1数据输入Q0~Q3 3~6输出GND7 地(0 V)CP 8时钟输入(低电平到高电平边沿触发)/M/R 9中央复位输入(低电平有效)Q4~Q710~13输出VCC14正电源罗。

实验五寄存器电路设计1.画出74ls74构成的4位单向移位寄存器并说明其工作原理。

74ls74是由四个D触发器串联而成的四位单向移位寄存器。

移位寄存器使其中所储存的二进制,在一位脉冲的作用下左右移动;一位触发器可以储存1位二进制代码,存放n位二进制就需要n个触发器构成。

2.8位移位寄存器设计原理图。

实验五寄存器电路设计一、实验目的l、掌握寄存器的工作原理、测试和分析其工作状态2、掌握集成双向移位寄存器和并行数据锁存器的功能及使用方法3、8位移位寄存器电路设计二、实验内容及步骤1、并行输入/并行输出寄存器功能测试表5.12、移位寄存器功能测试(1)用74LS74构成的4位单向移位寄存器表5.2(2) 74LSl94表5.3S1S0CP Dsr Dsl I3I2I1I0Q3Q2Q1Q0 0X X X X X X X X X00001X X0X X X X X X0000111X X d3d2d1d0d3d2d1d01011X X X X X11111010X X X X X0000110X1X X X X1111110X0X X X X0000100X X X X X X X00003、8D锁存器功能测试表5.4E D7D6D5D4D3D2D1D0Q7Q6Q5Q4Q3Q2Q1Q0 001011011000000000 011011011010110110 00011101100111011 01100010011000100 1X X X X X X X X X00000000注: “个”表示单脉冲上升沿4、8位移位寄存器电路设计(如不够可自行加纸)自制表格:Cr S1 S0 CP Dsr Dsl I3 I2 I1 I0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q00 X X X X X X X X X 0 0 0 0 0 0 0 01 X X 0 X X X X X X 0 0 0 0 0 0 0 0 1 1 1 ↑X X 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 ↑0 X X X X X 0 0 0 0 0 0 0 0 1 0 1 ↑ 1 X X X X X 1 1 1 1 1 1 1 1 1 1 0 ↑0 X X X X X 0 0 0 0 0 0 0 0 1 1 0 ↑ 1 X X X X X 1 1 1 1 1 1 1 1 1 0 0 X X X X X X X 0 0 0 0 0 0 0 0实验仿真图:实验原理:实验主要用到用两片74LS194芯片构成8位移步寄存器。

实验四八位双向移位寄存器的设计实验目的:本实验的目的是设计一个八位双向移位寄存器,该寄存器能够实现数据在寄存器中向左或向右进行移位,并能在移位过程中保持数据的完整性。

实验原理:双向移位寄存器是一种特殊的寄存器,能够将数据从一个位置移动到另一个位置,并且可以选择向左或向右移位。

其主要原理是通过一个移位控制信号来判断是向左移位还是向右移位,并通过移位操作来实现数据的移动。

在设计八位双向移位寄存器时,需要使用八个触发器来存储数据,并采用串级连接的方式将它们连接起来,以实现数据的移位。

同时,还需要一个移位控制信号,用来控制数据的移位方向。

当移位控制信号为1时,表示向右移位;当移位控制信号为0时,表示向左移位。

移位寄存器的设计主要包括以下几个方面的工作:1.数据输入:通过八个输入端口将数据输入到触发器中,每个触发器存储一位数据。

数据可以是由其他部件产生的信号,也可以是手动输入的信号。

2.数据输出:通过八个输出端口从触发器中输出数据。

输出的数据可以被其他部件使用,也可以通过显示设备或者其他方式进行显示。

3.移位方向控制:需要有一个移位控制信号来控制数据的移位方向。

移位控制信号可以由其他部件产生,也可以是手动输入的信号。

4.移位操作:通过移位操作来实现数据的移动。

根据移位控制信号的不同,决定向左还是向右移动,并将数据从一个触发器移动到另一个触发器中。

这需要使用触发器的时钟信号来驱动移位操作。

实验步骤:1.将八个触发器按照串级方式进行连接,形成一个八位双向移位寄存器的结构。

确保触发器按照顺序连接,并连接到移位操作控制信号。

2.设置八个输入端口和八个输出端口,用于输入和输出数据。

将数据输入到触发器中,并从触发器中输出数据。

3.设置一个移位控制信号端口,用于控制数据的移位方向。

该信号可以是手动输入的信号,也可以由其他部件产生。

4.设置一个时钟信号端口,用于驱动移位操作。

根据移位控制信号的不同,决定向左还是向右移动,并将数据从一个触发器移动到另一个触发器中。

8位串入并出移位寄存器电路的设计姓名:林蔼龄学号:1060601007 班级:物理系BTEC电子信息工程A班8位串入并出移位寄存器电路的设计一、实验内容用VHDL语言实现8位串入并出移位寄存器电路的设计。

二、程序建立文本编辑新窗口,在文件编辑窗口中输入如下程序: LIBRARY IEEE; USE IEEE.Std_logic_1164.all; ENTITY text ISPORT (a, b, clr, clock: IN BIT;q : BUFFER BIT_VECTOR(0 TO 7)); END text;ARCHITECTURE one OF text IS BEGINPROCESS (a,b,clr,clock)BEGINIF clr = '0' THENq <= "00000000";ELSEIF clock'EVENT AND clock = '1'THENFOR i IN q'RANGE LOOPIF i = 0 THEN q (i) <= (a AND b);ELSEQ (i) <= q(i-1);END IF;END LOOP;END IF;END IF;END PROCESS;END one;保存本文本。

三、仿真结果建立仿真波形文件,进行时序防震,得到的仿真结果如下图1所示:图1下面的是2016年经典励志语录,需要的朋友可以欣赏,不需要的朋友下载后可以编辑删除~~谢谢~~1、有来路,没退路;留退路,是绝路。

2、为目标,晚卧夜半,梦别星辰,脚踏实地,凌云舍我其谁!3、做一题会一题,一题决定命运。

4、静下来,铸我实力;拼上去,亮我风采。

5、拼一载春秋,搏一生无悔。

6、狠抓基础是成功的基础,持之以恒是胜利的保证。

7、把汗水变成珍珠,把梦想变成现实!8、拧成一股绳,搏尽一份力,狠下一条心,共圆一个梦。

基于Verilog的八位移位寄存器优秀doc资料Verilog HDL 八位移位寄存器林春涛电子信息科学与技术 08级 2班 3108001158module EightBit(direction,clk,q,d;reg[7:0]q; //定义了一个 8位的名为 q 的 reg 型数据input direction,clk,d; //声明输入信号 direction,clk 和 dOutput[7:0]q; //声明输出信号 qinitial q=0;//初始化寄存器输出 always @(posedgeclkbeginshift(q,d,direction;//调用等待任务 shift endtask shift;//定义移位寄存器开始移位 inout [7:0]Q;input D;input dir;if(dir==0//当 direction 为 0时定义为左移,否则为右移beginQ<=(Q<<1;Q[0]<=D;endelsebeginQ<=(Q>>1;Q[7]<=D;endendtaskendmodule编译仿真图如下:结果分析:图中设计了三个 d 为高电平的区域,图的左半部分下可见 direction 为 0,寄存器左移, 每次 clk 上升沿到达时,可见 q[0]的值一直向高位传。

右半部分 direction 设为1,寄存器右移,每次 clk 上升沿到达时,可见 q[7]的值一直向低位移动。

可见实现了八位移位寄存器。

LUT链和寄存器链的使用在Cyclone的LE之间除了LAB局部互连和进位外,还有LUT链、寄存器链。

使用LUT链可以把相邻的LE中的LUT连接起来构成复杂的组合逻辑,寄存器链可以把相邻的LE中的寄存器连接起来,构成诸如移位寄存器的功能,如图1所示。

图1 LUT链和寄存器链的使用寄存器的原理及应用课型:讲授 主讲:史娟芬教学目的:掌握数码寄存器和移位寄存器的逻辑功能 教学重点:掌握中规模四位双向移位寄存器的逻辑功能 教学难点:掌握中规模四位双向移位寄存器的逻辑功能 教学课时:两课时复习提问:写出RS 触发器、JK 触发器、D 触发器、T 触发器、T`触发器的逻辑功能、特性方程。

8位移位寄存器原理8位移位寄存器的原理基于触发器和传输门的组合。

它由8个触发器构成,每个触发器都可以存储1位数据。

其中,第一个触发器(Q0)连接输入数据线,而其他触发器的输入则与前一位触发器的输出连接。

这样就可以实现数据的逐位移动。

移位寄存器还包括一个控制线,用于控制数据的移位方向。

移位寄存器的工作模式可以分为串行和并行两种。

在串行模式下,数据从第一个触发器输入,逐位移动至最后一个触发器输出,形成一条数据序列。

在并行模式下,数据通过多条并行输入线进入8位移位寄存器的每个触发器,然后同时输出。

移位寄存器的工作模式可以通过控制线进行选择。

移位寄存器的工作过程如下:1.初始化:将所有触发器的输出设置为0,将控制线置于初始状态。

2.数据输入:将输入数据线连接至第一个触发器的D端,使得数据进入移位寄存器。

3.移位操作:根据控制线的信号,触发器会根据输入数据,将数据逐位向后移动。

如果控制线为低电平,则数据从最后一个触发器移向第一个触发器(相当于向左移位);如果控制线为高电平,则数据从第一个触发器移向最后一个触发器(相当于向右移位)。

4.数据输出:根据需要,可以将数据从移位寄存器的任意触发器输出。

8位移位寄存器的应用广泛。

例如,在串行通信中,发送方使用移位寄存器将并行数据转换为串行数据,并通过单一的数据线将数据传输至接收方。

在串行通信中,接收方通过移位寄存器将串行数据转换为并行数据。

此外,移位寄存器还被用于数据缓存、数据序列化和复位信号生成等应用中。

总结起来,8位移位寄存器是一种通过触发器和传输门的组合,将输入数据逐位移动的数字电路。

它具有串行和并行两种工作模式,可以用于数据序列化、并行数据转换为串行数据、数据缓存和数据传输等应用中。

这一原理简单而直观,并在现代电子通信和计算机系统中扮演了重要的角色。