32位移位寄存器

- 格式:doc

- 大小:333.00 KB

- 文档页数:10

移位寄存器原理引言移位寄存器是一种常见的数字电路元件,它用于在计算机和其他数字系统中处理串行数据的移位操作。

本文将介绍移位寄存器的原理和工作方式。

移位寄存器的定义移位寄存器是一种特殊的存储器元件,它可以在输入端和输出端之间进行数据移位操作。

移位寄存器通常是由触发器组成的,每个触发器都可以存储一个位(bit)的数据。

移位寄存器的输入端和输出端都是并行接口,但是数据在寄存器内部是以串行的方式传输的。

移位寄存器的工作原理并行加载移位寄存器最常见的操作之一是并行加载。

在这种操作模式下,通过并行输入引脚将数据加载到移位寄存器中。

当时钟信号到达时,移位寄存器将存储的数据向左或向右移位,并将其输出到并行输出引脚。

移位的方向由控制信号决定。

串行移位除了并行加载,移位寄存器还可以进行串行移位操作。

在串行移位模式下,输入数据通过串行输入引脚进入移位寄存器,并且顺序地从寄存器的一端移出。

当时钟信号到达时,移位寄存器会将存储的数据按位移动一个位置,并从另一端输出。

这种操作模式可以用于各种应用,例如数据的平移、数据的旋转等。

循环移位循环移位是移位寄存器的另一个重要特性。

在循环移位模式下,移位寄存器的输出会通过反馈引脚重新进入输入端,形成一个闭环。

当时钟信号到达时,移位寄存器将在输入和输出之间循环移动数据。

这种操作模式常用于数据的循环处理、数据的延时等应用场景。

移位寄存器的应用移位寄存器在数字系统中有广泛的应用。

以下是一些常见的应用场景:•移位寄存器常用于串行通信中的数据传输和接收。

通过移位寄存器,可以将并行数据转换为串行数据进行传输,并将接收到的串行数据重新转换为并行数据。

•移位寄存器可以用于数字时钟电路中。

通过串行输入信号和移位寄存器的移位操作,可以实现时钟信号的频率除法,从而生成不同的时钟信号。

•移位寄存器还可用于数据的处理和分析。

例如,在图像处理中,移位寄存器可以用来进行图像平移、旋转和缩放等操作。

总结移位寄存器是一种常见的数字电路元件,用于处理串行数据的移位操作。

实验四一、实验名称32位并进/并出移位寄存器设计二、实验原理用一个8位移位寄存器,再增加一些电路,如4个8位锁存器等,设计成为一个能为32位二进制数进行不同方式移位的移位寄存器。

三、实验步骤1、建立一个工程项目,设置路径,项目名和顶层实体名一致;2、设计一个8位移位寄存器电路;3、设计一个8位锁存器电路;4、运用元件调用声明语句和元件例化语句完成顶层设计。

四、实验程序1、八位移位寄存器程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY jicun ISPORT ( CLK,CO: IN STD_LOGIC; --时钟和进位输入MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位模式控制字 D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); -- 待加载移位的数据 QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --移位数据输出CN : OUT STD_LOGIC); --- 进位输出END jicun;ARCHITECTURE behav OF jicun ISSIGNAL REG : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL CY : STD_LOGIC;BEGINPROCESS(CLK,CO,MD)BEGINIF CLK'EVENT AND CLK='1' THENCASE MD ISWHEN "001"=> REG(0)<=CO; ---带进位循环左移REG(7 DOWNTO 1)<= REG(6 DOWNTO 0);CY<=REG(7);WHEN "010" => REG(0)<=REG(7); ---自循环左移REG(7 DOWNTO 1)<= REG(6 DOWNTO 0);WHEN "011"=>REG(7)<=REG(0); ---自循环右移REG(6 DOWNTO 0)<=REG(7 DOWNTO 1);WHEN "100" =>REG(7)<=CO; ---带进位循环右移REG(6 DOWNTO 0)<=REG(7 DOWNTO 1);CY<=REG(0);WHEN "101" =>REG(7 DOWNTO 0)<=D(7 DOWNTO 0); --加载待移数 WHEN OTHERS=>REG<=REG;CY<=CY;--保持END CASE;END IF;END PROCESS;QB(7 DOWNTO 0)<=REG(7 DOWNTO 0);CN<=CY;END behav;2、锁存器程序library ieee ;use ieee.std_logic_1164.all ;entity suocun isport(d : in std_logic_vector(7 downto 0) ;q: out std_logic_vector(7 downto 0);clk : in std_logic );end suocun ;architecture one of suocun issignal q1: std_logic_vector(7 downto 0);beginprocess(clk,q1)beginif clk'event and clk='1'thenq1<=d;end if;end process;q<=q1;end one;3、顶层设计程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY jicun32 ISPORT ( clk0,co: IN STD_LOGIC; --时钟和进位输入md : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位模式控制字db : IN STD_LOGIC_VECTOR(31 DOWNTO 0); -- 待加载移位的数据qb : OUT STD_LOGIC_VECTOR(31 DOWNTO 0); --移位数据输出 cn : OUT STD_LOGIC); --- 进位输出END jicun32;ARCHITECTURE one OF jicun32 ISCOMPONENT jicunPORT ( CLK,CO: IN STD_LOGIC;MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0);D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);CN : OUT STD_LOGIC);END COMPONENT;COMPONENT suocunport(d : in std_logic_vector(7 downto 0) ;q: out std_logic_vector(7 downto 0);clk : in std_logic );END COMPONENT;SIGNAL e,f,g,h : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL l,m,n : STD_LOGIC;BEGINu1: suocun PORT MAP(d=>db(7 DOWNTO 0),q=>e,clk=>clk0);u2: jicun PORT MAP (D=>e,QB=>qb(7 DOWNTO 0),CLK=>clk0,CO=>co,CN=>l,MD=>md);u3: suocun PORT MAP(d=>db(15 DOWNTO 8),q=>f,clk=>clk0); u4: jicun PORT MAP(D=>f,QB=>qb(15 DOWNTO 8),CLK=>clk0,CO=>l,CN=>m,MD=>md);u5: suocun PORT MAP(d=>db(23 DOWNTO 16),q=>g,clk=>clk0); u6: jicun PORT MAP(D=>g,QB=>qb(23 DOWNTO 16),CLK=>clk0,CO=>m,CN=>n,MD=>md);u7: suocun PORT MAP(d=>db(31 DOWNTO 24),q=>h,clk=>clk0); u8: jicun PORT MAP(D=>h,QB=>qb(31 DOWNTO 24),CLK=>clk0,CO=>n,CN=>cn,MD=>md);END ARCHITECTURE one;五、仿真结果1、锁存器仿真2、八位寄存器仿真3、顶层设计仿真4、32位并进并出移位寄存器RTL图。

移位寄存器工作原理

移位寄存器是一种在数字电路中常用的重要元件,它可以将二进制数据按照一定的规律进行移位操作。

其工作原理如下:

1. 移位寄存器由多个触发器组成,常见的有D触发器、JK触

发器等。

每个触发器都可以存储一个二进制位。

2. 顺序移位寄存器中,触发器按照一定的顺序连接起来,每个触发器的输出接到下一个触发器的输入。

3. 并行移位寄存器中,所有的触发器的时钟信号都是相同的,即它们同时进行状态的更新。

4. 当时钟信号到达时,触发器按照一定的规则将输入数据传递给下一个触发器,并将上一个触发器的输出传递给自己的输出。

5. 移位操作可以是向左移位或向右移位,这取决于触发器的连接方式。

向左移位表示数据向高位移动,而向右移位表示数据向低位移动。

6. 移位寄存器还可以通过加载操作将特定的数据加载到触发器中,实现对寄存器的初始化或重置。

7. 移位寄存器常用于数据传输、数据序列生成、数字信号处理等领域,可以实现数据的移位、平移、循环移位等功能。

总之,移位寄存器的工作原理是利用触发器的连接方式和时钟

信号的控制,实现对二进制数据的移位操作。

它在数字电路中有着广泛的应用,是实现许多逻辑和运算功能的重要组成部分。

移位寄存器工作原理移位寄存器是数字电路中常见的一种逻辑电路,它在数字信号处理、数据存储等领域有着广泛的应用。

在实际的电子设备中,移位寄存器能够实现数据的移位、存储和转换,其工作原理十分重要。

本文将从移位寄存器的定义、分类、工作原理以及应用等方面进行详细介绍。

首先,移位寄存器是一种能够将数据进行移位操作的寄存器,它由多个触发器组成,能够实现数据的平行移位。

根据移位方向的不同,移位寄存器可以分为左移寄存器和右移寄存器两种类型。

左移寄存器是将数据向左移位,右移寄存器则是将数据向右移位。

移位寄存器的工作原理主要依赖于触发器的状态变化和时钟信号的控制,通过时钟信号的触发,数据可以按照设定的规则进行移位操作。

其次,移位寄存器的工作原理可以通过时钟信号和触发器的状态变化来解释。

在移位寄存器中,每个触发器都有两个稳定的状态,分别是置位和复位状态。

当时钟信号触发时,触发器的状态会发生变化,数据就会按照设定的方向进行移位。

对于左移寄存器来说,数据会从右向左移动,而右移寄存器则是从左向右移动。

通过时钟信号的不断触发,数据可以连续进行移位操作,实现数据的平行移位。

此外,移位寄存器在数字信号处理和数据存储中有着广泛的应用。

在数字信号处理中,移位寄存器可以用来实现数字信号的滤波、延时等功能。

在数据存储中,移位寄存器可以用来进行数据的缓存和转换,提高数据的处理效率。

此外,移位寄存器还可以用来实现逻辑运算、乘法和除法等操作,具有很高的灵活性和可编程性。

总的来说,移位寄存器是一种十分重要的数字电路,它能够实现数据的移位、存储和转换,具有广泛的应用前景。

通过对移位寄存器的工作原理进行深入理解,我们可以更好地应用它来解决实际的工程问题,提高数字电路的设计和应用水平。

希望本文能够对读者有所帮助,谢谢阅读!。

双向移位寄存器摘要:系统使用EDA技术设计了具有移位功能的寄存器,采用硬件描述语言VHDL进行设计,然后进行编程,时序仿真。

软件基于Verilog语言实现了双向32位移位寄存器的控制功能。

通过本设计熟悉QuartusII环境下的硬件描述操作流程,掌握基本的Verilog语法与编写风格。

关键字:EDA;Verilog;32位双向移位寄存器1.引言随着社会的发展,科学技术也在不断的进步。

特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。

近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入一个崭新的阶段,具体表现在:(1)电子器件及其技术的发展将更多地趋向于为EDA服务;(2)硬件电路与软件设计过程已高度渗透;(3)电子设计技术将归结为更加标准、规范的EDA工具和硬件描述语言HDL的运用;(4)数字系统的芯片化实现手段已成主流。

因此利用计算机和大规模复杂可编程逻辑器件进行现代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。

移位寄存器正在向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超高速硬件描述语言VHDL对32位双向移位寄存器进行编程实现。

2.课程设计的目的在计算机中常要求寄存器有移位功能。

如在进行乘法时,要求将部分积右移;在将并行传送的数转换成串行数时也需要移位。

因此,移位寄存器的设计是必要的。

本次设计的目的就是利用计算机组成原理中移位寄存器的相关知识,通过课程设计更加深入的了解移位寄存器的功能。

了解EDA技术,并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合计算机组成原理中的相关知识理论联系实际,掌握所学的课程知识。

通过对移位寄存器的设计,巩固和综合运用所学知识,提高对计算机组成原理的理解。

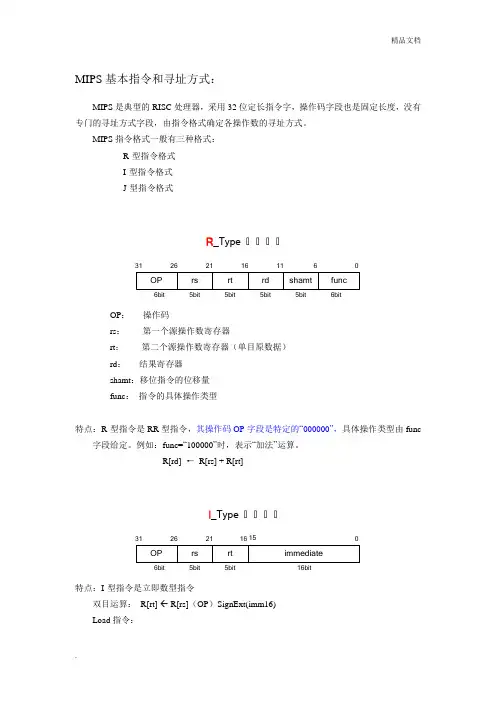

MIPS 基本指令和寻址方式:MIPS 是典型的RISC 处理器,采用32位定长指令字,操作码字段也是固定长度,没有专门的寻址方式字段,由指令格式确定各操作数的寻址方式。

MIPS 指令格式一般有三种格式: R-型指令格式 I-型指令格式 J-型指令格式R _Type 指指指指262116116316bit6bit5bit5bit5bit5bitOP : 操作码rs : 第一个源操作数寄存器rt : 第二个源操作数寄存器(单目原数据) rd : 结果寄存器 shamt :移位指令的位移量 func : 指令的具体操作类型特点:R-型指令是RR 型指令,其操作码OP 字段是特定的“000000”,具体操作类型由func字段给定。

例如:func=“100000”时,表示“加法”运算。

R[rd] ← R[rs] + R[rt]I _Type 指指指指2621163115特点:I-型指令是立即数型指令双目运算: R[rt] R[rs](OP )SignExt(imm16) Load 指令:Addr ← R[rs] + SignExt(imm16) 计算数据地址 (立即数要进行符号扩展) R[rt] ← M[Addr] 从存储器中取出数据,装入到寄存器中Store 指令:Addr ← R[rs] + SignExt(imm16) M[Addr] ← R[rt]J _Type 指令格式26316bit26bit25特点:J-型指令主要是无条件跳转指令,将当前PC 的高4位拼上26位立即数,后补两个“0”,作为跳转目标地址。

j L //goto L 指指指指指指指指指jal L //$ra 指PC+4;goto L 指指指指指指指指指R 型指令:定点运算: add / addu , sub / subu , sra , mult/multu , div/divu 逻辑运算: and / or / nor , sll / srl 比较分支: beq / bne / slt / sltu 跳转指令: jrI 型指令:定点运算: addi / addiu 逻辑运算: andi / ori 比较分支: slti / sltiu数据传送: lw / sw / lhu / sh / lbu / sb / luiJ 型指令: j / jal设计模块划分,教学安排1、MIPS格式指令系统设计2、指令存储器设计3、寄存器堆设计4、ALU设计——基本算术、逻辑单元的设计32位超前进位加法器的设计32位桶式移位寄存器的设计5、取指令部件的设计6、立即数处理单元设计7、单周期处理器设计——R型指令的数据通路设计I型指令的数据通路设计Load/Store指令的数据通路设计分支指令/转移指令的数据通路设计综合12条指令的完整数据通路设计8、ALU控制单元设计9、主控制单元的设计10、单周期处理器总体验证11、异常和中断处理及其电路实现12、带有异常和中断处理功能的处理器的设计设计示例1:指令存储器设计1、 指令存储器模块定义:指令存储器用于存放CPU 运算的程序指令和数据等,采用单端口存储器设计,设计最大为64个存储单元,每个存储单元数据宽度为32bit 。

XILINX FPGA设计中如何更好的优化资源在设计过程中我们只要注意一些要点,就可以节省下宝贵的芯片资源。

下面以XILINX FPGA为例阐述在设计中如何节约资源。

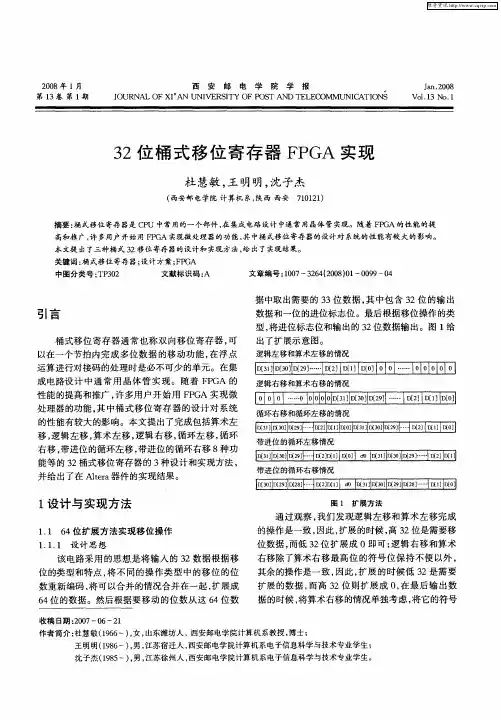

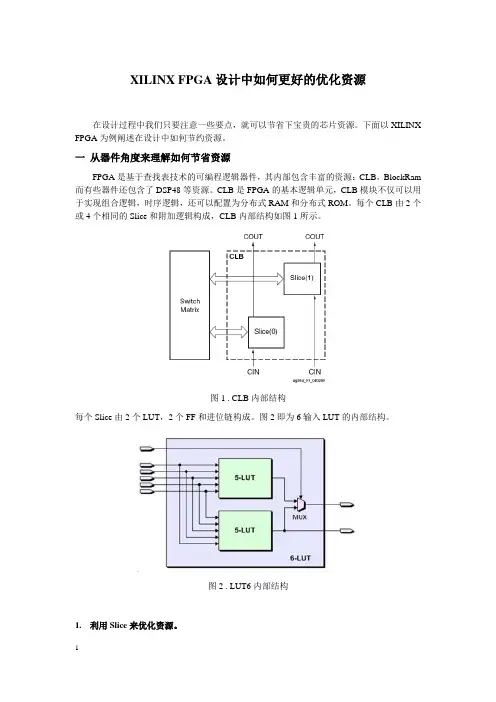

一从器件角度来理解如何节省资源FPGA是基于查找表技术的可编程逻辑器件,其内部包含丰富的资源:CLB,BlockRam 而有些器件还包含了DSP48等资源。

CLB是FPGA的基本逻辑单元,CLB模块不仅可以用于实现组合逻辑,时序逻辑,还可以配置为分布式RAM和分布式ROM。

每个CLB由2个或4个相同的Slice和附加逻辑构成,CLB内部结构如图1所示。

图1 . CLB内部结构每个Slice由2个LUT,2个FF和进位链构成。

图2即为6输入LUT的内部结构。

图2 . LUT6内部结构1.利用Slice来优化资源。

巧妙利用Slice可以节约很多的资源,典型的例子就是移位寄存器。

对比用代码编写的32位移位寄存器和用原语调用的32位移位寄存器,就可以看出怎样利用Slice节约资源。

用代码编写的32位移位寄存器:always@(posedge clk)beginQ <= {Q[30:0],D};end用原语调用一个32位移位寄存器:SRL32#(.INIT(32'h00000))U_DIV_LATENCY_OIF0[2:0](.CLK(Gclk), .D(Oif_base_q), .Q(Oi f_base_q0), .A0(1'b1), .A1(1'b1), .A2(1'b1), .A3(1'b1) , .A4(1'b1));综合之后可以发现,使用代码会消耗32个FF,而使用原语只要一个LUT6就可以完成。

用原语生成移位寄存器要比用代码生成寄存器节约32个触发器资源。

当然我们也可以例化IP核,但是,使用原语会比例化IP核在complier时候更加节省时间。

因为Verilog语言的IP核是由.v和.ngc文件构成的。

单片机移位寄存器引言:在单片机的应用中,移位寄存器是一种非常常用的功能模块。

它能够实现数据的移位操作,常被用于串行通信、显示控制、数据传输等场景。

本文将介绍移位寄存器的工作原理、应用领域以及设计注意事项。

一、移位寄存器的工作原理移位寄存器是一种能够将数据按位进行移位操作的寄存器。

它内部由多个触发器组成,每个触发器都能存储一个二进制位。

移位寄存器的输入端可以接收一个数据位,通过控制线来选择是向左移位还是向右移位。

当移位方向选择为向左移位时,寄存器中的所有数据位都向左移动一位,最右边的数据位被丢弃,同时在最左边补入一个新的数据位。

当移位方向选择为向右移位时,寄存器中的所有数据位都向右移动一位,最左边的数据位被丢弃,同时在最右边补入一个新的数据位。

这样就实现了数据的移位操作。

二、移位寄存器的应用领域1. 串行通信:移位寄存器常被用于串行通信中,它可以将并行数据转换为串行数据进行传输。

通过不断地向右移位,将并行数据逐位发送出去,从而实现数据的串行传输。

在接收端,再通过向左移位将串行数据转换为并行数据进行处理。

2. 显示控制:在数码管显示、液晶显示等场景中,移位寄存器可以用来控制显示的内容。

将需要显示的数据按照一定的格式存储在移位寄存器中,然后通过移位操作将数据逐位输出到显示模块,实现显示效果。

3. 数据传输:移位寄存器还可以用于数据传输场景。

例如,将传感器采集到的数据存储在移位寄存器中,通过移位操作将数据传输到其他模块进行处理或存储。

三、移位寄存器的设计注意事项1. 移位方向的选择:在设计中需要明确移位的方向,根据实际需求选择向左移位还是向右移位。

2. 移位速度的控制:移位的速度需要根据具体应用场景进行控制,过快或过慢都可能导致数据错误。

3. 寄存器位数的选择:根据需要存储的数据位数选择合适的移位寄存器。

位数过少可能导致数据丢失,位数过多则会浪费资源。

4. 级联的设计:如果需要存储的数据位数超过一个移位寄存器所能存储的范围,可以通过级联多个移位寄存器来实现,需要合理设计级联的方式和控制信号。

单片机移位寄存器在单片机中,移位寄存器是一种重要的功能模块,用于实现数据的移位操作。

移位寄存器通过改变数据的位序,可以实现数据在寄存器内部的移动和重排。

它在数字电路和信号处理中具有广泛的应用,如数据压缩、图像处理、通信等领域。

1. 移位寄存器的基本概念移位寄存器是一种特殊的寄存器,它具有多个存储单元(位),每个存储单元可以存储一个二进制位。

移位寄存器可以实现数据的左移和右移操作,通过改变数据的位置,可以将数据位重新排列。

移位寄存器可以分为串行移位寄存器和并行移位寄存器两种类型。

2. 串行移位寄存器串行移位寄存器是由多个触发器级联而成的,数据在寄存器内部逐个位地移动。

通常情况下,串行移位寄存器有一个输入端和一个输出端,数据通过输入端进入寄存器,经过一系列的触发器后,从输出端输出。

串行移位寄存器具有较小的尺寸和较低的功耗,适用于复杂的移位操作。

3. 并行移位寄存器并行移位寄存器是由多个存储单元并列连接而成的,数据同时在所有存储单元内进行移动。

并行移位寄存器具有较高的并行性和处理速度,但尺寸较大且功耗较高。

并行移位寄存器适合于对数据进行快速处理和重排。

4. 移位寄存器的应用移位寄存器在数字电路和信号处理中有广泛的应用。

在数字电路中,移位寄存器用于实现数据的序列操作,如数据的移动、重排、加密等。

在信号处理中,移位寄存器用于数据的滤波、压缩、编码/解码等操作。

5. 移位寄存器的扩展移位寄存器可以通过级联或并行连接的方式进行扩展。

级联连接是通过将多个移位寄存器的输出端与下一个移位寄存器的输入端相连,形成一个更大的移位寄存器。

并行连接是通过将多个移位寄存器的输入端同时连接到数据源,以实现更高的处理速度和并行性。

6. 总结移位寄存器作为一种重要的功能模块,在单片机中具有广泛的应用。

它可以实现数据的移位操作,改变数据的位序,从而实现数据的移动和重排。

串行移位寄存器和并行移位寄存器是常见的两种类型,各有优缺点。

移位寄存器可以通过级联或并行连接进行扩展,以满足不同场景的需求。

EDA课程设计报告题目:32位移位寄存器设计专业班级:电气工程及其自动化101 姓名:完成日期:2012年12月 30 日设计要求双向移位寄存器设计要求:完成以下功能特性的双向32 位移位寄存器。

同时要求有使能端,用1602 显示。

32位移位寄存器设计摘要:移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。

在本设计中使用硬件描述语言Verilog,在EDA 工具QuartussII中,设计32位双向移位寄存器硬件电路,根据设计语言进行功能时序仿真,验证设计的正确性与可行性。

关键词:Verilog QuartusII 移位寄存器1 引言随着社会的发展,科学技术也在不断的进步。

特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。

移位寄存器正在向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超高速硬件描述语言Verilog对移位寄存器进行编程实现。

现在各种装饰用的流水灯、广告彩灯、宣传画越来越多的出现在人民的生活当中,这些装饰控制设备多数要用移位寄存器来实现。

在计算机中常要求寄存器有移位功能。

如在进行乘法时,要求将部分积右移;在将并行传送的数转换成串行数时也需要移位。

因此,移位寄存器的设计是必要的。

2 总体设计方案移位寄存器的功能即是对每一个上升沿到来时,并且寄存器使能是时,对输入按照移位模式控制信号的要求实现输出的左移和右移。

首先,要完成双向的32位移位寄存器,就首先必须要实现8位移位寄存器作为基础。

其次,在4个8个移位寄存器的基础上达到32位移位寄存器的功能。

第一要有模式控制输入,来控制移位寄存器的移位方向;第二,有使能端,即在什么情况下移位寄存器才可以正常工作,才可以实现模式控制,什么时候置数,什么时候移位,是左移还是右移,这就要求使能是模式控制输入的前提;然后是脉冲控制信号,由要求可知,移位寄存器是在上升沿触发的,即在每一次上升沿到来时,移位寄存器使输入按照模式控制的要求向左或向右移一位;最后输入和输出,都要用到32位并行输入和输出。

单片机移位寄存器1. 什么是单片机移位寄存器单片机移位寄存器(Shift Register)是一种具有移位功能的寄存器,在数字电子电路中被广泛应用。

它由一组触发器(Flip-Flop)组成,可以将数据按照特定的方式进行移位操作。

2. 移位寄存器的工作原理移位寄存器通常由串行输入、串行输出、并行输入和并行输出四个主要部分组成。

其工作原理如下:•串行输入:数据输入信号逐位地经过寄存器,通过串行输入端口输入。

每当输入一个新的数据位时,原有的数据位将向左移位,腾出位置存放新的数据位。

•串行输出:从移位寄存器的串行输出端口输出数据。

当整个移位寄存器被移位后,最右边的数据位将从串行输出端口输出,同时,原有数据位向右移位填充空出的位置。

•并行输入:通过并行输入端口将整个数据一次性输入到移位寄存器中,不进行移位操作。

•并行输出:通过并行输出端口将整个移位寄存器的内容一次性输出。

3. 移位寄存器的应用场景移位寄存器在数字电子电路中具有广泛的应用,例如:3.1. 数据传输与存储移位寄存器可以用于将数据从一个地方传输到另一个地方,实现数据的序列化和反序列化。

在通信系统中,可以使用移位寄存器将并行数据转换为串行数据进行传输,或者将串行数据转换为并行数据进行处理。

3.2. 并行输入/输出扩展通过移位寄存器,可以将单片机的并行输入/输出引脚扩展为更多的输入/输出引脚。

通过将多个移位寄存器级联,可以实现更多的输入/输出引脚扩展。

3.3. 状态存储移位寄存器可以用于存储状态信息,例如程序计数器(Program Counter)和状态寄存器(Status Register)等。

4. 移位寄存器的类型根据移位寄存器的工作方式和结构特点,常见的移位寄存器包括以下几种类型:4.1. 并行入/串行出移位寄存器(PISO)并行入/串行出移位寄存器有多个并行输入引脚和一个串行输出引脚。

多个并行输入信号可以一次性并行输入到寄存器中,然后按位进行移位,输出到串行输出引脚上。

32位CPU寄存器简介以及TSS和TRCPU的指令一般都是通过寄存器来实现的。

其中有一个寄存器叫做EIP(Instruction Pointer,指令寄存器),程序的执行就是靠EIP的不断增加来完成的(跳转的话,EIP就变成了跳转到的地址)。

在Windows系统下,进程并不拥有EIP,那么只有进程,一个程序就无法运行。

而拥有这些寄存器的是线程,所以说进程是静态的。

一个CPU下只有一个EIP,也就是说同一时刻只能有一个线程可以运行,那么所说的多线程又是什么呢?事实上同一时刻也只有一个线程在运行,每个线程运行一段时间后,它会把它拥有的EIP等寄存器让出来,其它线程占有这些寄存器后,继续运行。

为了实现不同的线程之间的转换,CPU要求操作系统维护一份固定格式的数据(该数据存在于内存中),这份数据叫做Task-State Segment(TSS),在这份数据结构里,维护着线程的EAX,EIP,DS(Data Segment)等寄存器的内容。

EAX—EDX可称为数据寄存器,你除了直接访问外,还可分别对其高十六位和低十六位进行访问。

它们的低十六位就是把它们前边儿的E去掉,即EAX的低十六位就是AX。

而且它们的低十六位又可以分别进行八位访问,也就是说,AX还可以再进行分解,即AX还可分为AH(高八位)AL(低八位)。

在32位程序中,32位以内的函数返回值都通过eax寄存器来传递——这是__stdcall和__ccall的调用约定形成的结果。

Win32API函数(wsprintf使用__cdecl调用规则,其余所有API函数都是用__stdcall 调用规则)默认是是用eax返回值。

高级语言特性+编译器,通常将函数的返回值放在EAX中(单一返回值直接放EAX,如果多个返回值,则EAX中存放指针)。

00000000000000000000000000000000│ EAX ││ AX ││ AH │ AL │而CPU还有一个寄存器叫做Task Register(TR),该寄存器指向当前正在执行的线程的TSS。

河南科技学院新科学院EDA课程设计报告题目:32位移位寄存器设计专业班级:电气工程及其自动化106姓名:程琦指导教师:付广春完成日期:2013年01月01 日32位双向移位寄存器设计设计要求:完成以下功能特性的双向 32 位移位寄存器。

同时要求有使能端,用 1602 显示。

摘要:移位寄存器的功能即是对每一个上升沿到来时,并且寄存器使能是0时,对输入按照移位模式控制信号的要求实现输出的左移和右移。

32位移位寄存器可有4个八位的移位寄存器的逻辑关系来实现关键词:寄存器,上升沿,使能端1 引言移位寄存器使我们学习生活包括开发研究道路上不可或缺的一部分。

随着社会的发展,社会主义市场经济不断繁荣,各种装饰用的流水灯、广告彩灯、宣传画越来越多的出现在人民的生活当中,在大型晚会的现场,更是用的淋漓尽致,这些装饰控制设备多数要用移位寄存器来实现,因此,移位寄存器的研究和设计就变的至关重要。

2 总体设计方案因移位寄存器由多种不同的描述和设计方案,我们可以依据要求设列出最好最简单的设计方案。

首先,要完成双向的32位移位寄存器,就首先必须要实现8位移位寄存器作为基础。

其次,在4个8个移位寄存器的基础上达到32位移位寄存器的功能。

第一要有模式控制输入,来控制移位寄存器的移位方向;第二,有使能端,即在什么情况下移位寄存器才可以正常工作,才可以实现模位控制,是左移还是右移,这就要求使能是模式控制输入的前提;然后是脉冲控制信号,由题意可知,移位寄存器是在上升沿触发的,即在每一次上升沿到来时,移位寄存器使输入按照模位控制的要求向左或向右移一位;最后输入和输出,都要用到32并行输入和输出。

2.1 设计思路① 8位移位寄存器由设计要求可知,要实现8位的双向移位寄存器,并且还有使能端。

我们可令CLK为移位时钟信号,D为8位并行预臵数据端口,LOAD为并行数据预臵使能信号,QB为串行输出端口,LEFT_RIGHT 为移位模式控制数。

此移位寄存器的工作方式是:当CLK得上升沿到来时,过程被启动,如果这时预臵使能端LOAD为低电平,且移位模式控制数LEFT_RIGHT为1时,则最高位被移入寄存器中,其他7位依次左移一位同步并行臵入移位寄存器中;如果移位模式控制数LEFT_RIGHT为0时,则最低位被移入寄存器中,其他7位依次左移一位同步并行臵入移位寄存器中。

8位数码扫描显示电路设计一、实验目的学习硬件扫描显示电路的设计;二、实验原理动态数码扫描显示方式是利用了人眼的视觉暂留效应,把八个数码管按一定顺序进行点亮,当点亮的频率不大时,我们看到的是数码管一个个的点亮,然而,当点亮频率足够大时,我们看到的不再是一个一个的点亮,而是全部同时显示,与传统方式得到的视觉效果完全一样。

因此我们只要给数码管这样一个扫描频率,那么就可以实现两个以上的数码管同时点亮。

而这个频率我们可以通过一个计数器来产生,只要计数频率足够大,就可以实现我们的要求。

事实上,因为数码管点亮不是瞬间就可以的,它也需要一定的时间,该时间与数码管的选择有关系。

为了折中这一对矛盾,实验中一般可将计数频率选择在100Hz左右。

图示8位数码扫描显示电路,其中每个数码管的8 个段:h、g、f、e、d、c、b、a(h 是小数点)都分别连在一起,8 个数码管分别由8 个选通信号k1、k2、… k8 来选择。

被选通的数码管显示数据,其余关闭。

如在某一时刻,k3 为高电平,其余选通信号为低电平,这时仅k3 对应的数码管显示来自段信号端的数据,而其它7 个数码管呈现关闭状态。

根据这种电路状况,如果希望在8 个数码管显示希望的数据,就必须使得8 个选通信号k1、k2、… k8 分别被单独选通,并在此同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。

实验参考扫描显示程序中clk 是扫描时钟;SG 为7 段控制信号,由高位至低位分别接g、f、e、d、c、b、a 7个段;BT 是位选控制信号,接图5-2 中的8 个选通信号:k1、k2、… k8 。

程序中CNT8 是一个3 位计数器,作扫描计数信号,由进程P2 生成;进程P3 是7 段译码查表输出程序,进程P1 是对8 个数码管选通的扫描程序,例如当CNT8 等于"001" 时,K2 对应的数码管被选通,同时,A 被赋值3,再由进程P3 译码输出"1001111",显示在数码管上即为“3”;当CNT8 扫变时,将能在8 个数码管上显示数据:13579BDF 。

原理图如图1所示。

图1 八位数码管显示电路三、实验步骤1、建立一个工程项目,设置路径,项目名和顶层实体名一致;2、、设计一个动态扫描显示电路,在8 个数码管上显示数据:13579BDF;并进行编译仿真与下载测试;四、8位数码扫描显示电路的VHDL描述:LIBRARY IEEE;USE SCAN_LED ISPORT ( CLK : IN STD_LOGIC;SG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);BT: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END;ARCHITECTURE one OF SCAN_LED ISSIGNAL CNT8 : STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL A : INTEGER RANGE 0 TO 15;BEGINP1:PROCESS( CNT8 )BEGINCASE CNT8 ISWHEN "000" => BT <= "00000001" ; A <= 1 ;WHEN "001" => BT <= "00000010" ; A <= 2 ;WHEN "010" => BT <= "00000100" ; A <= 3 ;WHEN "011" => BT <= "00001000" ; A <= 4 ;WHEN "100" => BT <= "00010000" ; A <= 5 ;WHEN "101" => BT <= "00100000" ; A <= 6 ;WHEN "110" => BT <= "01000000" ; A <= 7 ;WHEN "111" => BT <= "" ; A <= 8 ;WHEN OTHERS => NULL ;END CASE ;END PROCESS P1;P2:PROCESS(CLK)BEGINIF CLK'EVENT AND CLK = '1' THEN CNT8 <= CNT8 + 1;END IF;END PROCESS P2 ;P3:PROCESS( A )BEGINCASE A ISWHEN 0 => SG <= "0111111"; WHEN 1 => SG <= "0000110";WHEN 2 => SG <= "1011011"; WHEN 3 => SG <= "1001111";WHEN 4 => SG <= "1100110"; WHEN 5 => SG <= "1101101";WHEN 6 => SG <= "1111101"; WHEN 7 => SG <= "0000111";WHEN 8 => SG <= "1111111"; WHEN 9 => SG <= "1101111";WHEN 10 => SG <= "1110111"; WHEN 11 => SG <= "1111100";WHEN 12 => SG <= "0111001"; WHEN 13 => SG <= "1011110";WHEN 14 => SG <= "1111001"; WHEN 15 => SG <= "1110001";WHEN OTHERS => NULL ;END CASE ;END PROCESS P3;END;五、仿真波形功能仿真波形时序仿真波形32位并进/并出移位寄存器设计一、实验原理用一个8位移位寄存器,再增加一些电路,如4个8位锁存器等,设计成为一个能为32位二进制数进行不同方式移位的移位寄存器。

二、实验步骤1、建立一个工程项目,设置路径,项目名和顶层实体名一致;2、设计一个8位移位寄存器电路;3、设计一个8位锁存器电路;4、运用元件调用声明语句和元件例化语句完成顶层设计。

三、实验程序1、八位移位寄存器程序LIBRARY IEEE;USE jicun ISPORT ( CLK,CO: IN STD_LOGIC;MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0);D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);CN : OUT STD_LOGIC);END jicun;ARCHITECTURE behav OF jicun ISSIGNAL REG : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL CY : STD_LOGIC;BEGINPROCESS(CLK,CO,MD)BEGINIF CLK'EVENT AND CLK='1' THENCASE MD ISWHEN "001"=> REG(0)<=CO;REG(7 DOWNTO 1)<= REG(6 DOWNTO 0);CY<=REG(7); WHEN "010" => REG(0)<=REG(7); ---自循环左移REG(7 DOWNTO 1)<= REG(6 DOWNTO 0);WHEN "011"=>REG(7)<=REG(0); ---自循环右移REG(6 DOWNTO 0)<=REG(7 DOWNTO 1);WHEN "100" =>REG(7)<=CO; ---带进位循环右移REG(6 DOWNTO 0)<=REG(7 DOWNTO 1);CY<=REG(0);WHEN "101" =>REG(7 DOWNTO 0)<=D(7 DOWNTO 0); --加载待移数 WHEN OTHERS=>REG<=REG;CY<=CY;--保持END CASE;END IF;END PROCESS;QB(7 DOWNTO 0)<=REG(7 DOWNTO 0);CN<=CY;END behav;2、锁存器程序library ieee ;use ;entity suocun isport(d : in std_logic_vector(7 downto 0) ;q: out std_logic_vector(7 downto 0);clk : in std_logic );end suocun ;architecture one of suocun issignal q1: std_logic_vector(7 downto 0);beginprocess(clk,q1)beginif clk'event and clk='1'thenq1<=d;end if;end process;q<=q1;end one;3、顶层设计程序LIBRARY IEEE;USE jicun32 ISPORT ( clk0,co: IN STD_LOGIC;md : IN STD_LOGIC_VECTOR(2 DOWNTO 0);db : IN STD_LOGIC_VECTOR(31 DOWNTO 0);qb : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);cn : OUT STD_LOGIC);END jicun32;ARCHITECTURE one OF jicun32 ISCOMPONENT jicunPORT ( CLK,CO: IN STD_LOGIC;MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0);D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);CN : OUT STD_LOGIC);END COMPONENT;COMPONENT suocunport(d : in std_logic_vector(7 downto 0) ;q: out std_logic_vector(7 downto 0);clk : in std_logic );END COMPONENT;SIGNAL e,f,g,h : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL l,m,n : STD_LOGIC;BEGINu1: suocun PORT MAP(d=>db(7 DOWNTO 0),q=>e,clk=>clk0);u2: jicun PORT MAP (D=>e,QB=>qb(7 DOWNTO 0),CLK=>clk0,CO=>co,CN=>l,MD=>md);u3: suocun PORT MAP(d=>db(15 DOWNTO 8),q=>f,clk=>clk0); u4: jicun PORT MAP(D=>f,QB=>qb(15 DOWNTO 8),CLK=>clk0,CO=>l,CN=>m,MD=>md);u5: suocun PORT MAP(d=>db(23 DOWNTO 16),q=>g,clk=>clk0); u6: jicun PORT MAP(D=>g,QB=>qb(23 DOWNTO 16),CLK=>clk0,CO=>m,CN=>n,MD=>md);u7: suocun PORT MAP(d=>db(31 DOWNTO 24),q=>h,clk=>clk0); u8: jicun PORT MAP(D=>h,QB=>qb(31 DOWNTO 24),CLK=>clk0,CO=>n,CN=>cn,MD=>md);END ARCHITECTURE one;四、仿真结果1、锁存器仿真2、八位寄存器仿真3、顶层设计仿真。