《EDA技术与Verilog HDL》 第5章

- 格式:pdf

- 大小:2.86 MB

- 文档页数:78

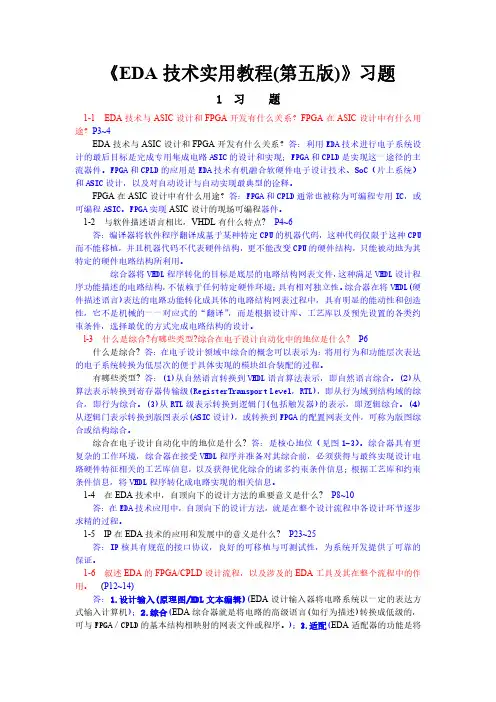

《EDA技术实用教程(第五版)》习题1习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~4EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

FPGA在ASIC设计中有什么用途?答:FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA实现ASIC设计的现场可编程器件。

1-2与软件描述语言相比,VHDL有什么特点?P4~6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU 而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P6什么是综合?答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

EDA技术实用教程-VerilogHDL版第四版课程设计一、背景介绍EDA技术(Electronic Design Automation)是指电子设计自动化技术,它是电子设计工程师在工作中必不可少的技术。

EDA技术让电子设计工程师能够更快、更准确和更高效地创建电子原型和系统级设计。

EDA技术的应用包括了芯片设计、数字信号处理、嵌入式系统和PCB设计等。

在EDA技术的发展历程中,Verilog HDL成为了实际应用中最为普及、最为有效的HDL语言。

二、课程设计目标本次课程设计的目标是通过实际案例,帮助学生掌握Verilog HDL设计方法、EDA设计流程以及EDA工具的应用,最终形成独立设计能力和技术素养。

同时,通过课程设计,提高学生综合能力,包括解决问题的能力、分析问题的能力等。

三、课程设计内容和步骤1.课程设计第一阶段:确定设计目标及功能需求在这一阶段,学生需要做的是梳理出设计要求及功能需求,包括指定设计的模块、所完成的功能、输入输出的端口要求,以及需要达到的功能性能等。

2.课程设计第二阶段:Verilog HDL设计在这一阶段,学生需要学习Verilog HDL语言,包括基础语法、模块框架、变量、运算符、组合逻辑和时序逻辑、宏定义以及模块连接等。

学生需要根据课程设计要求,选择合适的Verilog HDL代码实现方式,进行模块组件的设计。

3.课程设计第三阶段:仿真验证在这一阶段,学生需要学习EDA工具,包括ModelSim等较为流行的仿真工具的使用,运用所学工具对设计的模块组件进行仿真和测试,以验证和调试设计的正确性。

4.课程设计第四阶段:芯片布局设计、综合与验证在这一阶段,学生需要学习EDA工具,如Synopsys等较为流行的工具的应用,进行芯片综合、硬件描述语言优化、延时优化以及布局等操作,以完成设计的验证。

四、设计案例以下为一个简单的数字电路设计案例,学生可以根据这个案例进行课程设计实践。

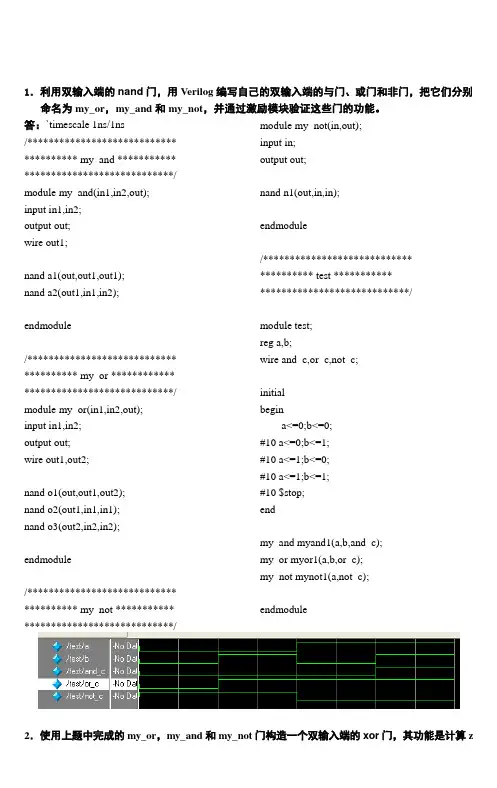

1.利用双输入端的nand门,用Verilog编写自己的双输入端的与门、或门和非门,把它们分别命名为my_or,my_and和my_not,并通过激励模块验证这些门的功能。

答:`timescale 1ns/1ns/**************************** ********** my_and *********** ****************************/ module my_and(in1,in2,out); input in1,in2;output out;wire out1;nand a1(out,out1,out1);nand a2(out1,in1,in2); endmodule/**************************** ********** my_or ************ ****************************/ module my_or(in1,in2,out);input in1,in2;output out;wire out1,out2;nand o1(out,out1,out2);nand o2(out1,in1,in1);nand o3(out2,in2,in2); endmodule/**************************** ********** my_not *********** ****************************/ module my_not(in,out);input in;output out;nand n1(out,in,in);endmodule/**************************** ********** test ***************************************/module test;reg a,b;wire and_c,or_c,not_c;initialbegina<=0;b<=0;#10 a<=0;b<=1;#10 a<=1;b<=0;#10 a<=1;b<=1;#10 $stop;endmy_and myand1(a,b,and_c);my_or myor1(a,b,or_c);my_not mynot1(a,not_c); endmodule2.使用上题中完成的my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z第5章门级建模41= x’y + x y’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真。

第1章 EDA技术概述1. EDA:EDA(Electronic Design Automation)电子设计自动化,EDA技术依赖于强大的计算机,在EDA工具软件平台上,对以HDL(Hardware Description Language--硬件描述语言)为系统逻辑描述手段完成的设计文件,自动完成逻辑化简、逻辑分割、逻辑综合、结构综合(布局布线),以及逻辑优化和仿真测试等项功能,直至实现既定性能的电子线路系统功能。

2. EDA的设计输入有:图形输入方式:原理图输入,状态图输入;HDL文本输入:VHDL,Verilog3. 常用缩写FPGA(Field Programable Gate Araay)CPLD(Complex Programmable Logic Device)ASIC(Application Specific Interated Circuit)SOC(System on a Chip)SOPC(System-on-a-Programmable-Chip)HDL(Hardware Description Language)IP(Intellectual Property)CAD(Computer Aided Design)CAM(Computer Aided Manufacturing)CAT(Computer Aided Test)CAE(Computer Aided Engineering)CAA(Computer Aided Analysis)4.综合(Synthesis):将用行为和功能层次表达的系统转换成低层次的便于具体实现的模块组合装配过程。

整个综合过程就是将设计者在EDA平台上编辑输入的HDL文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述网表文件。

5.适配:适配器也称结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如JEDEC、Jam格式的文件。

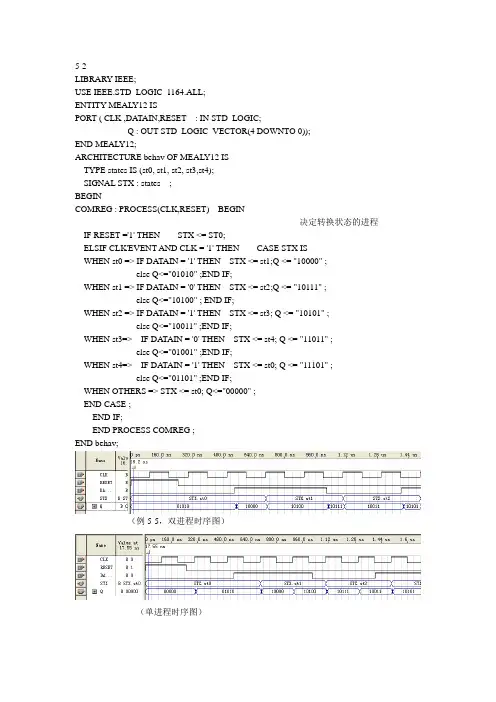

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MEALY12 ISPORT ( CLK ,DA TAIN,RESET : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(4 DOWNTO 0));END MEALY12;ARCHITECTURE behav OF MEALY12 ISTYPE states IS (st0, st1, st2, st3,st4);SIGNAL STX : states ;BEGINCOMREG : PROCESS(CLK,RESET) BEGIN--决定转换状态的进程IF RESET ='1' THEN STX <= ST0;ELSIF CLK'EVENT AND CLK = '1' THEN CASE STX ISWHEN st0 => IF DA TAIN = '1' THEN STX <= st1;Q <= "10000" ;else Q<="01010" ;END IF;WHEN st1 => IF DA TAIN = '0' THEN STX <= st2;Q <= "10111" ;else Q<="10100" ; END IF;WHEN st2 => IF DA TAIN = '1' THEN STX <= st3; Q <= "10101" ;else Q<="10011" ;END IF;WHEN st3=> IF DA TAIN = '0' THEN STX <= st4; Q <= "11011" ;else Q<="01001" ;END IF;WHEN st4=> IF DA TAIN = '1' THEN STX <= st0; Q <= "11101" ;else Q<="01101" ;END IF;WHEN OTHERS => STX <= st0; Q<="00000" ;END CASE ;END IF;END PROCESS COMREG ;END behav;(例5-5,双进程时序图)(单进程时序图)要求一:表达的是moore型状态机,特点是输出仅为当前状态的函数。

EDA技术实用教程VerilogHDL版第五版教学设计简介EDA(Electronic Design Automation),即电子设计自动化,是指利用计算机与专用软件来进行电路设计与验证、电子系统的设计、制造和测试的技术。

Verilog HDL是一种用于数字电路设计的硬件描述语言。

本教程将介绍EDA技术的实用应用和Verilog HDL的基本语法,以及实战案例的讲解。

教学目标本教学设计旨在让学生掌握以下技能:•理解EDA技术的基本原理和应用;•掌握Verilog HDL的基本语法和使用方法;•能够使用EDA工具进行数字电路设计和模拟;•了解数字电路设计的实际应用。

教学内容第一部分:EDA技术基础与实战本部分将首先介绍EDA技术的基本原理和应用,包括电路设计流程、EDA工具的选择和应用、仿真和验证技术等。

接着,将通过实例对EDA技术进行实战演练,让学生了解如何使用EDA工具进行数字电路设计和模拟。

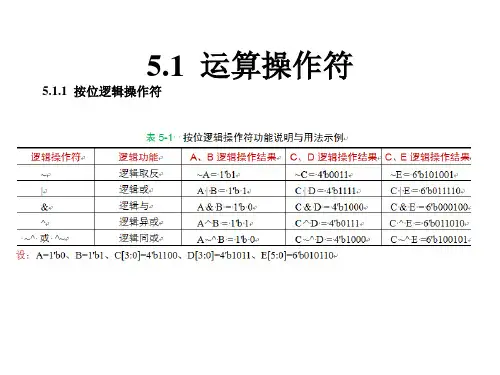

第二部分:Verilog HDL语言基础本部分将介绍Verilog HDL的基本语法和使用方法,包括模块和端口的定义、数据类型、运算符、条件语句、循环语句等。

通过实例演示,让学生掌握Verilog HDL的编写和调试技能。

第三部分:数字电路设计实践本部分将引导学生进行数字电路设计实践,包括组合逻辑和时序逻辑的设计与实现。

通过实际案例让学生了解数字电路设计的实际应用。

教学方法本教学采用以下方法:讲授法通过教师讲解,结合实例演示,让学生了解EDA技术的基本原理、VerilogHDL的基本语法和数字电路设计实践。

分组编程实践组织学生分组进行数字电路设计实践。

每个小组负责完成一个实例,组内成员协作设计实现数字电路。

实验演示通过实验演示,让学生了解数字电路设计的实际应用,增强实际操作能力。

教材及参考资料教材:•《数字电路设计与Verilog HDL》(美)Samir Palnitkar 著,王青杨林华译,电子工业出版社,2014年版。

1.利用双输入端的nand门,用Verilog编写自己的双输入端的与门、或门和非门,把它们分别命名为my_or,my_and和my_not,并通过激励模块验证这些门的功能。

答:`timescale 1ns/1ns/**************************** ********** my_and *********** ****************************/ module my_and(in1,in2,out); input in1,in2;output out;wire out1;nand a1(out,out1,out1);nand a2(out1,in1,in2); endmodule/**************************** ********** my_or ************ ****************************/ module my_or(in1,in2,out);input in1,in2;output out;wire out1,out2;nand o1(out,out1,out2);nand o2(out1,in1,in1);nand o3(out2,in2,in2); endmodule/**************************** ********** my_not *********** ****************************/module my_not(in,out);input in;output out;nand n1(out,in,in);endmodule/**************************** ********** test ***************************************/module test;reg a,b;wire and_c,or_c,not_c;initialbegina<=0;b<=0;#10 a<=0;b<=1;#10 a<=1;b<=0;#10 a<=1;b<=1;#10 $stop;endmy_and myand1(a,b,and_c);my_or myor1(a,b,or_c);my_not mynot1(a,not_c);endmodule2.使用上题中完成的my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z第5章门级建模41=x’y+x y’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真。