边界扫描介绍

- 格式:pdf

- 大小:566.65 KB

- 文档页数:9

编辑本段ICT是信息、通信和技术三个英文单词的词头21世纪初,八国集团在冲绳发表的《全球信息社会冲绳宪章》中认为:“信息通信技术是21世纪社会发展的最强有力动力之一,并将迅速成为世界经济增长的重要动力。

”事实上,信息通信业界对ICT的理解并不统一。

作为一种技术,一般人的理解是ICT不仅可提供基于宽带、高速通信网的多种业务,也不仅是信息的传递和共享,而且还是一种通用的智能工具。

至于业务会多到什么程度,这个工具会“智能”到什么地步,目前的概念还十分模糊。

三网融合只是ICT的一个基础和前奏,IPTV、手机电视等恐怕也仅仅是冰山一角而已。

对于已经吹响转型号角的固网运营商来说,目前更多地把ICT作为一种向客户提供的服务,这种服务是IT(信息业)与CT(通信业)两种服务的结合和交融,通信业、电子信息产业、互联网、传媒业都将融合在ICT的范围内。

固网运营商如中国电信为客户提供的一站式ICT整体服务中,包含集成服务、外包服务、专业服务、知识服务以及软件开发服务等。

事实上,ICT服务不仅为企业客户提供线路搭建、网络构架的解决方案,还减轻了企业在建立应用、系统升级、运维、安全等方面的负担,节约了企业运营成本,因此受到了企业用户的欢迎。

目前,IT与CT的交叉主要体现在IT企业对运营商的支撑系统的建设,值得一提的就是BOSS(Business Operating Support System),移动的称为BOSS,电信和联通的一般称为BSS。

CT企业与IT服务企业的特点比较概述在中国电信的企业战略转型指导意见中,ICT成为与互联网应用、视频内容以及移动通信并列的4大拓展业务领域之一。

ICT产生的背景是行业间的融合以及对信息通信服务的强烈诉求,而固网运营商进入ICT领域是固网空间被四处挤压、企业进入发展的疲劳甚至是衰退期下的选择,严格说来属于危机转型或弱势转型。

在转型的先驱者中,既有诺基亚这样从木材加工业成功转型到IT产业的公司,也有在转型过程中黯然落幕的百年老店AT&T。

ARM JTAG 调试原理OPEN-JTAG开发小组 1 前言这篇文章主要介绍ARM JTAG调试的基本原理。

基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原理。

这篇文章主要是总结了前段时间的一些心得体会,希望对想了解ARM JTAG调试的网友们有所帮助。

我个人对ARM JTAG的理解还不是很透彻,在文章中,难免会有偏失和不准确的地方,希望精通JTAG调试原理的大侠们不要拍砖,有什么问题提出来,我一定尽力纠正。

同时也欢迎对ARM JTAG调试感兴趣的朋友们一起交流学习。

2 IEEE Standard 1149.1 - Test Access Port and Boundary-Scan Architecture既然是介绍JTAG调试,还是让我们从IEEE的JTAG调试标准开始吧。

JTAG是JOINT TEST ACTION GROUP的简称。

IEEE 1149.1标准就是由JTAG这个组织最初提出的,最终由IEEE批准并且标准化的。

所以,这个IEEE 1149.1这个标准一般也俗称JTAG调试标准。

接下来的这一部分,主要简单的介绍了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的基本构架。

虽然不是很全面,但对了解JTAG的基本原理来说,应该是差不离了。

如果希望更全面深入的了解JTAG的工作原理,可以参考IEEE 1149.1标准。

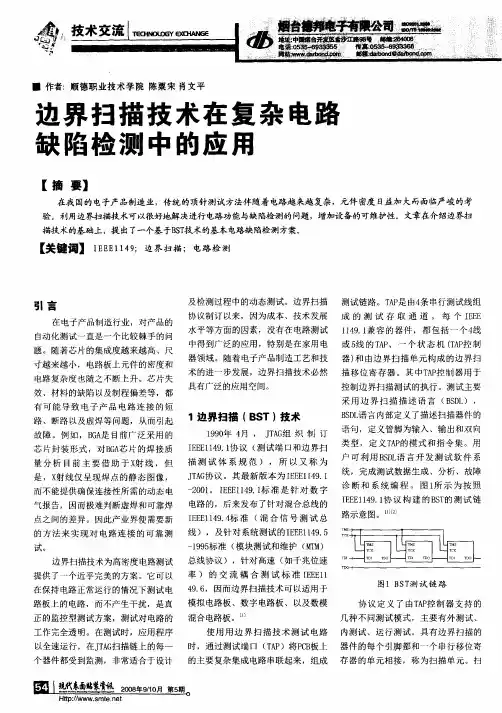

2-1 边界扫描在JTAG调试当中,边界扫描(Boundary-Scan)是一个很重要的概念。

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。

因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

电脑芯片的测试与分析方法电脑芯片是计算机硬件的核心组件之一,负责处理和执行计算机中的各种指令和数据。

在芯片的设计和制造过程中,测试和分析是确保芯片品质和性能的重要环节。

本文将介绍电脑芯片测试与分析的方法和技术。

一、功能测试功能测试是芯片测试的基本环节,用于验证芯片是否按照设计要求正常工作。

常见的功能测试方法包括边界扫描测试、功能向量测试等。

边界扫描测试是通过对芯片输入输出引脚周围的特定点进行测试,以验证芯片对输入信号的响应和输出信号的正确性。

功能向量测试则是通过输入一系列预定义的测试向量,验证芯片的各个功能是否正常工作。

二、性能测试性能测试是评估芯片性能的关键环节,通过对芯片进行负载测试,了解芯片在不同工作条件下的性能表现。

性能测试可以包括时钟频率测试、电源电流测试、功耗测试等。

时钟频率测试用于测量芯片的最高工作频率,以评估芯片的运算速度和稳定性。

电源电流测试和功耗测试则用于评估芯片在不同工作负载下的功耗情况,以确保芯片能够在正常工作范围内提供稳定的电源供应。

三、可靠性测试可靠性测试是对芯片在长时间使用过程中的可靠性进行评估的环节,可以分为温度测试、振动测试、电磁干扰测试等。

温度测试通过将芯片置于不同温度环境中,观察芯片在不同温度下的工作情况,以验证芯片在极端温度条件下的可靠性。

振动测试和电磁干扰测试则用于评估芯片在不同振动和电磁场干扰下的可靠性表现。

四、芯片分析方法芯片分析是对芯片内部结构和工作原理进行深入研究的过程,可以帮助芯片设计人员和制造商发现问题和优化设计。

常见的芯片分析方法包括扫描电镜观察、透射电镜观察、X射线衍射分析等。

扫描电镜观察可以对芯片表面和层间连接进行高分辨率观察,以发现表面缺陷和连接问题。

透射电镜观察则可以深入观察芯片内部结构和器件,以了解芯片工作原理和故障特征。

X射线衍射分析可以对芯片材料进行成分和结构分析,以确保芯片材料的质量和一致性。

综上所述,电脑芯片的测试与分析方法包括功能测试、性能测试、可靠性测试以及芯片分析方法。

集成电路测试方法研究华中科技大学IC设计中心陈新武目录摘要 (I)Abstract ················································································I I 1 序言1.1背景及其意义 (1)1.2 国内外研究现状 (3)1.3 本文的主要内容 (5)2 集成电路可测试性设计的根本概念DFT的根本概念 (6)DFT的常用方法 (6)2.3 系统芯片与IP核 (10)2.4 自动测试设备〔ATE〕 (11)2.5 集成电路可测试性设计的挑战 (12)3 边界扫描测试方法3.1 边界扫描根本状况 (14)IEEE Std 1149.1 (14)IEEE Std 1149.4 (16)IEEE Std 1149.5 (18)IEEE Std 1149.6 (20)3.6 边界扫描测试的开展前景 (22)3.7 本章小结 (22)4 全扫描可测试性实现方法4.1为什么需要扫描测试 (23)4.2可扫描单元类型 (24)4.3如何提高故障覆盖率 (28)4.4 一个实现实例 (41)4.5本章小结 (42)5 集成电路的低功耗DFT方法5.1测试模式下功耗比拟高的原因 (43)5.2基于扫描设计的低功耗DFT方法 (44)5.3基于非扫描设计的低功耗DFT方法 (47)5.4本章小结 (52)6 测试调度问题6.1为测试调度问题建立数学模型 (53)’02 (56)6.3测试调度算法 (61)6.4实验数据的构造 (64)6.5实验结果与分析 (65)6.6本章小结 (66)7 总结与展望7.1 总结 (68)7.2 本文的创新点 (69)7.3 展望 (69)参考文献 (72)附录1 一个测试基准举例 (78)1 序言本课程目的在于研究集成电路的测试实现方法,可以用于指导集成电路的设计工作。

DFT,可测试性设计--概念理解⼯程会接触DFT。

需要了解DFT知识,但不需要深⼊。

三种基本的测试(概念来⾃参考⽂档):1. 边界扫描测试:Boundary Scan Test: 测试⽬标是IO-PAD,利⽤JTAG接⼝互连以⽅便测试。

(jtag接⼝,实现不同芯⽚之间的互连。

这样可以形成整个系统的可测试性设计)2. 内建⾃测试BIST:(模拟IP的关键功能,可以开发BIST设计。

⼀般情况,BIST造成系统复杂度⼤⼤增加。

memory IP⼀般⾃带BIST,简称MBIST)3. 扫描测试(ATPG)Scan path: 与边界扫描测试的区别,是内部移位寄存器实现的测试数据输⼊输出。

测试⽬标是std-logic,即标准单元库。

(扫描测试和边界扫描,不是⼀个概念。

需要区别对待。

内部的触发器,全部要使⽤带SCAN功能的触发器类型。

)补充:还有⼀种测试:4. 全速测试at-speed-test(其实是属于扫描测试的⼀种。

只不过测试时钟来源频率更快。

)at-speed 就是实速测试,主要⽤于scan测试-即AC测试和mbist测试。

这种测试⼿段的⽬的是-测试芯⽚在其⼯作频率下是否能正常⼯作,实速即实际速度。

测试时钟往往是由芯⽚内部的PLL产⽣很快的测试时钟,⽤于实速测试。

相对⽽⾔,⼀般的测试是20~40兆的测试时钟,频率低,测不到transition fault。

即使测试通过,实际使⽤中还会由于使⽤⾼频时钟发⽣芯⽚电路故障。

常见的DFT/OCC结构如下:特点:1. Clock MUX必须放在OCC模块/DFT MUX之前。

(OCC:On Chip Clock)2. 时钟⼤于50MHz时,使⽤OCC模块,否则使⽤DFT MUX。

3. Clock Gate放在OCC模块/DFT MUX之后。

4. 对于⼿动添加的Clock Gate,DFT_SE端⼝接到 dft_glb_gt_se。

5. 对于综合⼯具添加的Clock Gate,DFT_SE端⼝接到dft_syn_gt_se注意:1. DFT_MODE有效时,clock mux的sel信号要保证dft_clk来源于最⾼频率的时钟源。

三坐标测量机(CMM)的测量方式通常可分为接触式测量、非接触式测量和接触与非接触并用式测量。

其中,接触测量方式常用于机加工产品、压制成型产品、金属膜等的测量。

为了分析工件加工数据,或为逆向工程提供工件原始信息,经常需要用三坐标测量机对被测工件表面进行数据点扫描。

本文以美国Brown & Sharpe公司Microxcel Pfx454型三坐标测量机为例,介绍三坐标测量机的几种常用扫描方法及其操作步骤。

?三坐标测量机的扫描操作是应用PC?DMIS程序在被测物体表面的特定区域内进行数据点采集,该区域可以是一条线、一个面片、零件的一个截面、零件的曲线或距边缘一定距离的周线等。

扫描类型与测量模式、测头类型以及是否有CAD文件等有关,控制屏幕上的“扫描”(Scan)选项由状态按钮(手动/DCC)决定。

若采用DCC方式测量,又有CAD文件,则可供选用的扫描方式有“开线”(Open Linear)、“闭线”(Closed Linear)、“面片”(Patch)、“截面”(Section)和“周线”(Perimeter)扫描;若采用DCC方式测量,而只有线框型CAD 文件,则可选用“开线”(Open Linear)、“闭线”(Closed Linear)和“面片”(Patch)扫描方式;若采用手动测量模式,则只能使用基本的“手动触发扫描”(Manul TTP Scan)方式;若采用手动测量方式并使用刚性测头,则可用选项为“固定间隔”(Fixed Delta)、“变化间隔”(Variable Delta)、“时间间隔”(Time Delta)和“主体轴向扫描”(Body Axis Scan)方式。

?下面详细介绍在DCC状态下,进入“功能”(Utility)菜单选取“扫描”(Scan)选项后可供选择的五种扫描方式。

?1.开线扫描(Open Linear Scan)开线扫描是最基本的扫描方式。

测头从起始点开始,沿一定方向并按预定步长进行扫描,直至终止点。

iMPACT简介1.iMPACT简介iMPACT 支持4种下载模式:边界扫描,从串模式、SelectMap模式以及Desktop配置模式。

从串模式是一种常用配置电路,可用USB口或并口完成配置。

SelectMap模式是一种并行配置模式,速度快,但需要使用多个信号管脚。

Desktop模式是一种高速配置模式,可配置FPGA、 PROM以及SystemACE,但需要专用的硬件设备。

在实际中,由于边界扫描模式标准统一、设备简单,且可通过JTAG链路配置FPGA、CPLD以 及PROM,使用最为广泛。

因此本节主要基于边界扫描模式来介绍IMPACT的使用方法。

当设计完成后,ISE调用BitGEN程序把布局布 线后的.ncd文件转化成.bit 文件,包括了配置数据和配置指令。

如果使用JTAG模式,可直接将.bit文件通过iMPACT文件配置到FPGA芯片 中。

如果要用其它模式配置FPGA,则需要通过iMPACT进行格式转化,生成.mcs、.exo 以及.hex等文件格式,表M对常用的配置文件进行比较和说明。

表5-19 常用的Xilixn FPGA配置文件格式列表对于FPGA器件,iMPACT能够直接将.bit位流文件下载到芯片中,或者将其转换为PROM器件的EXO/MCS文件格式,并下载到PROM芯片中。

2.iMPACT用户界面有 两种方法可以启动iMPACT软件,一种是在ISE过程管理区中,点击Generate Programming File前面的“+”号,再双击“Configure Device”,在ISE环境下运行;另一种是通过点击“开始 程序 ISE9.1 Accessories iMPACT”,在Windows环境下单独运行。

其用户界面如图M所示。

图5-35 iMPACT的用户界面iMPACT的用户界面主要由File、Edit、View、Operations、Options、Output、Debug、Window、Help菜单栏和常用工具栏组成。

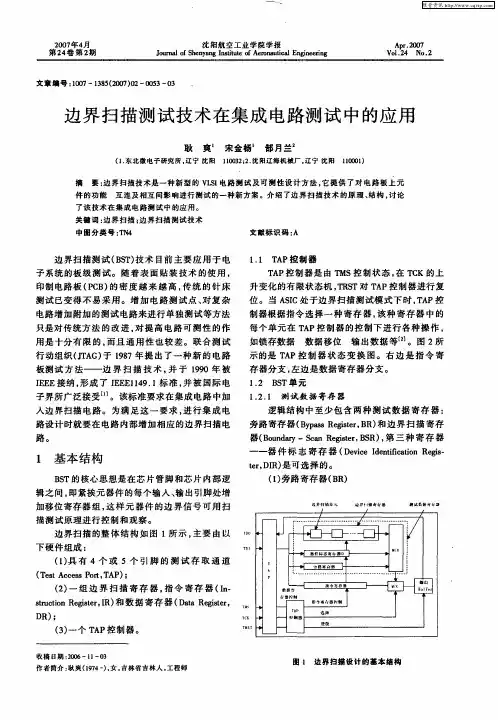

NoC边界扫描测试系统硬件设计全钊锋【摘要】为了解决内部结构日益复杂的片上网络系统故障测试的问题,在研究3×32D-Mesh体系结构的NoC系统、边界扫描测试技术和资源节点故障类型的基础上,以FPGA为核心器件设计边界扫描测试系统。

完成了数据采集、频率计、放大器、 SRAM、 IEEE1500 Wrapper等资源节点电路以及资源节点边界扫描链路的接口电路设计,并利用测试软件、信号发生器、万用表和数字示波器,通过边界扫描链路完成对整个硬件设计的测试。

测试结果表明该设计性能稳定,为研究NoC系统的边界扫描测试技术提供了硬件平台。

%A boundary scan test system is designed with FPGA as the core for fault testing of complex network on chip systems based on 3 ×3 2D-Mesh structure of NoC system, the boundary scan test technology and the resource node fault types.The frequency meter, amplifier, SRAM, IEEE1500 Wrapper and the boundary scanning chains of resource nodes interface are implemented.The test software, signal generator, AVO meter, digital oscilloscope are used to checkout the whole hardware design through boundary chain.The test results show that the design offers sta-ble performance and provides a hardware platform of boundary scan test in the research of NoC systems.【期刊名称】《电子科技》【年(卷),期】2015(000)009【总页数】4页(P63-66)【关键词】片上网络;FPGA;边界扫描;硬件平台【作者】全钊锋【作者单位】桂林电子科技大学电子工程与自动化学院,广西桂林 541004【正文语种】中文【中图分类】TN47片上网络(Network-on-Chip,NoC)是专门用于芯片内部互连的通信网络,它借鉴了计算机网络中分组交换的通信方法,可以根据应用灵活地采用多种网络拓扑结构互连片上系统或者IP核[1]。