边界扫描测试原理与应用

- 格式:ppt

- 大小:4.14 MB

- 文档页数:30

Boundary Scan测试原理及实现什么是边界扫描(boundary scan)?什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器(TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register 和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

在不了解Boundary scan的目的:Boundary scan是一种用于测试数字集成电路的技术,它能找出,开路,短路,和功能不良的数字器件,另外它还能完成一些功能测试。

边界扫描测试原理边界扫描测试是一种黑盒测试方法,其中测试人员专注于程序的边界条件。

该方法旨在检测程序在处理边界条件时是否存在问题,例如程序的最大和最小输入值,以及输入值与最大和最小值之间的情况。

边界扫描测试方法适用于各种程序,包括软件应用程序、Web应用程序和嵌入式系统等。

边界扫描测试方法可以确保程序在处理边界条件时具有正确的行为,并且不会出现错误或异常情况。

这种测试方法可以帮助测试人员发现程序的潜在缺陷,并且可以改进程序的质量和可靠性。

边界扫描测试方法通常包括以下步骤:1. 确定输入值的最大和最小值测试人员需要确定程序所期望的最大和最小输入值。

这可以通过查看程序的规范或文档来实现。

如果程序没有明确的规范或文档,则测试人员需要自己确定最大和最小值。

2. 确定输入值与最大和最小值之间的情况测试人员需要确定输入值与最大和最小值之间的情况。

例如,如果程序要求输入数字,则测试人员需要确定输入数字的最大和最小值,并确定输入数字与这些值之间的情况。

3. 编写测试用例测试人员需要编写测试用例来测试程序的边界条件。

测试用例应包括最大和最小输入值以及输入值与最大和最小值之间的情况。

测试用例应覆盖所有可能的情况,并且应该能够测试程序的所有功能。

4. 运行测试用例测试人员需要运行测试用例并记录测试结果。

如果测试用例中出现错误或异常情况,则测试人员需要将其记录下来并报告给开发人员。

5. 分析测试结果测试人员需要分析测试结果,并确定程序在处理边界条件时是否存在问题。

如果存在问题,则测试人员需要将其报告给开发人员,并协助开发人员解决问题。

总结边界扫描测试方法是一种有效的黑盒测试方法,可以帮助测试人员发现程序在处理边界条件时的潜在缺陷,并改进程序的质量和可靠性。

边界扫描测试方法需要测试人员确定输入值的最大和最小值,并编写测试用例来测试程序的边界条件。

测试人员需要运行测试用例,并记录测试结果。

最后,测试人员需要分析测试结果,并将问题报告给开发人员。

jtag边界扫描的概念

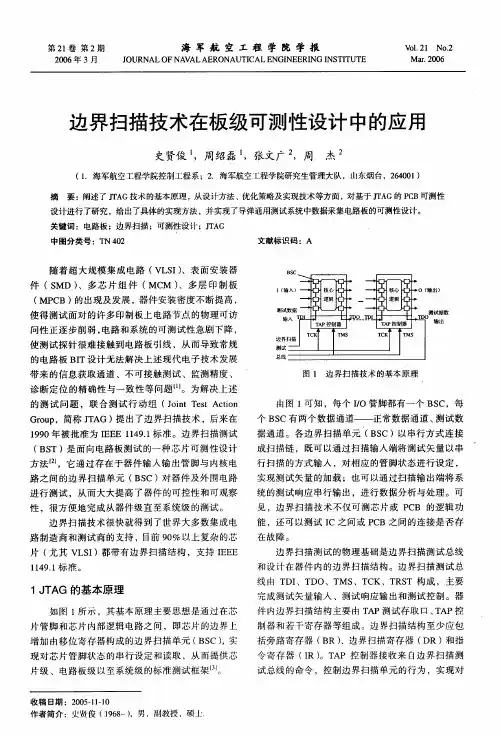

边界扫描(Boundary Scan)是一种测试技术,用于在集成电路板内进行测试,特别是对于那些无法通过传统的测试方法进行测试的复杂电路板。

它利用在每个芯片的输入输出管脚上增加的移位寄存器单元(Boundary-Scan Register Cell),这些寄存器单元分布在芯片的边界上,被称为边界扫描寄存器。

在JTAG调试中,边界扫描是一个非常重要的概念。

当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制。

对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。

正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

它可以串行地输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制。

一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过TAP(Test Access Port)Controller来完成。

以上内容仅供参考,如需更多信息,建议查阅相关文献或咨询专业人士。

边界扫描测试系统一、IEEE1149.1产生的背景当今电子制造商正面临着越来越大的降低成本、提高质量及缩短生产周期的压力,电路板越来越密、器件越来越复杂、电路性能要求也越来越苛刻,这一切直接导致了电子器件的生产商和电子产品的制造商都在倾向于采用最新的器件技术,如GA、CSP、TCP 等更小的封装,以更小的体积提供更强的功能。

但是随之而来的接入问题却日益成为测试的巨大障碍。

为了解决此类问题,IEEE1149.1———边界扫描测试技术应运而生。

二、边界扫描测试的原理边界扫描测试是一种可测试结构技术,它采用集成电路的内部外围所谓的“电子引脚”(边界)模拟传统的在线测试的物理引脚,对器件内部进行扫描测试。

它是在芯片的I/O端上增加移位寄存器,把这些寄存器连接起来,加上时钟复位、测试方式选择以及扫描输入和输出端口,而形成边界扫描通道。

IEEE1149.1标准规定了一个四线串行接口(第五条线是可选的),该接口称作测试访问端口(TAP),用于访问复杂的集成电路(IC),例如微处理器、DSP、ASIC 和CPLD等。

在TDI(测试数据输入)引线上输入到芯片中的数据存储在指令寄存器中或一个数据寄存器中。

串行数据从TDO(测试数据输出)引线上输出。

边界扫描逻辑由TCK(测试时钟)上的信号计时,而且TMS(测试模式选择)信号控制驱动TAP控制器的状态。

TRST*(测试重置)是可选项,可作为硬件重置信号,一般不用。

详细边界扫描结构及信号流程参考图1。

图1中“TAP Controller”其实质上是一个状态切换到6个不同的状态,具体状态逻辑参考图2。

从一个状态切换成另一个状态总是发生在TCK的上升沿,由TMS 从两个状态选择其中一个状态。

在测试向量寄存器中,既有指令寄存器(IR),又有数据寄存器(DR),而且,为了区分是指令还是数据,扫描链路中的状态图有两个独立的完全类似的结构(Scan DR/ Scan IR)。

测试操作的最重要步骤是移入和同步移出测试数据(DR SHIFT),新的数据进入移位链,测试数据传送到测试单元DR-update)的输出锁存器中,对于指令寄存器(IR-shift,IR-capture,IR-update)同样如此。

boundaryscan应用实例-回复什么是boundary scan技术?Boundary scan技术,又称JTAG(Joint Test Action Group)技术,是一种用于芯片级电路板测试和诊断的技术。

它使用了IEEE标准1149.1定义的边界扫描链(Boundary Scan Chain),通过在电路板上的闩锁功能来实现对芯片上的引脚的测试和调试。

Boundary scan技术的原理和功能如何工作?Boundary scan技术的原理基于一种边界扫描链结构(Boundary Scan Chain),该链将所有芯片引脚连接起来形成一个环。

这个环具有使能信号和测试控制信号,通过这些信号的控制,可以将测试数据从一个引脚传输到另一个引脚,实现对芯片引脚的测试和调试。

Boundary scan技术的功能主要有以下几个方面:1. 电路连通性测试:通过boundary scan技术,可以检测和诊断电路板上信号线的连通性是否良好,以及是否存在断路和短路。

2. 引脚功能测试:通过boundary scan技术,可以实时测试和诊断芯片引脚的功能是否正常。

这对于芯片级的调试和故障排除非常有用。

3. 元件配置和诊断:通过boundary scan技术,可以识别和配置电路板上的各种元件,例如存储器、逻辑门等。

这可以帮助工程师更好地了解电路板的组成和功能。

4. 容错性检查:通过boundary scan技术,可以检查电路板上的信号线是否遵循电气特性,例如正确的电阻和电容值。

这对于确保电路板的稳定性和可靠性至关重要。

Boundary scan技术的应用实例1. 电子设备制造:Boundary scan技术可以在生产线上用于测试和验证电子设备的电路板,以确保其质量和可靠性。

它可以有效地检测和排除电路板上的连通性问题和故障,提高生产效率和产品质量。

2. 电路板维修:当电子设备发生故障时,boundary scan技术可以用于定位和修复故障点。

IEEE1149.1标准是一项用于测试和故障诊断集成电路的重要标准,而JTAG(Joint Test Action Group)是这项标准的主要推动者之一。

本文将对IEEE1149.1标准进行解析,从其定义、原理、应用等多个角度进行分析,帮助读者更好地理解和应用这一标准。

一、 IEEE1149.1标准的定义IEEE1149.1标准,也称为边界扫描标准或JTAG标准,是一项由IEEE 制定的用于测试集成电路的标准。

该标准于1990年发布,已被广泛应用于半导体工业、电子制造业等领域。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试和调试,从而提高了集成电路的可靠性和稳定性。

二、 IEEE1149.1标准的原理1. 边界扫描链IEEE1149.1标准的核心是边界扫描链(boundary scan ch本人n),通过在集成电路的引脚上添加扫描逻辑,实现了对芯片内部连接和状态的测试。

这种边界扫描链可以将芯片的内部引脚与外部引脚进行连接,从而实现对芯片内部信号的观测和控制。

2. TAP控制器IEEE1149.1标准还引入了TAP(Test Access Port)控制器,用于与边界扫描链进行通信和控制。

TAP控制器可以对边界扫描链进行初始化、数据传输和状态控制,从而实现对集成电路的测试和调试。

三、 IEEE1149.1标准的应用1. 芯片测试IEEE1149.1标准最主要的应用是用于集成电路的测试。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试,从而发现潜在的故障和缺陷。

2. 芯片调试除了测试功能,IEEE1149.1标准还可以用于集成电路的调试。

通过边界扫描链和TAP控制器,工程师可以对集成电路进行状态观测和信号控制,从而快速定位和分析故障原因。

3. 芯片编程IEEE1149.1标准还可以用于集成电路的编程。

一些可编程逻辑器件(如FPGA)可以通过边界扫描信息口进行编程,实现对逻辑器件内部配置和状态的控制。

1边界扫描测试技术原理2.边界扫描指令集Extest指令--强制指令用于芯片外部测试,如互连测试测试模式下的输出管脚,由BSC update锁存驱动BSC scan锁存捕获的输入数据移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存原先EXTEST指令是强制为全“0”的,在IEEE 1149.1—2001中,这条强制取消了。

选择边界扫描寄存器连通TDI和TDO。

在这种指令下,可以通过边界扫描输出单元来驱动测试信号至其他边界扫描芯片,以及通过边界扫描输入单元来从其他边界扫描芯片接受测试信号。

EXTEST指令是IEEE 1149.1标准的核心所在,在边界扫描测试中的互连测试(interconnect test)就是基于这个指令的。

Sample/Preload指令编辑Sample/Preload指令--强制指令在进入测试模式前对BSC进行预装载输入输出管脚可正常操作输入管脚数据和内核输出数据装载到BSC的scan锁存中。

移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存。

原先这两个指令是合在一起的,在IEEE 1149.1--2001中这两个指令分开了,分成一个SAMPLE指令,一个PRELOAD指令。

选择SAMPLE/PRELOAD指令时,IC工作在正常工作模式,也就是说对IC的操作不影响IC的正常工作。

选择边界扫描寄存器连通TDI和TDO。

SAMPLE指令---通过数据扫描操作(Data Scan)来访问边界扫描寄存器,以及对进入和离开IC的数据进行采样。

PRELOAD指令---在进入EXTEST指令之前对边界扫描寄存器进行数据加载。

Bypass指令编辑Bypass指令--强制指令提供穿透芯片的最短通路。

输入输出管脚可正常操作选择一位的旁路(Bypass)寄存器强制全为1和未定义的指令为Bypass指令BYPASS指令为全“1”。

边界扫描测试方法

嘿,咱今儿来聊聊边界扫描测试方法呀!这玩意儿可神奇啦,就像是给电子设备做了一次全面又精细的体检。

你想啊,一个电子设备里面那么多复杂的电路和元器件,就好像是一个庞大的迷宫。

那怎么才能知道这个迷宫里有没有问题呢?边界扫描测试方法就派上用场啦!它就像是一个超级侦探,能一点点地去排查每一个角落。

它是通过在芯片的边界上设置一些特殊的引脚来实现的。

这些引脚就像是一个个小眼睛,能观察到芯片内部的情况。

比如说,它可以检测芯片之间的连接是否正常,有没有短路或者开路的情况。

这多重要啊,要是连接有问题,那整个设备不就乱套啦!

而且哦,边界扫描测试方法还特别灵活。

它可以根据不同的需求和情况,进行各种不同的测试。

就好像你有一套工具,你可以根据要修的东西不同,选择不同的工具来干活儿。

它还能帮助我们在生产过程中及时发现问题。

你想想,要是生产了一大批产品,最后才发现有问题,那得多麻烦,多浪费啊!但有了边界扫描测试方法,就能早早地把问题揪出来,及时解决,多省心啊!

这就好比是我们出门前要照照镜子,看看自己有没有穿戴整齐。

边界扫描测试方法就是给电子设备照镜子,确保它们能以最好的状态工作。

它还能提高设备的可靠性呢!就像我们锻炼身体,让自己更强壮,不容易生病一样。

通过边界扫描测试,能让设备更稳定地运行,减少出故障的概率。

咱再想想,要是没有这个方法,那电子设备出问题了可咋办?那可就像没头苍蝇一样,不知道从哪儿开始找问题啦!所以说,边界扫描测试方法真的是太重要啦!它是电子设备领域的好帮手,是保障设备正常运行的关键一环啊!大家可千万别小瞧了它哟!。

什么是边界扫描(boundary scan)?Boundary Scan测试原理及实现JTAG标准的IC芯片结构IEEE 1149.1 标准背景JTAG什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

dft的测试方法DFT的测试方法概述DFT(Design for Testability,测试性设计)是一种设计方法,旨在确保电子设备的可测试性和可靠性。

它包括在设计过程中引入测试功能,以便更容易地检测和诊断设备的故障。

本文将介绍DFT的测试方法,并探讨其在电子设备制造过程中的重要性和应用。

1.扫描链测试扫描链测试是DFT中最常用的测试方法之一。

它通过在设计中引入扫描链,将电路分成多个扫描链,使得测试信号可以从输入端口进入电路,然后通过扫描链输出。

这种方法可以大大简化测试过程,提高测试覆盖率和效率。

同时,扫描链测试还可以检测到电路中的短路、开路和延迟故障等问题。

2.边界扫描测试边界扫描测试是一种用于测试集成电路(IC)边界的DFT技术。

它通过在IC设计中引入边界扫描链,将输入和输出端口与边界扫描链相连接,从而实现对IC边界的测试。

边界扫描测试可以有效地测试IC边界上的逻辑和电气特性,并提供高测试覆盖率和可靠性。

3.存储器BIST测试存储器BIST(Built-In Self-Test,内建自测试)是一种用于测试存储器的DFT技术。

它通过在存储器中内置测试电路和算法,实现存储器的自测试。

存储器BIST测试可以在芯片制造过程中自动进行,无需外部测试设备,大大提高了测试效率和可靠性。

4.电路自适应测试电路自适应测试是一种基于DFT的自适应测试方法。

它通过在电路中引入自适应测试电路,实现对电路的自动测试和故障诊断。

电路自适应测试可以根据电路的实际工作状态和测试需求,自动选择最佳的测试算法和参数,提高测试效率和准确性。

5.故障模拟测试故障模拟测试是一种基于DFT的故障检测方法。

它通过在设计中引入故障模拟电路,模拟故障情况,然后利用模拟结果进行故障检测和诊断。

故障模拟测试可以帮助设计人员了解电路的故障情况,优化设计和测试策略,提供更可靠的电子设备。

6.片上监测测试片上监测测试是一种用于监测电子设备工作状态的DFT技术。