边界扫描测试技术(课件)

- 格式:ppt

- 大小:1.79 MB

- 文档页数:19

IEEE1149.1-1990标准,要求在集成电路中加入边界扫描电路,在板级测试时,可以在主控器的控制下,构成一条在集成电路边界绕行的移位寄存器链,对板内集成电路的所有引脚进行扫描,通过将测试数据串行输入到该寄存器链的方法,检查发现PCB上的器件焊接故障和板内连接故障。

IEEE1149.1定义了边界扫描器件的四线测试访问端口(TAP):TDI、TDO、TCK、TMS,常称为JTAG接口。

TDI(测试数据输入)、TDO(测试数据输出)、TCK(测试时钟)、TMS (测试模式选择)。

TAP控制器支持的几种测试模式:外测试,内测时,运行测试等等。

具有边界扫描功能器件的每一个引脚都与一个串行移位寄存器(SSR)的单元相接,称为边界扫描单元。

边界扫描单元连在一起构成一个移位寄存器链,用于控制和检测器件引脚。

IEEE1149.1标准测试结构:TAP、TAP控制器、指令寄存器和数据寄存器。

TAP控制器由TCK和TMS控制。

在测试逻辑内部,一系列边界扫描指令寄存器以及解码逻辑处于TAP控制器控制之下,并将TDI信号经过可控的延迟之后从TDO输出。

指令寄存器用于设置数据寄存器(Data Register)的工作模式。

有两种数据寄存器必须存在,一是旁路寄存器(Bypass Register),而是边界寄存器(Boundary Register)。

TAP控制器:包含16个状态的有限状态机,由TCK上升沿采样的TMS状态来控制。

指令寄存器:指令寄存器由串行移位寄存器和并行锁存寄存器组成,长度等于器件边界扫描测试指令的长度。

指令寄存器的行为由TAP控制器的状态决定,根据移入指令的内容将某一数据寄存器连接到TDI和TDO之间。

在进行测试操作时,测试指令首先经TDI移入指令寄存器,然后送入指令锁存器,最后TAP控制器将锁存器中的指令译码后,配合其输出信号来控制其它扫描逻辑。

数据寄存器:1.旁路寄存器不需要并行锁存寄存器,且长度只由1位。

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified astrademarks or service marks are the property of their respective holders as described at /common/legal.html . Altera warrants performance of itssemiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products andservices at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or servicedescribed herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.Cyclone IV 器件手册,卷12011年11月SubscribeISO 9001:2008 Registered 10.Cyclone IV 器件的JTAG 边界扫描测试本章介绍了Cyclone ®IV 器件所支持的边界扫描测试(BST)功能。

边界扫描背景:早在1985年,几家欧洲的厂商为解决高复杂度IC的测试问题,成立了一个JETAG(Joint European Test Action Group)的组织。

稍后,包含HP(Hewlett Packard)及一些美商公司亦加入了这个组织,该组织更名为JTAG(Joint Test Action Group)。

JTAG发展了BOUNDARY-SCAN 的技术,并于1989年将BOUNDARY-SCAN 的JTAG Rev 2.0 版,移转给电机电子工程师协会(Institute Electrical and Electronic Engineers, IEEE),并于1990年成为IEEE Standard1149.1-1990。

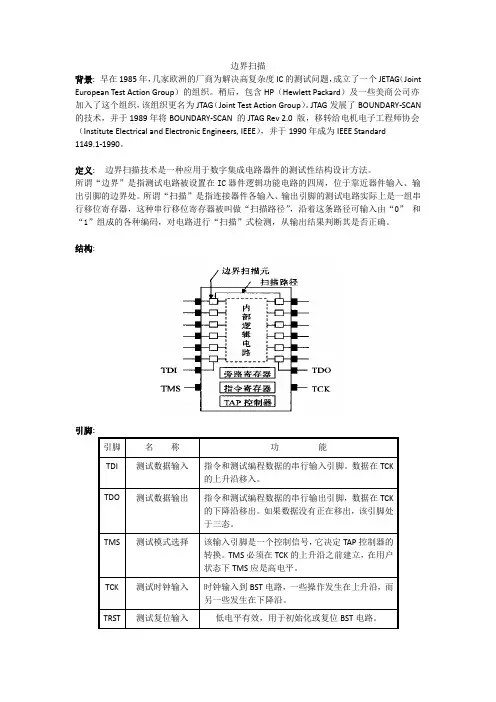

定义:边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。

所谓“边界”是指测试电路被设置在IC器件逻辑功能电路的四周,位于靠近器件输入、输出引脚的边界处。

所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一组串行移位寄存器,这种串行移位寄存器被叫做“扫描路径”,沿着这条路径可输入由“0” 和“1”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确。

结构:引脚:寄存器:1指令寄存器:用来决定是否进行扫描测试和访问数据寄存器操作。

2旁路寄存器:旁路寄存器只有1位,它提供了一条从TDI到TDO之间的最短通道。

当选择了旁路寄存器,实际上没有执行边界扫描测试,它的作用是为了缩短扫描路径,将不需要测试的数据寄存器旁路掉,以减少不必要的扫描时间。

3边界扫描寄存器边界扫描寄存器由大量置于集成电路输入输出引脚附近的边界扫描单元组成。

边界扫描单元首尾相连构成一个串行移位寄存器链,它使用TDI引脚作为输入,TDO引脚作为输出。

在测试时钟TCK的作用下,从TDI加入的数据可以在边界扫描寄存器中进行移动扫描。

设计人员可用边界扫描寄存器来测试外部引脚的连接,或是在器件运行时捕获内部数据。

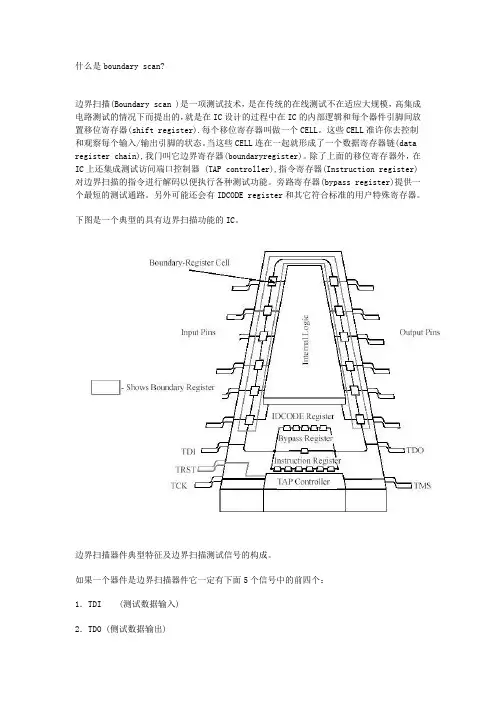

什么是boundary scan?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

下图是一个典型的具有边界扫描功能的IC。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)测试访问端口控制器(TAP controller)TMS,TCK,TRST构成了边界扫描的测试访问端口控制器(TAP controller)。

TAP (the test access port)是一个通用的端口,用来引入控制信号到边界扫描器件(TCK,TMS,TRST*)并且为边界扫描提供串行的输入,输出信号(TDI,TDO)TAP controller是一个16位的状态机,可以通过TMS(test mode selection)和TCK(test clock input)对TAP controller进行编程控制它的状态,TAP controller控制进入指令寄存器(instruction register)和数据寄存器(data register)数据流。

1边界扫描测试技术原理2.边界扫描指令集Extest指令--强制指令用于芯片外部测试,如互连测试测试模式下的输出管脚,由BSC update锁存驱动BSC scan锁存捕获的输入数据移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存原先EXTEST指令是强制为全“0”的,在IEEE 1149.1—2001中,这条强制取消了。

选择边界扫描寄存器连通TDI和TDO。

在这种指令下,可以通过边界扫描输出单元来驱动测试信号至其他边界扫描芯片,以及通过边界扫描输入单元来从其他边界扫描芯片接受测试信号。

EXTEST指令是IEEE 1149.1标准的核心所在,在边界扫描测试中的互连测试(interconnect test)就是基于这个指令的。

Sample/Preload指令编辑Sample/Preload指令--强制指令在进入测试模式前对BSC进行预装载输入输出管脚可正常操作输入管脚数据和内核输出数据装载到BSC的scan锁存中。

移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存。

原先这两个指令是合在一起的,在IEEE 1149.1--2001中这两个指令分开了,分成一个SAMPLE指令,一个PRELOAD指令。

选择SAMPLE/PRELOAD指令时,IC工作在正常工作模式,也就是说对IC的操作不影响IC的正常工作。

选择边界扫描寄存器连通TDI和TDO。

SAMPLE指令---通过数据扫描操作(Data Scan)来访问边界扫描寄存器,以及对进入和离开IC的数据进行采样。

PRELOAD指令---在进入EXTEST指令之前对边界扫描寄存器进行数据加载。

Bypass指令编辑Bypass指令--强制指令提供穿透芯片的最短通路。

输入输出管脚可正常操作选择一位的旁路(Bypass)寄存器强制全为1和未定义的指令为Bypass指令BYPASS指令为全“1”。

边界扫描测试方法

嘿,咱今儿来聊聊边界扫描测试方法呀!这玩意儿可神奇啦,就像是给电子设备做了一次全面又精细的体检。

你想啊,一个电子设备里面那么多复杂的电路和元器件,就好像是一个庞大的迷宫。

那怎么才能知道这个迷宫里有没有问题呢?边界扫描测试方法就派上用场啦!它就像是一个超级侦探,能一点点地去排查每一个角落。

它是通过在芯片的边界上设置一些特殊的引脚来实现的。

这些引脚就像是一个个小眼睛,能观察到芯片内部的情况。

比如说,它可以检测芯片之间的连接是否正常,有没有短路或者开路的情况。

这多重要啊,要是连接有问题,那整个设备不就乱套啦!

而且哦,边界扫描测试方法还特别灵活。

它可以根据不同的需求和情况,进行各种不同的测试。

就好像你有一套工具,你可以根据要修的东西不同,选择不同的工具来干活儿。

它还能帮助我们在生产过程中及时发现问题。

你想想,要是生产了一大批产品,最后才发现有问题,那得多麻烦,多浪费啊!但有了边界扫描测试方法,就能早早地把问题揪出来,及时解决,多省心啊!

这就好比是我们出门前要照照镜子,看看自己有没有穿戴整齐。

边界扫描测试方法就是给电子设备照镜子,确保它们能以最好的状态工作。

它还能提高设备的可靠性呢!就像我们锻炼身体,让自己更强壮,不容易生病一样。

通过边界扫描测试,能让设备更稳定地运行,减少出故障的概率。

咱再想想,要是没有这个方法,那电子设备出问题了可咋办?那可就像没头苍蝇一样,不知道从哪儿开始找问题啦!所以说,边界扫描测试方法真的是太重要啦!它是电子设备领域的好帮手,是保障设备正常运行的关键一环啊!大家可千万别小瞧了它哟!。

边界扫描测试技术(04-100)

最近出现的系统级接口器件,为设计人员把用于制造测试的边界扫描测试从板级扩展到系统级提供了灵活条件。

扩展到系统级的基础结构是提供单点接入到多扫描链,以支持隔离的诊断能力。

这可以用于CPLD和FPGA系统内配置的最佳化,以及编程闪存时存储器读/写周期的最佳化。

它也支持板到板内连测试(用于背投内连失效诊断)到端口连接器引脚级。

另一个优点是在产品装运前提供系统测试,这包括固件检验和简化固件更新。

扩展边界扫描到系统级提供执行嵌入式测试结构(即器件级BIST)的基础结构,这可在EPGA、ASIC和SoC中实现。

另外,它提供单点接入能力来支持环境重点测试和精确的引脚级诊断。

拓扑结构

选择边界扫描系统结构对于路由TAP测试接入端口是重要的,并将确定选择哪些系统级器件。

有三种主要的TAP路由方式:ring(环状)star(星状)multi- drop(多分接)

当然,多分接方式是最广泛用于可靠系统控制的。

在这种方式中,5个主要的IEEE1149.1测试接入信号(TCK,TMS,TDI,TDD,TEST)并联连接到系统配置的所有背板槽中。

多分接配置中的每个槽都有一个专门的地址,槽地址多达64/128个专门地址,通常,这些地址在背板中用硬线连接(见图1)

通过总体扫描链的TDI信号线,广播每个板的专门背板地址来接入系统中的每块板。

对应于广播地址的置于槽中的板,将唤醒并允许接入到本地扫描。

用边界扫描技术检测非边扫器件I. 引言- 简述非边扫描器件的概念及应用背景- 阐述目前检测非边扫描器件所面临的困难和挑战II. 综述边界扫描技术- 介绍边界扫描技术的基本原理和特点- 讨论边界扫描技术在检测集成电路中的应用情况III. 基于边界扫描技术的非边扫描器件检测方案- 提出基于边界扫描技术的非边扫描器件检测方案- 阐述该方案的实现方法IV. 方案实验与结果分析- 设计实验样本集并进行实验测试- 分析实验结果,评估方案的检测能力和鲁棒性V. 结论- 总结该非边扫描器件检测方案的优势和局限性- 展望该方案在未来的应用前景及发展方向附:参考文献边界扫描技术是针对数字集成电路(Integrated Circuit,IC)的一种测试技术。

随着集成电路技术的飞速发展,集成度逐渐提高,而集成度的提高也意味着芯片的复杂度将会不断增加,测试成为设计和制造中的核心问题之一。

因此,边界扫描技术应运而生,被广泛应用于芯片测试、故障定位等领域。

其主要原理是在芯片电路的边缘添加额外的控制逻辑,使得这些逻辑可以通过扫描链(SCAN Chain)或者测试向量实现对芯片中部的逻辑单元(logic cell)的任意访问,从而实现对芯片进行完整测试和故障检测。

目前,边界扫描技术已经成为了集成电路测试领域的主流技术之一。

边界扫描技术最初是用于边缘所处的测试程序,常被称为Boundary-Scan,后来不断发展,并广泛应用于各种汽车、飞机、医疗等电子器件的测试中。

据统计,目前已经有超过90%的现代器件集成了边界扫描技术。

此外,随着数字系统的迅速变化,复杂性越来越高,加上我们要减少设计调试的时间,遇到放大比赛技术上的小问题也可能成为一场惨痛的经验,因此边界扫描技术也可以用于故障诊断和电路分析的方面。

但是,在实际应用中,边界扫描技术仅适用于带有边缘扫描逻辑的芯片。

而对于一些没有边缘扫描逻辑的非边缘扫描器件,如异步逻辑、多级管脚等,传统的边缘扫描技术往往无法应用。

边界扫描(boundaryscan)边界扫描(Boundary scan )是⼀项测试技术,是在传统的在线测试不在适应⼤规模,⾼集成电路测试的情况下⽽提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做⼀个CELL。

这些CELL准许你去控制和观察每个输⼊/输出引脚的状态。

当这些CELL连在⼀起就形成了⼀个数据寄存器链(Data Register Chain),我们叫它边界寄存器(Boundary Register)。

除了上⾯的移位寄存器外,在IC上还集成测试访问端⼝控制器 (TAP controller),指令寄存器(Instruction Register)对边界扫描的指令进⾏解码以便执⾏各种测试功能。

旁路寄存器(bypass register)提供⼀个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的⽤户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果⼀个器件是边界扫描器件它⼀定有下⾯5个信号中的前四个:1.TDI (测试数据输⼊)2.TDO (侧试数据输出)3.TMS (测试模式选择输⼊)4.TCK (测试时钟输⼊)5.TRST (测试复位输⼊,Optional)TMS,TCK,TRST构成了边界扫描测试端⼝控制器(TAP controller),它负责测试信号指令的输⼊,输出,指令解码等,TAP controller是⼀个16位的状态机,边界扫描测试的每个环节都由它来控制。

在后续的⽂章中还会向⼤家介绍边界扫描的其它⽅⾯。

边界扫描为开发⼈员缩短开发周期,并且提供良好的覆盖率和诊断信息。

在不了解IC内部逻辑的情况下快速的开发出优秀的测试程序。

在未来的测试领域,边界扫描将会得到⼴泛的应⽤。

边界扫描测试发展于上个世纪90年代,随着⼤规模集成电路的出现,印制电路板制造⼯艺向⼩,微,薄发展,传统的ICT 测试已经没有办法满⾜这类产品的测试要求。