边界扫描技术

- 格式:pptx

- 大小:200.44 KB

- 文档页数:17

边界扫描技术在某导航雷达控制电路板测试与诊断中的研究运用一、引言A. 研究背景和目的B. 边界扫描技术的概述二、相关技术与理论A. 导航雷达控制电路板测试与诊断技术B. 边界扫描技术原理及应用三、实验设计与搭建A. 导航雷达控制电路板的测试与诊断需求B. 边界扫描测试方案设计C. 搭建测试平台及工具实现四、实验结果与分析A. 测试结果及数据分析B. 问题分析与排除过程C. 实验结果的验证和评估五、结论与展望A. 研究总结和贡献B. 科研展望和创新点注:本提纲仅供参考,具体论文框架和内容根据研究要求和撰写习惯进行调整。

一、引言A. 研究背景和目的导航雷达是现代导航设备中不可或缺的重要组成部分,在遥感、军事海洋、大地测量等领域发挥着重要的作用。

而导航雷达控制电路板则是保证雷达稳定运行的重要部件,控制电路板的测试与诊断是确保雷达运行的核心工作。

针对导航雷达控制电路板的测试与诊断,传统的方法往往需要手动检测电路板的各个元器件,测试计算结果,并分析数据,工作量和成本较大。

因此本研究旨在探索边界扫描技术在导航雷达控制电路板的测试与诊断上的实用性和有效性,为实现雷达控制电路板的自动测试和诊断奠定基础。

B. 边界扫描技术的概述边界扫描技术(Boundary Scan)是IEEE标准1149.1所定义的一种通用测试方法,它可以在保持芯片设备处于状态不改变的情况下,通过Access Port对芯片内部的互连电路进行结构测试、功能测试、芯片内部器件诊断,也可以通过这种技术进行编程下载以及重编程等操作,从而实现了高速、无需插拔的设备测试,这一技术在电子工业中被广泛应用。

边界扫描技术可以在不需要改变芯片会话的情况下来测试和诊断设备,这为雷达控制电路板的测试与诊断提供了新思路。

由于导航雷达控制电路较为复杂,常规的测试方法受限于它们操作的复杂性而难以实现高效、可靠的测试。

因此,基于边界扫描技术的自动测试方案可以显著简化测试流程,降低测试成本并提高测试效率。

jtag边界扫描的概念

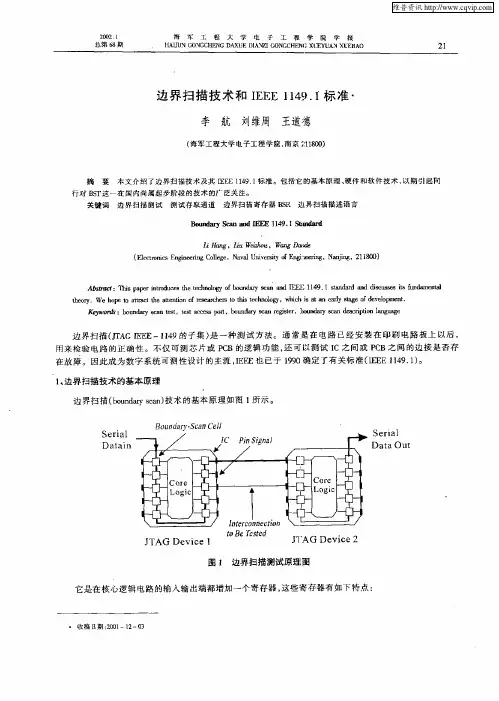

边界扫描(Boundary Scan)是一种测试技术,用于在集成电路板内进行测试,特别是对于那些无法通过传统的测试方法进行测试的复杂电路板。

它利用在每个芯片的输入输出管脚上增加的移位寄存器单元(Boundary-Scan Register Cell),这些寄存器单元分布在芯片的边界上,被称为边界扫描寄存器。

在JTAG调试中,边界扫描是一个非常重要的概念。

当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制。

对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。

正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

它可以串行地输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制。

一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过TAP(Test Access Port)Controller来完成。

以上内容仅供参考,如需更多信息,建议查阅相关文献或咨询专业人士。

boundaryscan应用实例-回复什么是boundary scan技术?Boundary scan技术,又称JTAG(Joint Test Action Group)技术,是一种用于芯片级电路板测试和诊断的技术。

它使用了IEEE标准1149.1定义的边界扫描链(Boundary Scan Chain),通过在电路板上的闩锁功能来实现对芯片上的引脚的测试和调试。

Boundary scan技术的原理和功能如何工作?Boundary scan技术的原理基于一种边界扫描链结构(Boundary Scan Chain),该链将所有芯片引脚连接起来形成一个环。

这个环具有使能信号和测试控制信号,通过这些信号的控制,可以将测试数据从一个引脚传输到另一个引脚,实现对芯片引脚的测试和调试。

Boundary scan技术的功能主要有以下几个方面:1. 电路连通性测试:通过boundary scan技术,可以检测和诊断电路板上信号线的连通性是否良好,以及是否存在断路和短路。

2. 引脚功能测试:通过boundary scan技术,可以实时测试和诊断芯片引脚的功能是否正常。

这对于芯片级的调试和故障排除非常有用。

3. 元件配置和诊断:通过boundary scan技术,可以识别和配置电路板上的各种元件,例如存储器、逻辑门等。

这可以帮助工程师更好地了解电路板的组成和功能。

4. 容错性检查:通过boundary scan技术,可以检查电路板上的信号线是否遵循电气特性,例如正确的电阻和电容值。

这对于确保电路板的稳定性和可靠性至关重要。

Boundary scan技术的应用实例1. 电子设备制造:Boundary scan技术可以在生产线上用于测试和验证电子设备的电路板,以确保其质量和可靠性。

它可以有效地检测和排除电路板上的连通性问题和故障,提高生产效率和产品质量。

2. 电路板维修:当电子设备发生故障时,boundary scan技术可以用于定位和修复故障点。

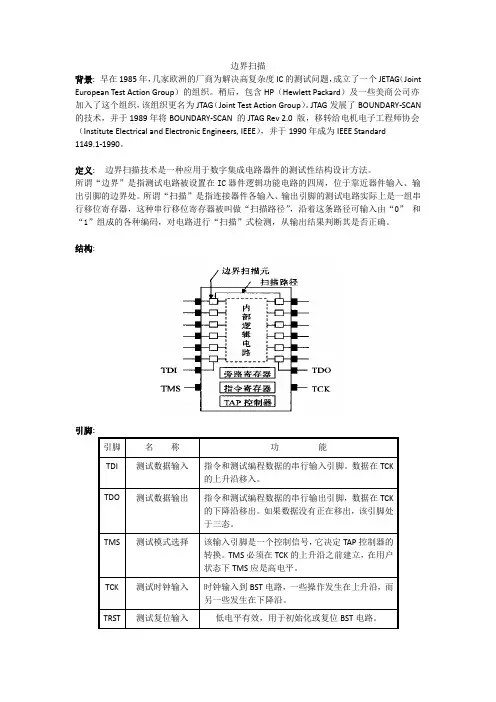

边界扫描背景:早在1985年,几家欧洲的厂商为解决高复杂度IC的测试问题,成立了一个JETAG(Joint European Test Action Group)的组织。

稍后,包含HP(Hewlett Packard)及一些美商公司亦加入了这个组织,该组织更名为JTAG(Joint Test Action Group)。

JTAG发展了BOUNDARY-SCAN 的技术,并于1989年将BOUNDARY-SCAN 的JTAG Rev 2.0 版,移转给电机电子工程师协会(Institute Electrical and Electronic Engineers, IEEE),并于1990年成为IEEE Standard1149.1-1990。

定义:边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。

所谓“边界”是指测试电路被设置在IC器件逻辑功能电路的四周,位于靠近器件输入、输出引脚的边界处。

所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一组串行移位寄存器,这种串行移位寄存器被叫做“扫描路径”,沿着这条路径可输入由“0” 和“1”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确。

结构:引脚:寄存器:1指令寄存器:用来决定是否进行扫描测试和访问数据寄存器操作。

2旁路寄存器:旁路寄存器只有1位,它提供了一条从TDI到TDO之间的最短通道。

当选择了旁路寄存器,实际上没有执行边界扫描测试,它的作用是为了缩短扫描路径,将不需要测试的数据寄存器旁路掉,以减少不必要的扫描时间。

3边界扫描寄存器边界扫描寄存器由大量置于集成电路输入输出引脚附近的边界扫描单元组成。

边界扫描单元首尾相连构成一个串行移位寄存器链,它使用TDI引脚作为输入,TDO引脚作为输出。

在测试时钟TCK的作用下,从TDI加入的数据可以在边界扫描寄存器中进行移动扫描。

设计人员可用边界扫描寄存器来测试外部引脚的连接,或是在器件运行时捕获内部数据。

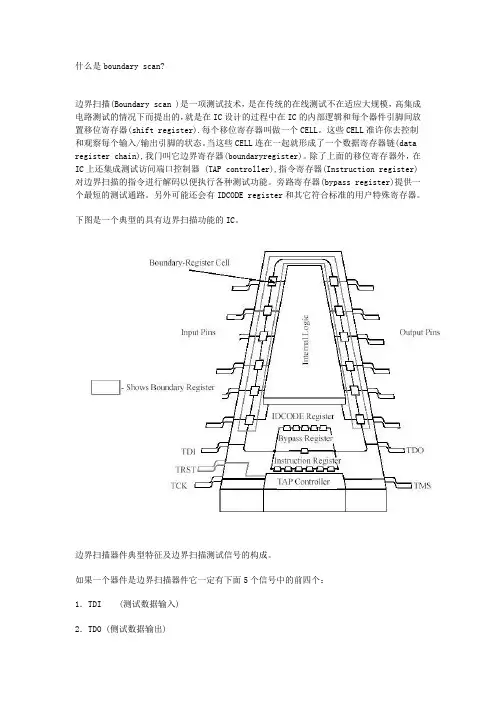

什么是boundary scan?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

下图是一个典型的具有边界扫描功能的IC。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)测试访问端口控制器(TAP controller)TMS,TCK,TRST构成了边界扫描的测试访问端口控制器(TAP controller)。

TAP (the test access port)是一个通用的端口,用来引入控制信号到边界扫描器件(TCK,TMS,TRST*)并且为边界扫描提供串行的输入,输出信号(TDI,TDO)TAP controller是一个16位的状态机,可以通过TMS(test mode selection)和TCK(test clock input)对TAP controller进行编程控制它的状态,TAP controller控制进入指令寄存器(instruction register)和数据寄存器(data register)数据流。

1边界扫描测试技术原理2.边界扫描指令集Extest指令--强制指令用于芯片外部测试,如互连测试测试模式下的输出管脚,由BSC update锁存驱动BSC scan锁存捕获的输入数据移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存原先EXTEST指令是强制为全“0”的,在IEEE 1149.1—2001中,这条强制取消了。

选择边界扫描寄存器连通TDI和TDO。

在这种指令下,可以通过边界扫描输出单元来驱动测试信号至其他边界扫描芯片,以及通过边界扫描输入单元来从其他边界扫描芯片接受测试信号。

EXTEST指令是IEEE 1149.1标准的核心所在,在边界扫描测试中的互连测试(interconnect test)就是基于这个指令的。

Sample/Preload指令编辑Sample/Preload指令--强制指令在进入测试模式前对BSC进行预装载输入输出管脚可正常操作输入管脚数据和内核输出数据装载到BSC的scan锁存中。

移位操作,可以从TDI输入测试激励,并从TDO观察测试响应。

在移位操作后,新的测试激励存储到BSC的update锁存。

原先这两个指令是合在一起的,在IEEE 1149.1--2001中这两个指令分开了,分成一个SAMPLE指令,一个PRELOAD指令。

选择SAMPLE/PRELOAD指令时,IC工作在正常工作模式,也就是说对IC的操作不影响IC的正常工作。

选择边界扫描寄存器连通TDI和TDO。

SAMPLE指令---通过数据扫描操作(Data Scan)来访问边界扫描寄存器,以及对进入和离开IC的数据进行采样。

PRELOAD指令---在进入EXTEST指令之前对边界扫描寄存器进行数据加载。

Bypass指令编辑Bypass指令--强制指令提供穿透芯片的最短通路。

输入输出管脚可正常操作选择一位的旁路(Bypass)寄存器强制全为1和未定义的指令为Bypass指令BYPASS指令为全“1”。

文档来源为:从网络收集整理.word版本可编辑.欢迎下载支持. 集成电路测试方法研究目录1 边界扫描测试方法 ....................................................................................................... 错误!未定义书签。

1.1边界扫描基本状况 ................................................................................................... 错误!未定义书签。

1.2IEEE S TD 1149.1 ........................................................................................................ 错误!未定义书签。

1.3IEEE S TD 1149.4 ........................................................................................................ 错误!未定义书签。

1.4IEEE S TD 1149.5 ........................................................................................................ 错误!未定义书签。

1.5IEEE S TD 1149.6 ........................................................................................................ 错误!未定义书签。

边界扫描测试方法

嘿,咱今儿来聊聊边界扫描测试方法呀!这玩意儿可神奇啦,就像是给电子设备做了一次全面又精细的体检。

你想啊,一个电子设备里面那么多复杂的电路和元器件,就好像是一个庞大的迷宫。

那怎么才能知道这个迷宫里有没有问题呢?边界扫描测试方法就派上用场啦!它就像是一个超级侦探,能一点点地去排查每一个角落。

它是通过在芯片的边界上设置一些特殊的引脚来实现的。

这些引脚就像是一个个小眼睛,能观察到芯片内部的情况。

比如说,它可以检测芯片之间的连接是否正常,有没有短路或者开路的情况。

这多重要啊,要是连接有问题,那整个设备不就乱套啦!

而且哦,边界扫描测试方法还特别灵活。

它可以根据不同的需求和情况,进行各种不同的测试。

就好像你有一套工具,你可以根据要修的东西不同,选择不同的工具来干活儿。

它还能帮助我们在生产过程中及时发现问题。

你想想,要是生产了一大批产品,最后才发现有问题,那得多麻烦,多浪费啊!但有了边界扫描测试方法,就能早早地把问题揪出来,及时解决,多省心啊!

这就好比是我们出门前要照照镜子,看看自己有没有穿戴整齐。

边界扫描测试方法就是给电子设备照镜子,确保它们能以最好的状态工作。

它还能提高设备的可靠性呢!就像我们锻炼身体,让自己更强壮,不容易生病一样。

通过边界扫描测试,能让设备更稳定地运行,减少出故障的概率。

咱再想想,要是没有这个方法,那电子设备出问题了可咋办?那可就像没头苍蝇一样,不知道从哪儿开始找问题啦!所以说,边界扫描测试方法真的是太重要啦!它是电子设备领域的好帮手,是保障设备正常运行的关键一环啊!大家可千万别小瞧了它哟!。

JTAG技术俗称边界扫描技术,是近代发展起来的高级测试技术。

随着电子技术的高速发展,电路已经进入超大规模时代,芯片的封装技术也日新月异,从最初的DIP到QFP,已经当今的BGA,电路的物理可测试性正在逐渐消失。

为了寻找更先进的测试技术,1985年,IBM、AT&T、Texas Instruments、Philips、Siemens、Alcatel、Ericsson等几家公司联合成立了JETAG(Joint European Test Action Group欧洲联合测试行动小组),并提出边界扫描技术。

通过存在于器件输入输出管脚与内核电路之间的BSC(Boundary Scan Cell)对器件及其外围电路进行测试。

1986年,一些欧洲之外的其他公司加入该组织,JETAG组织的成员已不仅仅局限在欧洲,所以该组织名称由JETAG更改为JTAG。

1990年,IEEE(Institute of Electrical and Electronics Engineers,美国电气和电子工程师协会)正式承认JTAG标准,命名为IEEE1149.1-1990。

JTAG主要有以下几个方面应用:1).互连测试。

判断互连线路是否存在开路、短路或固定逻辑故障。

2).可编程器件的程序加载。

如FLASH、CPLD、FPGA等器件的加载。

3).电路采样。

器件正常工作时,对管脚状态进行采样观察。

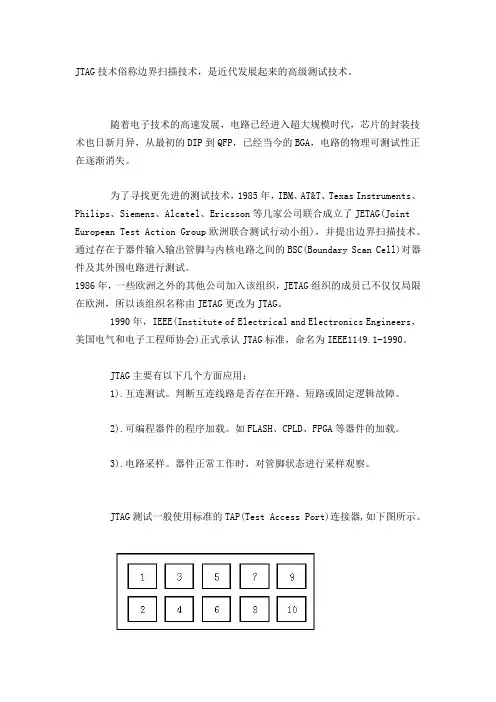

JTAG测试一般使用标准的TAP(Test Access Port)连接器,如下图所示。

A).1号脚为TCK。

JTAG测试参考时钟,由JTAG主控制器提供给被测试器件,该信号需要下拉处理,下拉电阻不能小于330ohm,一般选择1Kohm。

之所以TCK 要下拉处理,是因为JTAG测试规范规定:在TCK为低电平时,被测试器件的TAP 状态机不得发生变化。

所以,默认状态下,TCK必须为低电平,使TAP状态机保持稳定。

最小驱动电流为2mA。

边界扫描的原理及应用1. 引言边界扫描是一种常见的图像处理技术,用于检测和提取图像中物体的边界。

在计算机视觉、图像处理和模式识别等领域,边界扫描被广泛应用于目标检测、物体测量和图像分割等任务。

本文将介绍边界扫描的基本原理,以及其在实际应用中的一些例子。

2. 边界扫描的原理边界扫描的原理基于图像的灰度变化。

在图像中,物体的边界通常具有明显的灰度变化。

边界扫描算法通过分析图像中灰度的变化来检测边界。

边界扫描通常分为以下几个步骤:2.1 图像预处理在边界扫描之前,需要对图像进行预处理,以便提高边界的检测效果。

预处理步骤可以包括图像去噪、灰度化、平滑滤波等。

这些步骤的目的是减少图像中的噪声,并使边界更加明显。

2.2 边缘检测边缘检测是边界扫描的核心步骤。

它通过分析图像中灰度的变化来确定边界的位置。

常用的边缘检测算法包括Sobel算子、Canny算子、拉普拉斯算子等。

这些算子能够在图像中检测出灰度变化较大的区域,从而确定物体的边界。

2.3 边界提取边界提取是根据边缘检测的结果,提取出物体的实际边界。

在边界提取过程中,可以使用一些形态学操作来平滑边界的形状,以及去除噪声。

常用的形态学操作包括膨胀、腐蚀、开运算和闭运算等。

3. 边界扫描的应用边界扫描在许多领域中都有广泛的应用。

以下是一些边界扫描应用的例子:3.1 目标检测边界扫描可以用于目标检测,即通过边界提取来确定图像中是否存在特定的目标。

例如,在交通监控系统中,可以使用边界扫描来检测车辆或行人的位置。

3.2 物体测量边界扫描可以用于物体测量,即通过测量边界的长度、面积或形状来获得物体的尺寸信息。

例如,在工业生产中,可以使用边界扫描来测量产品的尺寸,以进行质量控制。

3.3 图像分割边界扫描可以用于图像分割,即将图像分割为不同的区域或物体。

例如,在医学图像处理中,可以使用边界扫描来分割肿瘤或病变区域,以便进行疾病诊断。

3.4 视觉导航边界扫描可以用于视觉导航,即通过检测环境中的边界来确定机器人或车辆的位置。

什么是边界扫描(boundary scan)?Boundary Scan测试原理及实现JTAG标准的IC芯片结构IEEE 1149.1 标准背景JTAG什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

在不了解IC内部逻辑的情况下快速的开发出优秀的测试程序。

在未来的测试领域,边界扫描将会得到广泛的应用。

JTAG技术俗称边界扫描技术,是近代发展起来的高级测试技术。

随着电子技术的高速发展,电路已经进入超大规模时代,芯片的封装技术也日新月异,从最初的DIP到QFP,已经当今的BGA,电路的物理可测试性正在逐渐消失。

为了寻找更先进的测试技术,1985年,IBM、AT&T、Texas Instruments、Philips、Siemens、Alcatel、Ericsson等几家公司联合成立了JETAG(Joint European Test Action Group欧洲联合测试行动小组),并提出边界扫描技术。

通过存在于器件输入输出管脚与内核电路之间的BSC(Boundary Scan Cell)对器件及其外围电路进行测试。

1986年,一些欧洲之外的其他公司加入该组织,JETAG组织的成员已不仅仅局限在欧洲,所以该组织名称由JETAG更改为JTAG。

1990年,IEEE(Institute of Electrical and Electronics Engineers,美国电气和电子工程师协会)正式承认JTAG标准,命名为IEEE1149.1-1990。

JTAG主要有以下几个方面应用:1).互连测试。

判断互连线路是否存在开路、短路或固定逻辑故障。

2).可编程器件的程序加载。

如FLASH、CPLD、FPGA等器件的加载。

3).电路采样。

器件正常工作时,对管脚状态进行采样观察。

JTAG测试一般使用标准的TAP(Test Access Port)连接器,如下图所示。

A).1号脚为TCK。

JTAG测试参考时钟,由JTAG主控制器提供给被测试器件,该信号需要下拉处理,下拉电阻不能小于330ohm,一般选择1Kohm。

之所以TCK 要下拉处理,是因为JTAG测试规范规定:在TCK为低电平时,被测试器件的TAP 状态机不得发生变化。

所以,默认状态下,TCK必须为低电平,使TAP状态机保持稳定。

最小驱动电流为2mA。

用边界扫描技术检测非边扫器件I. 引言- 简述非边扫描器件的概念及应用背景- 阐述目前检测非边扫描器件所面临的困难和挑战II. 综述边界扫描技术- 介绍边界扫描技术的基本原理和特点- 讨论边界扫描技术在检测集成电路中的应用情况III. 基于边界扫描技术的非边扫描器件检测方案- 提出基于边界扫描技术的非边扫描器件检测方案- 阐述该方案的实现方法IV. 方案实验与结果分析- 设计实验样本集并进行实验测试- 分析实验结果,评估方案的检测能力和鲁棒性V. 结论- 总结该非边扫描器件检测方案的优势和局限性- 展望该方案在未来的应用前景及发展方向附:参考文献边界扫描技术是针对数字集成电路(Integrated Circuit,IC)的一种测试技术。

随着集成电路技术的飞速发展,集成度逐渐提高,而集成度的提高也意味着芯片的复杂度将会不断增加,测试成为设计和制造中的核心问题之一。

因此,边界扫描技术应运而生,被广泛应用于芯片测试、故障定位等领域。

其主要原理是在芯片电路的边缘添加额外的控制逻辑,使得这些逻辑可以通过扫描链(SCAN Chain)或者测试向量实现对芯片中部的逻辑单元(logic cell)的任意访问,从而实现对芯片进行完整测试和故障检测。

目前,边界扫描技术已经成为了集成电路测试领域的主流技术之一。

边界扫描技术最初是用于边缘所处的测试程序,常被称为Boundary-Scan,后来不断发展,并广泛应用于各种汽车、飞机、医疗等电子器件的测试中。

据统计,目前已经有超过90%的现代器件集成了边界扫描技术。

此外,随着数字系统的迅速变化,复杂性越来越高,加上我们要减少设计调试的时间,遇到放大比赛技术上的小问题也可能成为一场惨痛的经验,因此边界扫描技术也可以用于故障诊断和电路分析的方面。

但是,在实际应用中,边界扫描技术仅适用于带有边缘扫描逻辑的芯片。

而对于一些没有边缘扫描逻辑的非边缘扫描器件,如异步逻辑、多级管脚等,传统的边缘扫描技术往往无法应用。