边界扫描测试

- 格式:pdf

- 大小:468.66 KB

- 文档页数:5

IEEE1149.1-1990标准,要求在集成电路中加入边界扫描电路,在板级测试时,可以在主控器的控制下,构成一条在集成电路边界绕行的移位寄存器链,对板内集成电路的所有引脚进行扫描,通过将测试数据串行输入到该寄存器链的方法,检查发现PCB上的器件焊接故障和板内连接故障。

IEEE1149.1定义了边界扫描器件的四线测试访问端口(TAP):TDI、TDO、TCK、TMS,常称为JTAG接口。

TDI(测试数据输入)、TDO(测试数据输出)、TCK(测试时钟)、TMS (测试模式选择)。

TAP控制器支持的几种测试模式:外测试,内测时,运行测试等等。

具有边界扫描功能器件的每一个引脚都与一个串行移位寄存器(SSR)的单元相接,称为边界扫描单元。

边界扫描单元连在一起构成一个移位寄存器链,用于控制和检测器件引脚。

IEEE1149.1标准测试结构:TAP、TAP控制器、指令寄存器和数据寄存器。

TAP控制器由TCK和TMS控制。

在测试逻辑内部,一系列边界扫描指令寄存器以及解码逻辑处于TAP控制器控制之下,并将TDI信号经过可控的延迟之后从TDO输出。

指令寄存器用于设置数据寄存器(Data Register)的工作模式。

有两种数据寄存器必须存在,一是旁路寄存器(Bypass Register),而是边界寄存器(Boundary Register)。

TAP控制器:包含16个状态的有限状态机,由TCK上升沿采样的TMS状态来控制。

指令寄存器:指令寄存器由串行移位寄存器和并行锁存寄存器组成,长度等于器件边界扫描测试指令的长度。

指令寄存器的行为由TAP控制器的状态决定,根据移入指令的内容将某一数据寄存器连接到TDI和TDO之间。

在进行测试操作时,测试指令首先经TDI移入指令寄存器,然后送入指令锁存器,最后TAP控制器将锁存器中的指令译码后,配合其输出信号来控制其它扫描逻辑。

数据寄存器:1.旁路寄存器不需要并行锁存寄存器,且长度只由1位。

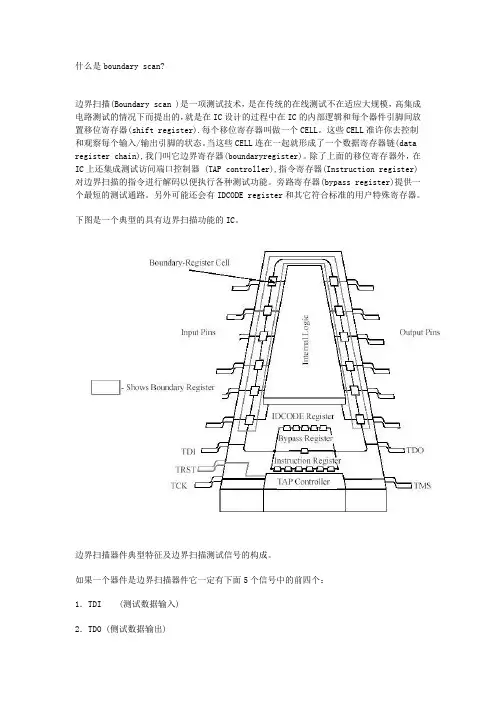

Boundary Scan测试原理及实现什么是边界扫描(boundary scan)?什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器(TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register 和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

在不了解Boundary scan的目的:Boundary scan是一种用于测试数字集成电路的技术,它能找出,开路,短路,和功能不良的数字器件,另外它还能完成一些功能测试。

边界扫描测试原理边界扫描测试是一种黑盒测试方法,其中测试人员专注于程序的边界条件。

该方法旨在检测程序在处理边界条件时是否存在问题,例如程序的最大和最小输入值,以及输入值与最大和最小值之间的情况。

边界扫描测试方法适用于各种程序,包括软件应用程序、Web应用程序和嵌入式系统等。

边界扫描测试方法可以确保程序在处理边界条件时具有正确的行为,并且不会出现错误或异常情况。

这种测试方法可以帮助测试人员发现程序的潜在缺陷,并且可以改进程序的质量和可靠性。

边界扫描测试方法通常包括以下步骤:1. 确定输入值的最大和最小值测试人员需要确定程序所期望的最大和最小输入值。

这可以通过查看程序的规范或文档来实现。

如果程序没有明确的规范或文档,则测试人员需要自己确定最大和最小值。

2. 确定输入值与最大和最小值之间的情况测试人员需要确定输入值与最大和最小值之间的情况。

例如,如果程序要求输入数字,则测试人员需要确定输入数字的最大和最小值,并确定输入数字与这些值之间的情况。

3. 编写测试用例测试人员需要编写测试用例来测试程序的边界条件。

测试用例应包括最大和最小输入值以及输入值与最大和最小值之间的情况。

测试用例应覆盖所有可能的情况,并且应该能够测试程序的所有功能。

4. 运行测试用例测试人员需要运行测试用例并记录测试结果。

如果测试用例中出现错误或异常情况,则测试人员需要将其记录下来并报告给开发人员。

5. 分析测试结果测试人员需要分析测试结果,并确定程序在处理边界条件时是否存在问题。

如果存在问题,则测试人员需要将其报告给开发人员,并协助开发人员解决问题。

总结边界扫描测试方法是一种有效的黑盒测试方法,可以帮助测试人员发现程序在处理边界条件时的潜在缺陷,并改进程序的质量和可靠性。

边界扫描测试方法需要测试人员确定输入值的最大和最小值,并编写测试用例来测试程序的边界条件。

测试人员需要运行测试用例,并记录测试结果。

最后,测试人员需要分析测试结果,并将问题报告给开发人员。

jtag边界扫描的概念

边界扫描(Boundary Scan)是一种测试技术,用于在集成电路板内进行测试,特别是对于那些无法通过传统的测试方法进行测试的复杂电路板。

它利用在每个芯片的输入输出管脚上增加的移位寄存器单元(Boundary-Scan Register Cell),这些寄存器单元分布在芯片的边界上,被称为边界扫描寄存器。

在JTAG调试中,边界扫描是一个非常重要的概念。

当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制。

对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。

正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

它可以串行地输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制。

一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过TAP(Test Access Port)Controller来完成。

以上内容仅供参考,如需更多信息,建议查阅相关文献或咨询专业人士。

集成电路边界扫描测试中的电路网表结构分析集成电路边界扫描测试(Boundary Scan Testing,BST)是一种广泛应用于VLSI设计和制造中的测试技术。

BST是一种将测试功能集成到复杂的芯片设计中的方法,它可以诊断集成电路中的任何一个缺陷,从而提高产品的质量和性能。

BST采用的核心技术是边界扫描技术(Boundary Scan),用于测试芯片的连接性、可编程逻辑器件(Programmable Logic Devices,PLD)和电路的故障诊断。

在BST中,电路网表结构分析是非常关键的一个步骤。

电路网表结构指的是VLSI集成电路中各个模块相互连接的电路线路结构,也就是电路的物理连接方式。

电路网表结构分析的主要目的是找出部分设计错误和模块之间的错误连接,以确保VLSI集成电路在边界扫描测试过程中能够被正确地测试。

电路网表结构分析需要一些专门的工具和软件来实现。

首先,我们需要对VLSI集成电路进行仿真和验证,确定其运行正确。

然后,需要将电路分解成多个模块和其相应的边界扫描单元(Boundary Scan Cells)。

Boundary Scan Cells是一种可设置逻辑器件,可以被串联到某个端口上,常常与电路网表结构密切相关。

在电路网表结构分析的过程中,我们需要同时验证电路网表结构和单元测试。

我们可以通过检查边界扫描链上的信号线路和寄存器电路是否正确来检测电路网表结构错误。

如果有任何电路连接错误,那么边界扫描测试将无法在这些错误地连接的边界扫描单元上进行正确测试,从而导致电路测试失败。

电路网表结构分析在VLSI设计过程中非常重要,它可以帮助我们找出设计中的错误和潜在的问题,最终确保集成电路在真正的测试前可以顺利进行边界扫描测试,从而提高产品的质量和性能。

在今后的VLSI设计工作中,电路网表结构分析将继续发挥重要作用,帮助人们设计出更加合理、优秀的电路设计。

边界扫描测试系统一、IEEE1149.1产生的背景当今电子制造商正面临着越来越大的降低成本、提高质量及缩短生产周期的压力,电路板越来越密、器件越来越复杂、电路性能要求也越来越苛刻,这一切直接导致了电子器件的生产商和电子产品的制造商都在倾向于采用最新的器件技术,如GA、CSP、TCP 等更小的封装,以更小的体积提供更强的功能。

但是随之而来的接入问题却日益成为测试的巨大障碍。

为了解决此类问题,IEEE1149.1———边界扫描测试技术应运而生。

二、边界扫描测试的原理边界扫描测试是一种可测试结构技术,它采用集成电路的内部外围所谓的“电子引脚”(边界)模拟传统的在线测试的物理引脚,对器件内部进行扫描测试。

它是在芯片的I/O端上增加移位寄存器,把这些寄存器连接起来,加上时钟复位、测试方式选择以及扫描输入和输出端口,而形成边界扫描通道。

IEEE1149.1标准规定了一个四线串行接口(第五条线是可选的),该接口称作测试访问端口(TAP),用于访问复杂的集成电路(IC),例如微处理器、DSP、ASIC 和CPLD等。

在TDI(测试数据输入)引线上输入到芯片中的数据存储在指令寄存器中或一个数据寄存器中。

串行数据从TDO(测试数据输出)引线上输出。

边界扫描逻辑由TCK(测试时钟)上的信号计时,而且TMS(测试模式选择)信号控制驱动TAP控制器的状态。

TRST*(测试重置)是可选项,可作为硬件重置信号,一般不用。

详细边界扫描结构及信号流程参考图1。

图1中“TAP Controller”其实质上是一个状态切换到6个不同的状态,具体状态逻辑参考图2。

从一个状态切换成另一个状态总是发生在TCK的上升沿,由TMS 从两个状态选择其中一个状态。

在测试向量寄存器中,既有指令寄存器(IR),又有数据寄存器(DR),而且,为了区分是指令还是数据,扫描链路中的状态图有两个独立的完全类似的结构(Scan DR/ Scan IR)。

测试操作的最重要步骤是移入和同步移出测试数据(DR SHIFT),新的数据进入移位链,测试数据传送到测试单元DR-update)的输出锁存器中,对于指令寄存器(IR-shift,IR-capture,IR-update)同样如此。

数字电路测试方法数字电路测试是电子工程领域中非常重要的一项工作,它用于确保电路设计的正确性和功能性。

本文将介绍一些常见的数字电路测试方法,包括仿真测试、功能测试、时序测试和边界扫描测试。

一、仿真测试仿真测试是一种基于软件的测试方法,它通过电路设计工具将电路的行为模拟出来,以验证电路的逻辑功能。

在仿真测试中,可以使用不同的输入信号来模拟各种情况,并观察输出信号是否符合预期。

仿真测试具有快速、灵活、便于调试等优点,但它并不能覆盖所有可能的输入组合,因此不能完全代替其他测试方法。

二、功能测试功能测试是一种基于实际硬件的测试方法,它通过输入不同的数据和信号来测试电路的功能是否符合要求。

在功能测试中,可以使用开关、按键、信号发生器等设备来激活电路,并观察输出信号的状态。

功能测试可以检测电路的基本功能,但不能检测电路的时序和边界问题。

三、时序测试时序测试是一种用于检测电路时序问题的测试方法。

时序问题指的是电路在不同的时钟信号下的工作状态是否正确。

在时序测试中,可以通过激活时钟信号,并观察电路的输出信号来验证电路的时序逻辑。

时序测试需要对电路的时钟频率、占空比等参数进行严格的控制和测试,以确保电路的稳定性和可靠性。

四、边界扫描测试边界扫描测试是一种用于检测电路边界问题的测试方法。

边界问题指的是电路输入和输出信号之间的接口是否正确连接。

在边界扫描测试中,可以将电路的边界信号分别输入和输出,并观察信号的正确性和一致性。

边界扫描测试可以帮助发现电路中各个模块之间的连接问题,避免信号传输错误或连接不良的情况。

总结:数字电路测试是确保电路设计正确性和功能性的关键步骤。

本文介绍了常见的数字电路测试方法,包括仿真测试、功能测试、时序测试和边界扫描测试。

这些测试方法各具特点,能够有效地检测电路中的问题,提高电路的可靠性和稳定性。

在实际应用中,可以根据具体需求选择合适的测试方法或组合多种测试方法来进行全面的数字电路测试工作。

什么是boundary scan?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

下图是一个典型的具有边界扫描功能的IC。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)测试访问端口控制器(TAP controller)TMS,TCK,TRST构成了边界扫描的测试访问端口控制器(TAP controller)。

TAP (the test access port)是一个通用的端口,用来引入控制信号到边界扫描器件(TCK,TMS,TRST*)并且为边界扫描提供串行的输入,输出信号(TDI,TDO)TAP controller是一个16位的状态机,可以通过TMS(test mode selection)和TCK(test clock input)对TAP controller进行编程控制它的状态,TAP controller控制进入指令寄存器(instruction register)和数据寄存器(data register)数据流。

边界扫描测试方法

嘿,咱今儿来聊聊边界扫描测试方法呀!这玩意儿可神奇啦,就像是给电子设备做了一次全面又精细的体检。

你想啊,一个电子设备里面那么多复杂的电路和元器件,就好像是一个庞大的迷宫。

那怎么才能知道这个迷宫里有没有问题呢?边界扫描测试方法就派上用场啦!它就像是一个超级侦探,能一点点地去排查每一个角落。

它是通过在芯片的边界上设置一些特殊的引脚来实现的。

这些引脚就像是一个个小眼睛,能观察到芯片内部的情况。

比如说,它可以检测芯片之间的连接是否正常,有没有短路或者开路的情况。

这多重要啊,要是连接有问题,那整个设备不就乱套啦!

而且哦,边界扫描测试方法还特别灵活。

它可以根据不同的需求和情况,进行各种不同的测试。

就好像你有一套工具,你可以根据要修的东西不同,选择不同的工具来干活儿。

它还能帮助我们在生产过程中及时发现问题。

你想想,要是生产了一大批产品,最后才发现有问题,那得多麻烦,多浪费啊!但有了边界扫描测试方法,就能早早地把问题揪出来,及时解决,多省心啊!

这就好比是我们出门前要照照镜子,看看自己有没有穿戴整齐。

边界扫描测试方法就是给电子设备照镜子,确保它们能以最好的状态工作。

它还能提高设备的可靠性呢!就像我们锻炼身体,让自己更强壮,不容易生病一样。

通过边界扫描测试,能让设备更稳定地运行,减少出故障的概率。

咱再想想,要是没有这个方法,那电子设备出问题了可咋办?那可就像没头苍蝇一样,不知道从哪儿开始找问题啦!所以说,边界扫描测试方法真的是太重要啦!它是电子设备领域的好帮手,是保障设备正常运行的关键一环啊!大家可千万别小瞧了它哟!。

集成电路测试方法研究目录1 边界扫描测试方法 (1)1.1边界扫描基本状况 (1)1.2IEEE S TD 1149.1 (1)1.3IEEE S TD 1149.4 (3)1.4IEEE S TD 1149.5 (5)1.5IEEE S TD 1149.6 (6)1.6边界扫描测试的发展前景 (9)1.7本章小结 (9)2 全扫描可测试性实现方法 (10)2.1为什么需要扫描测试 (10)2.2可扫描单元类型 (11)2.2.1多路选择器型的触发器 (11)2.2.2 专用时钟扫描单元 (12)2.2.3 电平敏感扫描设计 (12)2.2.4辅助时钟LSSD的扫描方式 (15)2.3如何提高故障覆盖率 (15)2.3.1门控时钟问题 (15)2.3.2时钟分频问题 (16)2.3.3内部复位问题 (17)2.3.4 三态网络的DFT (18)2.3.5双向引脚的DFT (24)2.4一个实现实例 (28)2.5本章小结 (29)3 集成电路的低功耗DFT方法 (30)3.1测试模式下功耗比较高的原因 (30)3.2基于扫描设计的低功耗DFT方法 (31)3.2.1测试矢量的处理 (31)3.2.2合理划分片上的测试资源 (31)3.2.3 减少测试电路节点的翻转次数 (33)3.2.4软硬件协同测试 (34)3.3基于非扫描设计的低功耗DFT方法 (34)3.3.1 对测试向量处理得到低功耗ATPG (35)3.3.2降低CUT输入端的活动性 (37)3.3.3采用混合模式测试向量 (38)3.4本章小结 (39)1 边界扫描测试方法扫描技术是实现数字系统可测试性的关键技术,它包括边界扫描、全扫描、部分扫描。

本章介绍边界扫描的实现方法,全扫描和部分扫描将在下一章介绍。

边界扫描技术一开始是为了测试芯片之间的简单互连(即导线直接连接)。

由于系统芯片的设计是基于IP核的设计,IP核之间的互连也可以采用边界扫描技术来实现。

什么是边界扫描(boundary scan)?Boundary Scan测试原理及实现JTAG标准的IC芯片结构IEEE 1149.1 标准背景JTAG什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

dft的测试方法DFT的测试方法概述DFT(Design for Testability,测试性设计)是一种设计方法,旨在确保电子设备的可测试性和可靠性。

它包括在设计过程中引入测试功能,以便更容易地检测和诊断设备的故障。

本文将介绍DFT的测试方法,并探讨其在电子设备制造过程中的重要性和应用。

1.扫描链测试扫描链测试是DFT中最常用的测试方法之一。

它通过在设计中引入扫描链,将电路分成多个扫描链,使得测试信号可以从输入端口进入电路,然后通过扫描链输出。

这种方法可以大大简化测试过程,提高测试覆盖率和效率。

同时,扫描链测试还可以检测到电路中的短路、开路和延迟故障等问题。

2.边界扫描测试边界扫描测试是一种用于测试集成电路(IC)边界的DFT技术。

它通过在IC设计中引入边界扫描链,将输入和输出端口与边界扫描链相连接,从而实现对IC边界的测试。

边界扫描测试可以有效地测试IC边界上的逻辑和电气特性,并提供高测试覆盖率和可靠性。

3.存储器BIST测试存储器BIST(Built-In Self-Test,内建自测试)是一种用于测试存储器的DFT技术。

它通过在存储器中内置测试电路和算法,实现存储器的自测试。

存储器BIST测试可以在芯片制造过程中自动进行,无需外部测试设备,大大提高了测试效率和可靠性。

4.电路自适应测试电路自适应测试是一种基于DFT的自适应测试方法。

它通过在电路中引入自适应测试电路,实现对电路的自动测试和故障诊断。

电路自适应测试可以根据电路的实际工作状态和测试需求,自动选择最佳的测试算法和参数,提高测试效率和准确性。

5.故障模拟测试故障模拟测试是一种基于DFT的故障检测方法。

它通过在设计中引入故障模拟电路,模拟故障情况,然后利用模拟结果进行故障检测和诊断。

故障模拟测试可以帮助设计人员了解电路的故障情况,优化设计和测试策略,提供更可靠的电子设备。

6.片上监测测试片上监测测试是一种用于监测电子设备工作状态的DFT技术。

边界扫描测试的内测试流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!边界扫描测试的内部测试流程详解在软件和硬件测试领域,边界扫描测试是一种广泛应用的测试技术,主要用于验证电路板上的输入/输出(I/O)端口。