Quartus-II中FPGA管脚的分配策略资料

- 格式:docx

- 大小:1.88 MB

- 文档页数:15

6.3 Quartus II操作指南6.3.1简介Altera技术领先的Quartus II设计软件配合一系列可供客户选择的IP核,可使设计人员在开发和推出FPGA、CPLD和结构化ASIC设计的同时,获得无与伦比的设计性能、一流的易用性以及最短的市场推出时间。

这是设计人员首次将FPGA移植到结构化ASIC 中,能够对移植以后的性能和功耗进行准确的估算。

Quartus II软件支持VHDL和Verilog硬件描述语言(HDL)的设计输入、基于图形的设计输入方式以及集成系统级设计工具。

Quartus II软件可以将设计、综合、布局和布线以及系统的验证全部都整合到一个无缝的环境之中,其中还包括和第三方EDA工具的接口。

Quartus II的主要特性有:<1>基于模块的设计方法提供工作效率<2>更快集成IP<3>在设计周期的早期对I/0引脚进行分配和确认<4>存储器编译器<5>支持CPLD、FPGA和基于HardCopy 的ASIC<6>使用全新的命令行和脚本功能自动化设计流程<7>高级教程帮助深入了解Quartus II的功能特性。

Altera公司的Quartus II软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证和仿真。

Quartus II设计软件根据设计者需要提供了一个完整的多平台开发环境,它包括整个FPGA和CPLD设计阶段的解决方案。

有关Quartus II的典型设计流程如图6-43所示。

1图6-43 Quartus II的典型设计流程此外,Quartus II软件为设计流程的每个阶段提供了Quartus II图形用户界面、EDA 工具界面和命令行界面。

Quartus II简明教程前言本教程是给Quartus II软件的初学者使用的入门级读物,主要翻译Altera公司DE2开发板CD-ROM 中的Quartus II Introduction Using Verilog Design教程而成。

主要内容是结合Altera公司的DE2开发板,通过一个简单的例子介绍使用Quartus II软件进行FPGA设计的整个流程,同时简单介绍FPGA设计的的一些基本知识。

主要作为哈尔滨理工大学电子科学与技术系的<<可编程逻辑器件>>和<<硬件描述语言>>两门课的试验指导材料使用。

限于水平,难免有错误和不妥之处,恳请读者批评指正。

联系作者,作者将不胜感激。

Altera公司的Quartus II设计软件是用来进行SOPC(System-on-a-programmable-chip)设计的综合设计环境。

本教程适用于Quartus II软件的新用户,介绍使用Quartus II软件的进行FPGA设计的基本方法。

需要注意,本教程并不是Quartus II软件的详尽的参考手册。

本教程包含的主要内容:1、典型的FPGA设计流程;2、开始3、新建project4、设计输入5、编译6、引脚分配7、仿真8、编程、配置FPGA器件9、板级调试1、典型的FPGA设计流程计算机辅助设计(Computer Aided Design,CAD)软件的使用使得使用可编程逻辑器件(Programmable Logic Device,PLD)器件(比如Field Programmable Gate Array,FPGA)进行数字逻辑电路设计变得非常容易。

使用CAD软件进行FPGA设计的典型流程如图1所示。

Quartus II软件支持以上设计流程的所有阶段。

本教程介绍Quartus II软件的基本特征。

2、开始在Quartus II软件中设计的每个电路或者子电路都叫做项目(Project)。

2.3 第一个上板例程2.3.1下载例程请首先下载代码例程,下载地址:/cHRC6ZIfPXdmR 访问密码 a101。

将该代码存放到工程目录,该目录不能有中文、空格或者特殊字符。

该代码功能:代码中clk是模块时钟,rst_n是模块复位信号,key是对应于FPGA的按键0,led对应于开发板上的4个LED灯。

下载程序到开发板后,4个LED灯开发轮流闪烁,类似于流水灯效果。

2.3.2 新建工程打开QuartusII,然后File->New Project wizard…,弹出如下新建工程中的介绍窗口。

按Next,开始配置工程信息。

其中,第一栏是设置工程目录。

要求该目录不能有中文、空格或特殊字符,该目录下保存有下载的例程代码。

例如本工程的目录是F://project。

第二栏是设置工程名,工程名同样不能包含有中文、空格和特殊字符。

本例子工程名为key_project。

第三栏是设置设计文件中最顶层的模块名。

如果项目有多个设计模块,则必定有一个模块是最顶层的,这个模块会逐个例化其他需要的模块。

注意,设计文件名与模块名可以不同,例如我们可以在light2.v中,定义一个模块:module light(clk,rst,key,led),其中light2是文件名,light是模块名。

虽然文件名与模块名可以不同,但实际上没必要这样做,而且还增加很多麻烦。

此栏必须填写key_light,因为例程的模块名就是key_light。

设置完毕后,按Next,弹出选择源代码窗口。

在此处可以添加下载的例程key_light.v代码。

添加完毕后,按Next,弹出设置芯片的窗口。

Altera推出了非常多款的芯片,一般芯片都可以在此处显示。

如果没有显示,则需要升级QuartusII软件或添加设计库。

本例程我们选择EP4CE6E22C8这款芯片。

设置完毕后后,连续按两次Next,直接出现Finish,按Finish后,完成工程的创建。

在我们“动态频谱资源共享宽带无线通信系统”项目中,使用的FPGA 芯片是Xilinx 公司的XC5VSX95T-FF1136C ,该芯片是Virtex-5 SXT 系列的一款芯片,FF 代表芯片的封装形式是F lip-chip F ine-pitch BGA (引脚之间的间距是1.00mm),1136表示该芯片有1136个引脚。

芯片大小是35*35(mm 2),芯片引脚分布框图如图1所示。

图1 XC5VSX95T-FF1136C 的引脚分布图从图1我们可知,芯片的引脚由34行和34列组成,34*34=1156,但是有20个行列交叉点没有作为引脚(比如A1、AP4),所以该芯片总的引脚数为1156-20=1136。

GPIO(640)在所有引脚中数目最多的是GPIO引脚,总共有640个,由于GPIO引脚采用差分形式传输信号,所以最多可以同时传输320个不同的输入输出信号。

图1中白色圆圈表示的就是GPIO引脚(比如G5、AC8)。

有些GPIO引脚是多功能引脚,也就是说这些引脚除了可以作为数据输入输出,还可以作为其他用途,比如可以在SelectMAP模式配置为数据输入引脚(D27)的G22,可以作为外部门限电压引脚(VREF)的A28。

640个GPIO引脚被分为18组(BANK),其中BANK1、BANK2、BANK3、BANK4为20个引脚,即20*4=80,另外BANK5、BANK6、BANK11、BANK12、BANK13、BANK15、BANK17、BANK18、BANK19、BANK20、BANK21、BANK22、BANK23、BANK25为40个引脚,即40*14=560。

GPIO的分组如图2所示。

图2 XC5VSX95T-FF1136C的GPIO引脚分组图BANK0(27)此外,还有一个分组叫BANK0,该分组是专用配置分组(Dedicated Configuration Bank)。

该分组有27个引脚,其中两个保留引脚(RSVD),6个引脚用于Dedicated System Monitor,剩余19个引脚用于其他专用配置。

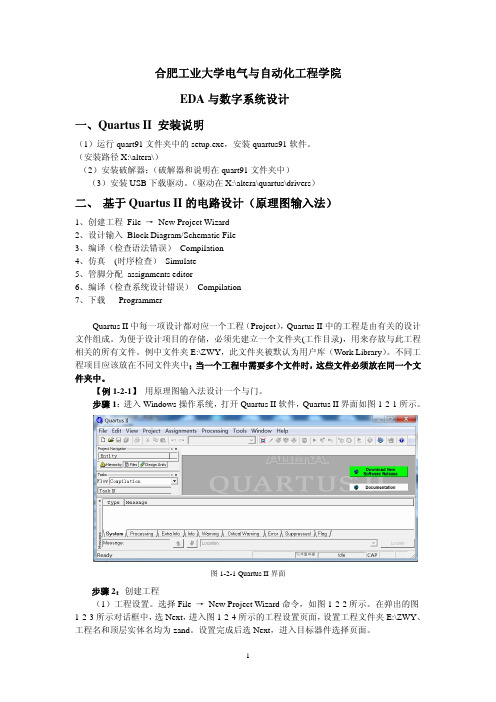

实验一QUARTUS II 入门QUARTUS 操作步骤,以“二选一多路选择器”为例1、如图1所示在F盘,建立以自己学号命令的文件夹如200913000000,并在其中建立命为EX1的文件夹,用来保存实验1的文件。

图12、如图2所示,点击Flie->New Project Wizard建立新的工程文件。

图23、将出现如图3所示的界面,点击如图所示的省略号,选择工程文件所要保存的位置。

图34、如图4所示,选中F:\20091300000\EX1并点击打开,进入如图5所示的界面图45、如图5所示,在工程文件保存的路径中显示刚才所选择的路径F:\20091300000\EX1图56、如图6所示,在What is the name of this project的栏目中输入工程的名字本实验临时取mux21a。

同时下面的顶层实体名也同步显示,然后点击Next进入到界面7。

图67、如图7所示,本界面是需要选择已有的文件,因为我们是新的工程,暂时没建立任何文件,所以直接点击Next进入到界面8。

图78、如图8所示,进行器件选择,我们要根据实验箱的芯片来进行器件选择。

选择CycloneII 系列。

图89、如图9所示,在CycloneII系列下选择EP2C5T144C8的芯片。

然后点击Next进行界面10。

图910、如图10所示,此界面是选择额外的综合、仿真工具软件,因为Quartus II本身自带有这些功能,所以我们不选择额外的工具软件。

直接点击Next进入到界面11。

图1011、如图11所示,此界面显示前面所有步骤的结果,包括文件保存路径、工程名、顶层实体名、芯片的系列与具体型号、额外的工具软件等等。

检查没错后点击Finish,如果有错点击Back返回进行修改。

图1112、如图12所示为已经建好工程的界面,显示工程名与工程文件路径。

图1213、如图13所示,点击新建文件按钮或File->New建立新文件,进入到如图14界面。

QuartusII软件概述QuartusII软件是Altera公司最新版本的EDA开发软件,支持APEX系列、Cyclone系列、Stratix系列和Excalibur系列等新型系列器件的开发。

含有工作组计算、集成逻辑分析仪、EDA工具集成、多过程支持、增强重编译和IP集成等特性。

支持百万门级的设计,支持高速I/O设计,具有更强的设计能力和更快的编译速度。

QuartusII开发软件为可编程片上系统(SOPC)设计提供了一个完整的设计环境。

无论是使用个人电脑、NUIX或Linux 工作站,QuartusII都提供了方便设计、快速编译处理以及编程功能。

QuartusII输入的设计过程可分为创建工程、输入文件、项目编译、项目校验和编程下载等几个步骤。

1文本输入的设计过程现通过一个简单设计实例说明QuartusII的基本文本设计过程。

例:用硬件描述语言VHDL设计一个2 输入与非门,设计放d:\ nand2_lab1目录下,工程文件名为nand2_lab1 。

先打开“我的电脑”,在D盘新建名为“nand2_lab1”文件夹。

1、创建工程文件利用QuartusII软件创建工程向导(New Project Wizard)创建一个新工程。

步骤如下:1)打开QuartusII6.0软件界面,在“文件”菜单下选择“New Project Wizard”,点击“next”后弹出如图1.1对话框图1.1 New Project Wizard对话框第一页点选第一行右侧的“…”选择工程目录为“d:\ nand2_lab1”,在第二行输入项目名称: nand2_lab1,第三行默认把项目名设为顶层文件名,点击“next”,2)新建项目向导第二页,如图1.2,该窗口可为项目添加已经编辑好的程序文件,默认为空,点击“next”,图1.2 New Project Wizard对话框第二页3)新建项目向导第三页,如图1.3,该窗口可以选择FPGA硬件信息,在Family下拉框内选择“FLEX10K”,在Avaliable devices窗口选择芯片型号为:EPF10K20RC208-4,其它选项默认。

第七章QUARTUSII⼊门指南第七章 QUARTUS II ⼊门指南7.1 QUARTUS II软件简介7.2 QUARTUS II基本设计流程7.3 原理图输⼊设计⽅法7.4 嵌⼊式逻辑分析仪SignalTap II的使⽤7.5 宏功能模块的应⽤7.1 QUARTUS II软件简介Quartus II是Altera公司推出的CPLD/FPGA开发⼯具,Quartus II提供了完全集成且与电路结构⽆关的开发包环境,具有数字逻辑设计的全部特性,包括:可利⽤原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体⽂件;芯⽚(电路)平⾯布局连线编辑;LogicLock增量设计⽅法,⽤户可建⽴并优化系统,然后添加对原始系统的性能影响较⼩或⽆影响的后续模块。

7.1.1 QUARTUS II基本特点功能强⼤的逻辑综合⼯具;完备的电路功能仿真与时序逻辑仿真⼯具;定时/时序分析与关键路径延时分析;可使⽤SignalTap II逻辑分析⼯具进⾏嵌⼊式的逻辑分析;⽀持软件源⽂件的添加和创建,并将它们链接起来⽣成编程⽂件;使⽤组合编译⽅式可⼀次完成整体设计流程;⾃动定位编译错误;⾼效的期间编程与验证⼯具;可读⼊标准的EDIF⽹表⽂件、VHDL⽹表⽂件和Verilog⽹表⽂件;能⽣成第三⽅EDA软件使⽤的VHDL⽹表⽂件和Verilog⽹表⽂件。

7.1.2 QUARTUS II系统安装1、QUARTUS II安装Quartus II 系统要求较⾼的系统配置,配置过低将使得编译过程⼗分缓慢。

对于安装Quartus II 7.2版本的系统必须满⾜以下最低要求:z硬件:运⾏速度为866MHz或更快Pentium III 以上计算机,系统内存容量⼤于256M。

z操作系统:Microsoft Windows 2000或Microsoft Windows XP。

安装QuartusII 之前建议浏览⼀下安装⽂件夹下的帮助⽂件及注意事项。

精品文档Quartus II中FPGA管脚的分配策略编写:***校核:审核:二〇一年月日目录目录 (I)QUARTUS II中FPGA管脚分配策略 (1)1.FPGA管脚介绍 (1)1.1.电源管脚 (1)1.2.配置管脚 (2)1.3.普通I/O管脚 (2)1.4.时钟管脚 (2)2.FPGA管脚分配方法 (3)2.1.P IN P LANNER方式 (3)2.2.I MPORT A SSIGNMENTS方式 (4)2.3.T CL S CRIPTS方式 (6)2.4.项目组统一使用方式 (9)3.编写FPGA管脚分配文件 (10)3.1.查看PDF格式的原理图 (10)3.2.查看P RJ PCB格式的原理图 (11)4.保存FPGA管脚分配文件 (12)4.1.T CL格式或CSV格式 (12)4.2.QSF格式 (12)4.3.项目组统一使用格式 (12)附录管脚类型说明 (13)Quartus II中FPGA管脚分配策略1. FPGA管脚介绍FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。

一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。

从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。

下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。

图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA的各个管脚分布在不同的Bank中。

其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。

圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。

正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。

五边形标记的管脚为配置管脚。

图1 Wire Bond1.1. 电源管脚FPGA通常需要两个电压才能运行,一个是内核电压,另一个是I/O电压。

每个电压通过独立的电源管脚来提供。

内核电压是用来给FPGA内部的逻辑门和触发器供电。

随着FPGA的发展,内核电压从5V、3.3V、2.5V、1.8V到1.5V ,变得越来越低。

I/O电压用来给各个Bank供电,每个Bank 都有独立的I/O电压输入。

一般情况下,内核电压会比I/O电压低。

图1中的VCCINT是内核电压管脚,VCCIO是I/O电压管脚。

1.2. 配置管脚每个FPGA都需要配置管脚,以支持多种配置方式,例如JTAG、从串、从并、主串、主并等。

对于配置管脚的控制信号来说,是专用管脚,不能作为普通的I/O管脚。

而其数据信号可以作为普通的I/O管脚使用。

图1中的MSEL为配置模式选择信号,即选择AS模式、PS模式或FAST AS模式。

MSEL[1:0]为00表示用AS模式,10表示用PS模式,01表示用FAST AS模式。

如果用JTAG模式,MSEL[1:0]置00,JTAG模式和MSEL无关,即用JTAG模式时,MSEL会被忽略,但是因为MSEL不能浮空,所以置00。

图1中的TMS、TCK、TDI和TDO为JTAG接口的4根线,分别为模式选择、时钟、数据输入和数据输出线。

常用的为AS模式和JTAG模式。

1.3. 普通I/O管脚FPGA的I/O管脚是FPGA上较为丰富的资源,也是做管脚约束时最常用的资源。

对于FPGA 的普通I/O管脚,可以设定电平类型(TTL、LVTTL、LVCOMS、ECL等)、驱动电流、摆率等参数。

1.4. 时钟管脚FPGA内部的时钟都需要通过专用时钟管脚连接内部PLL或者DCM等专用时钟处理单元,从而接入内部高速时钟网络。

对于一些外部同步信号的输入,如果时钟只用于采样当前的同步信号,其时钟可以不用连接到专用时钟管脚上,即不用接入全局时钟网络,但需要约束其管脚不使用全局时钟资源。

否者,EDA 工具会报错,提示其作为时钟输入而没有接在专用时钟管脚上。

更多的管脚类型说明见附录。

2. FPGA管脚分配方法FPGA管脚分配常用的有3种方式,分别为Pin Planner方式、Import Assignments方式和Tcl scripts 方式。

2.1. Pin Planner方式步骤1:在Quartus II软件中,选择“Assignments Pin Planner”,或者按快捷键“Ctrl+Shirt+N”,出现如图2所示的画面。

通过下拉菜单可以选择需要的管脚在Location选择了管脚后I/O Bank自动填充Bank内部的细分区域,非修改属性用于支持对应不同的电平标准,即VCCIO。

每个Bank只能有一种电压标准对管脚内部的I/O逻辑进行约束驱动电流强度电压转换速率,表示单位时间内电压升高的幅值图2 Pin Planner图2主要包含了7个选择项,分别为Location、I/O Bank、VREF Group、I/O Standard、Reserved、Current Strength和Slew Rate。

Location里可以选择所需要的芯片管脚,管脚确定后I/O Bank中的Bank数会自动填充,VREF Group也会自动填充。

I/O Standard是每个Bank对应的电压标准,一个Bank只能有一种电压标准,一般情况下选择默认值就好。

Reserved是对管脚内部的I/O逻辑进行约束,有6个选择项供选择,例As SignalProbe output、As bidirectional等。

Current Strength是驱动电流强度,一般选择默认值,如果需要驱动大功率的电路,一般在FPGA外围加驱动电路。

Slew Rate 是电压转换速率,跟信号跳变时间有关,一般选择默认值。

在管脚分配的过程中,我们主要关心Location这一选项,其他选项采用默认值就可。

步骤2:在Location中选择管脚。

所有管脚配置完成后关闭当前界面。

2.2. Import Assignments方式步骤1:新建一个txt文件(或csv文件),按图3格式编写管脚分配内容。

(编写格式有多种,但这种格式最简单。

)【注】To和Location两个关键字中间有一个半角逗。

图3 管脚分配格式步骤2:在Quartus II软件中,选择“Assignments Import Assignments”,出现如图4所示的画面,导入xxx.txt或者xxx.csv文件。

图4 Import Assginments导入后Quartus II软件的Message信息栏会弹出如图5所示的内容,显示Import Completed,表示文件没有语法错误。

图5 Message步骤3:在Quartus II软件中,选择“Assignments Pin Planner”,验证管脚是否分配正确。

如图6所示。

图6 验证管脚是否分配正确常见错误1:分配的管脚不属于FPGA芯片。

如果分配的管脚不属于FPGA芯片,在Pin Planner中会出现如图7所示的错误提示,表示管脚PIN_GC21不属于该FPGA芯片,找不到对应的I/O Bank和VREF Group。

图7 管脚不属于FPGA若信号比较多,人工不能发现存在的错误,可以通过Enable Live I/O Check工具检查I/O分配情况。

点击Pin Planner工具栏中的I/O Check图标,如图8所示。

图8 Enable Live I/O Check执行Check后,在Message窗口中会弹出检查结果,如图9所示,提示PIN_GC21是非法的管脚定义。

图9 Check检查管脚不属于FPGA常见错误2:多个信号公用一个管脚,即分配管脚冲突。

如果分配的管脚冲突,通过肉眼的方式很难发现,通过Enable Live I/O Check工具可以有效的发现存在的问题,如图10所示,提示fpga_rst_n定义的管脚G21已经被phy_clk50m信号占用。

图10 Check检查管脚冲突2.3. Tcl Scripts方式步骤1:在Quartus II软件中,选择“Assignments Remove Assignments”,出现如图11所示的画面。

此步骤用来移除已经存在的管脚分配内容,以确保分配的管脚没有因为覆盖而出现错误的情况。

【注】在执行没有管脚分配的新工程中,可跳过步骤1。

图11 Remove Assignments步骤2:新建一个tcl文件,按图12格式编写管脚分配内容。

注意关键字set_location_assignment 和-to的用法。

图12管脚分配格式步骤3:执行xxx.tcl文件。

方法1:(1)在Quartus II软件中,选择“View → Utility Windows → Tcl Console”,打开Quartus II Tcl Console,如图13所示。

图13 Tcl Console(2)将tcl文件中的内容复制到Tcl Console对话框中,如图14所示。

图14 执行管脚分配语句方法2:(1)将tcl文件添加到工程中,如图15所示。

图15 添加Tcl文件(2)在Quartus II软件中,选择“Tools Tcl Scripts”,出现如图16所示的画面。

图16 Tcl Scripts选择“Run”,执行Tcl文件。

步骤4:在Quartus II软件中,选择“Assignments Pin Planner”,验证管脚是否分配正确。

检查的方法同Import Assignments方式中的Enable Live I/O Check。

2.4. 项目组统一使用方式为了统一代码风格,便于项目管理,FPGA项目组统一使用2.3的Tcl Script方式。

在2.3的步骤3中也使用方法2,即添加Tcl文件,而非命令行。

3. 编写FPGA管脚分配文件在上文提到的3种管脚分配方法中主要包含了2种文件格式,即txt和tcl。

无论那种格式的文件都是为了阐明信号与管脚的对应关系。

编写FPGA管脚分配文件的主要任务就是要快速定位工程TOP文件中各个信号与FPGA管脚的对应关系。

通过2种方式可以定位这种关系,一种是通过查看对外PDF格式的原理图,另一种是通过查看PrjPCB格式的原理图。

推荐使用PrjPCB格式的原理图。

3.1. 查看PDF格式的原理图通过SVN下载相应工程,在工程路径中可以找到对应的原理图,如图17所示。

由于PDF格式的原理图没有目录,如图18所示,查找各个模块比较费时费力,所以不推荐这种方式。

图17 原理图路径图18 PDF格式原理图3.2. 查看PrjPCB格式的原理图查看原理图的软件有多种,我司主要使用Altium Designer软件。