FPGA配置方式及过程

- 格式:doc

- 大小:34.50 KB

- 文档页数:6

1 FPGA的上电启动原理FPGA是基于RAM结构的,当然了,也有基于FLASH结构的,但RAM结构的是主流,也是我们讨论的重点。

而RAM是易失存储器,在掉电后保存在上面的数据就丢失了,重新上电后需要再下载一次才可以。

因此,我们肯定不希望每次重新上电后都用PC去下载一次,工程实现也不允许我们这么做。

所以,通常FPGA旁边都有一颗配置芯片,它通常是一片FLASH,或者是并行或者是串行接口的。

不管是串行还是并行的FLASH,它们的启动加载原理基本相同,后面我们会专门讨论。

FPGA器件有三类配置下载方式:主动配置方式(AS)、被动配置方式(PS)和最常用的基于JTAG的配置方式。

AS和PS模式主要是将bit流下载到配置芯片中;而JTAG模式则既能将代码下载到FPGA中直接在线运行(速度快,调试时优选),也能够通过FPGA将bit流下载到配置芯片中。

由于JTAG方式灵活多用,所以我们的VIP板就只预留了JTAG接口。

AS配置方式:AS配置方式由FPGA器件引导配置操作过程,它控制着外部存储器及其初始化过程,EPCS系列配置芯片如EPCS1,EPCS4,EPCS16等配置器件专供AS模式。

使用Altera串行配置器件来完成,FPGA器件处于主动地位,配置器件处于从属地位。

配置数据通过DATA0引脚送入 FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS配置方式:PS配置方式则由外部计算机或其它控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG配置方式:JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

fpga的基本工作原理FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,它可以被编程成各种逻辑电路,具有高度的灵活性和可重构性。

FPGA在数字信号处理、图像处理、视频处理和通信等领域得到广泛应用。

本文将介绍FPGA的基本工作原理,包括FPGA的逻辑资源结构、FPGA的编程方式和FPGA的工作过程。

一、FPGA的逻辑资源结构FPGA的逻辑资源主要包括逻辑单元(Logic Units)、查找表(Look-Up Tables)和存储器单元(Memory Units)。

逻辑单元是FPGA中最基本的逻辑单元,它由逻辑门电路组成,包括与门、或门、非门等。

逻辑单元的输出可以直接与其他逻辑单元或存储器单元相连,也可以与查找表的输入相连。

逻辑单元还可以实现复杂的逻辑函数,如加法器、乘法器等。

查找表是FPGA中一个重要的组成部分,它用于存储逻辑函数的真值表,并将真值表与逻辑单元相连。

在FPGA中,查找表通常由4位或5位输入和1位输出组成。

查找表的真值表由程序员编写的逻辑函数确定,并存储在FPGA的寄存器中。

存储器单元是FPGA中另一种重要的逻辑资源,用于存储数据和程序。

FPGA中的存储器单元包括RAM、ROM和寄存器。

其中RAM和寄存器用于存储数据,ROM用于存储程序。

二、FPGA的编程方式通常,FPGA的编程方式分为两种:硬件描述语言(Hardware Description Language,HDL)和原理图编程。

硬件描述语言是一种用于描述数字电路的语言,它由一系列的语句组成,其中包括组合逻辑电路描述和时序逻辑电路描述。

常见的硬件描述语言有Verilog和VHDL等。

原理图编程是一种通过绘制逻辑图来编程的方式。

在原理图中,每个组件都是以图形的形式表示的,例如逻辑门、查找表和存储器单元等。

这些组件可以通过连接线连接起来,从而组成一个完整的数字电路。

在FPGA的工作过程中,程序员先使用硬件描述语言或原理图编写程序,并将程序编译成可被FPGA识别的字节码,然后通过编程器将字节码下载到FPGA中。

fpga内部结构组成摘要:一、FPGA 简介1.FPGA 的定义2.FPGA 的应用领域二、FPGA 内部结构组成1.FPGA 的基本组件2.FPGA 的核心部分3.FPGA 的互连资源三、FPGA 的工作原理1.FPGA 的编程过程2.FPGA 的配置方式3.FPGA 的运行机制四、FPGA 的发展趋势1.FPGA 技术的不断创新2.FPGA 在人工智能领域的应用3.FPGA 在我国的发展现状和前景正文:FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可重新配置硬件架构的集成电路,能够根据需要实时地调整硬件逻辑,适应不同的应用场景。

FPGA 内部结构组成复杂,但可以概括为基本组件、核心部分和互连资源三个部分。

首先,FPGA 的基本组件主要包括可编程逻辑单元(PLU)、输入输出模块(I/O)、时钟管理模块等。

其中,可编程逻辑单元是FPGA 的核心部分,可以根据用户需求实现不同的逻辑功能。

输入输出模块负责与外部设备进行数据交互,时钟管理模块则负责时钟信号的生成、分配和同步等功能。

其次,FPGA 的核心部分是可编程逻辑资源,主要包括查找表(LUT)、寄存器(Register)和互联线(Interconnect)。

查找表用于实现逻辑函数的查找,寄存器用于存储数据和状态信息,互联线则负责在各个逻辑单元之间传输信号。

通过这些核心部分,FPGA 可以实现各种复杂的逻辑功能。

最后,FPGA 的互连资源是连接各个逻辑单元的关键部分,负责实现逻辑单元之间的信号传输和组合。

互连资源的性能直接影响FPGA 的性能和容量。

FPGA 的工作原理是通过编程过程将用户设计的逻辑功能配置到FPGA 内部,配置方式有比特流(Bitstream)和直接编程(Direct Programming)两种。

在运行过程中,FPGA 根据配置的逻辑功能进行信号处理和计算。

随着科技的不断发展,FPGA 技术也在不断创新。

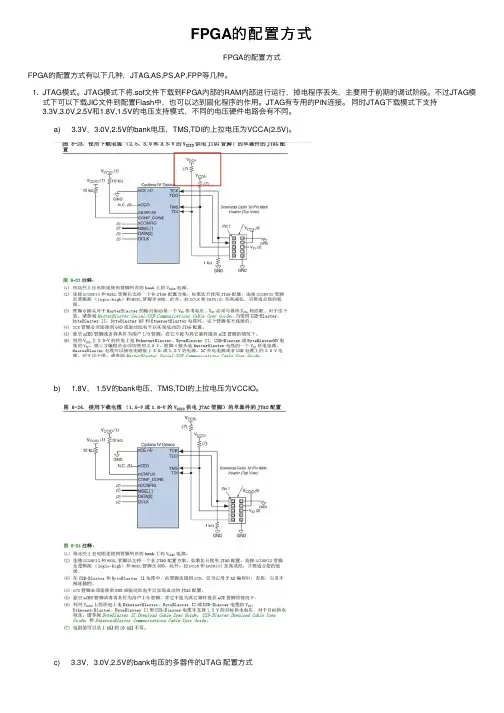

FPGA的配置⽅式FPGA的配置⽅式FPGA的配置⽅式有以下⼏种,JTAG,AS,PS,AP,FPP等⼏种。

1. JTAG模式。

JTAG模式下将.sof⽂件下载到FPGA内部的RAM内部进⾏运⾏,掉电程序丢失,主要⽤于前期的调试阶段。

不过JTAG模式下可以下载JIC⽂件到配置Flash中,也可以达到固化程序的作⽤。

JTAG有专⽤的PIN连接。

同时JTAG下载模式下⽀持3.3V,3.0V,2.5V和1.8V,1.5V的电压⽀持模式,不同的电压硬件电路会有不同。

a) 3.3V,3.0V,2.5V的bank电压,TMS,TDI的上拉电压为VCCA(2.5V)。

b) 1.8V, 1.5V的bank电压,TMS,TDI的上拉电压为VCCIO。

c) 3.3V,3.0V,2.5V的bank电压的多器件的JTAG 配置⽅式 d) 1.8V,1.5V的bank电压的多器件的JTAG 配置⽅式 e) 还可以⽤⼀台微处理器对FPGA进⾏JTAG配置。

2、AS配置模式。

AS配置模式是将sof⽂件下载外部Flash中,达到上电FPGA主动去加载程序的作⽤。

掉电程序不丢失。

a) 单器件的AS配置⽅式: b) 多器件的AS配置⽅式:的情况。

ii. 单个sof⽂件配置多个FPGA的情况。

3、AP下载模式。

AP仅在Cyclone IV E中⽀持。

(外部10pin接⼝座怎么连??下载的还是sof⽂件??) a) 单个芯⽚的AP模式。

b) 多个芯⽚的AP模式:4、PS配置模式: a) 使⽤外部微处理器来配置单个FPGA。

b) 使⽤微处理器来配置多个FPGA。

有从下⾯两种⽅案,区别为:上⾯⽅案是顺序加载,其中⼀个加载错误则整个系统就重新加载,下图是可以同时进⾏加载。

c) 使⽤下载线PS⽅式来配置单个FPGA。

d) 使⽤下载线PS⽅式来配置多个FPGA。

5、FPP的配置⽅式: a) 使⽤微处理器 FPP⽅式配置单个FPGA。

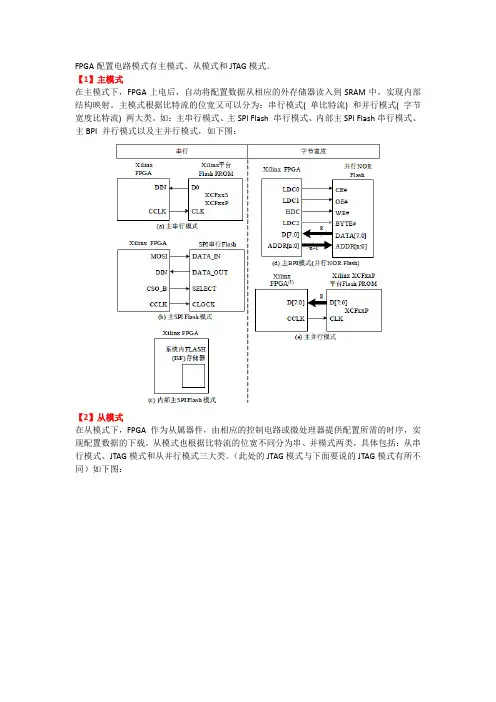

FPGA配置电路模式有主模式、从模式和JTAG模式。

【1】主模式在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射。

主模式根据比特流的位宽又可以分为:串行模式( 单比特流) 和并行模式( 字节宽度比特流) 两大类。

如:主串行模式、主SPI Flash 串行模式、内部主SPI Flash串行模式、主BPI 并行模式以及主并行模式,如下图:【2】从模式在从模式下,FPGA 作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。

从模式也根据比特流的位宽不同分为串、并模式两类,具体包括:从串行模式、JTAG模式和从并行模式三大类。

(此处的JTAG模式与下面要说的JTAG模式有所不同)如下图:【3】JTAG模式在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

主串模式是最常用的配置模式在FPGA主串配置模式下,会发现两种不同的连接方式:一种是FPGA在前,PROM在后。

即JTAG接口的DTI连接至FPGA的DTI,FPGA的DTO连接至PROM的DTI,PROM的DTO连接至JTAG接口的DTO。

另一种是PROM在前,FPGA在后。

即JTAG接口的DTI连接至PROM的DTI,PROM的DTO 连接至FPGA的DTI,FPGA的DTO连接至JTAG接口的DTO。

这两种连接方式都是正确的,都可以。

但是,由于PC机配置JTAG链的时候需要和第一级JTAG 设备同步,如果FPGA放在第一级,那么其配置速度较高,导致对PROM配置可能会不稳定,所以推荐的配置是将PROM作为JTAG链的第一级JTAG设备,即上述第二种方式。

在Xilinx 的PROM芯片XCF01/2/4S手册中给出的主串模式下(Configuring in Master Serial Mode)的连接图也是第二种方式,如下图:那FPGA在前的情况如下图:主串配置电路的关键点主串配置最关键的3点就是JTAG链的完整性、电源电压的设置以及CCLK信号的考虑。

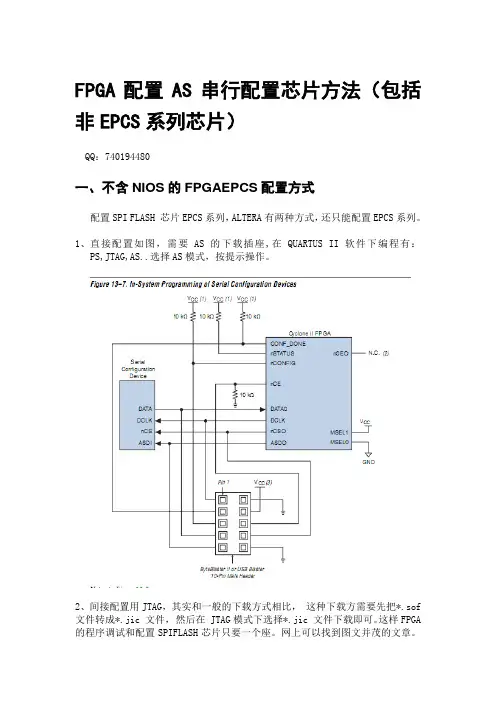

FPGA配置AS串行配置芯片方法(包括非EPCS系列芯片)QQ:740194480一、不含NIOS的FPGAEPCS配置方式配置SPI FLASH 芯片EPCS系列,ALTERA有两种方式,还只能配置EPCS系列。

1、直接配置如图,需要AS的下载插座,在QUARTUS II软件下编程有:PS,JTAG,AS..选择AS模式,按提示操作。

2、间接配置用JTAG,其实和一般的下载方式相比,这种下载方需要先把*.sof 文件转成*.jic 文件,然后在 JTAG模式下选择*.jic 文件下载即可。

这样FPGA 的程序调试和配置SPIFLASH芯片只要一个座。

网上可以找到图文并茂的文章。

《使用 JTAG 方式配置 EPCS芯片》。

二、epcs系列存配置与程序a)在SOPC builder里添加EPCS Device Controller Core,修改cpu里ResetVector为epcs_flash_controller。

b)编译后把sof文件格式转换成flash文件格式 sof2flash --epcs--input=example.sof --output=sof.flashc)把elf文件格式转换成flash文件格式: elf2flash --epcs--after=sof.flash --input=hello_word.elf--output=hello_epcs4.flash --boot=boot_loader_epcs.srec--after=sof.flash这是关键地方,必须把sof文件转换成的flash加上。

d)最后把程序通过JTAG下载到配置芯片 Nios2-flash-programmer --epcs--base=0x00001800 sof.flash Nios2-flash-programmer --epcs--base=0x00001800 hello_epcs4.flash 其中0x00001800基地址取决于SOPC builder中的定义,在烧写flash文件之前可能需先烧写example.sof文件。

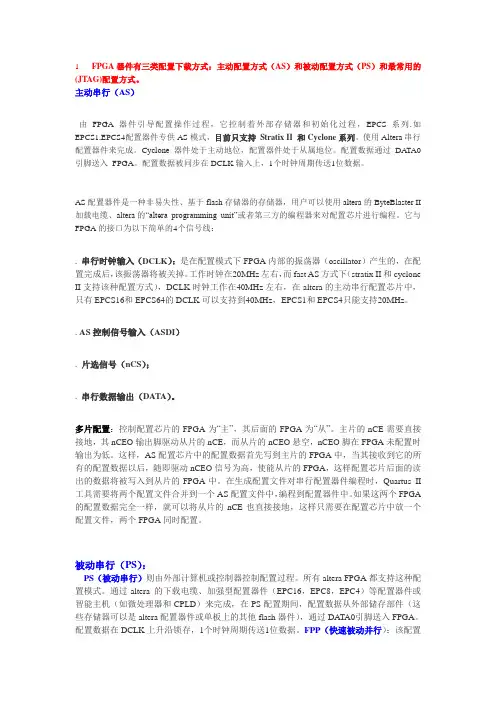

1 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

主动串行(AS)由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Stratix II 和Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

配置数据通过DA TA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

AS配置器件是一种非易失性、基于flash存储器的存储器,用户可以使用altera的ByteBlaster II 加载电缆、altera的“altera programming unit”或者第三方的编程器来对配置芯片进行编程。

它与FPGA的接口为以下简单的4个信号线:. 串行时钟输入(DCLK):是在配置模式下FPGA内部的振荡器(oscillator)产生的,在配置完成后,该振荡器将被关掉。

工作时钟在20MHz左右,而fast AS方式下(stratix II和cyclone II支持该种配置方式),DCLK时钟工作在40MHz左右,在altera的主动串行配置芯片中,只有EPCS16和EPCS64的DCLK可以支持到40MHz,EPCS1和EPCS4只能支持20MHz。

. AS控制信号输入(ASDI). 片选信号(nCS);. 串行数据输出(DATA)。

多片配置:控制配置芯片的FPGA为“主”,其后面的FPGA为“从”。

主片的nCE需要直接接地,其nCEO输出脚驱动从片的nCE,而从片的nCEO悬空,nCEO脚在FPGA未配置时输出为低。

这样,AS配置芯片中的配置数据首先写到主片的FPGA中,当其接收到它的所有的配置数据以后,随即驱动nCEO信号为高,使能从片的FPGA,这样配置芯片后面的读出的数据将被写入到从片的FPGA中。

用ARM对FPGA进行配置的原理与方法

0引言

基于SRAM工艺FPGA在每次上电后需要进行配置,通常情况下FPGA的

配置文件由片外专用的EPROM来加载。

这种传统配置方式是在FPGA的功能相对稳定的情况下采用的。

在系统设计要求配置速度高、容量大、以及远程升级时,这种方法就显得很不实际也不方便。

本文介绍了通过ARM对可编程器件进行配置的的设计和实现。

1 配置原理与方式

1.1配置原理

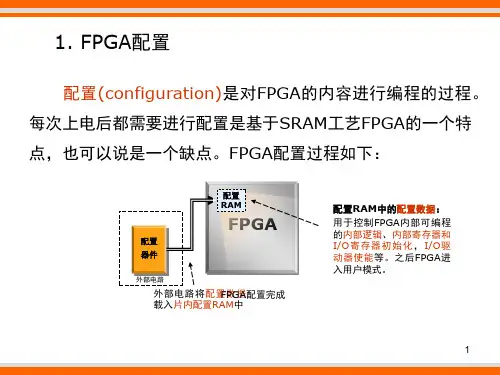

在FPGA正常工作时,配置数据存储在SRAM单元中,这个SRAM单元也被称为配置存储器(Configuration RAM)。

由于SRAM是易失性的存储器,因此FPGA在上电之后,外部电路需要将配置数据重新载入到片内的配置RAM中。

在芯片配置完成后,内部的寄存器以及I/O管脚必须进行初始化。

等初始化完成以后,芯片才会按照用户设计的功能正常工作。

1.2配置方式

根据FPGA在配置电路中的角色,其配置数据可以使用3种方式载入到目标器件中:

-FPGA主动(Active)方式;

-FPGA 被动(Passive)方式;

-JTAG 方式;

在FPGA 主动方式下,由目标FPGA来主动输出控制和同步信号(包括配置时钟)给专用的一种串行配置芯片,在配置芯片收到命令后,就把配置数据发到FPGA,完成配置过程。

在被动方式下,由系统中的其他设备发起并控制配置。

FPGA开发板使用手册一、硬件概述FPGA开发板是一种基于可编程逻辑器件(FPGA)的嵌入式系统开发板,它为电子工程师提供了一个高度灵活和可定制的平台,可用于开发各种数字系统,如通信、控制、数据处理等。

本手册旨在帮助用户了解和使用这款FPGA开发板,充分发挥其性能和功能。

二、开发板规格本开发板规格如下:1. 尺寸:90mm x 60mm x 1.6mm。

2. FPGA型号:Xilinx XC7020。

3. 内存容量:128MB DDR3。

4. 存储器:8GB eMMC。

5. 接口类型:USB 2.0,以太网 10/100Mbps,RS232等。

6. 电源电压:5V。

7. 重量:约15克。

三、硬件连接本开发板可通过以下方式与外围设备连接:1. USB接口:用于连接电脑进行编程和调试。

2. 以太网接口:用于连接网络。

3. RS232接口:用于连接其他串口设备。

4. GPIO接口:用于连接其他数字设备。

5. I2C接口:用于连接I2C总线设备。

6. SPI接口:用于连接SPI总线设备。

7. HDMI接口:用于显示输出。

8. SRAM接口:用于高速数据存储。

9. UART接口:用于串口通信。

四、FPGA设计工具安装与使用FPGA设计工具是用于编写和调试FPGA逻辑代码的软件环境。

本开发板支持的FPGA设计工具有Xilinx Vivado和Intel Quartus等。

用户需要根据所选工具,下载并安装相应的软件,然后按照软件说明进行安装和配置。

在安装过程中,请注意选择与本开发板兼容的版本和配置。

安装完成后,用户可以使用FPGA设计工具编写逻辑代码,并通过开发板的接口将代码下载到FPGA中运行。

五、FPGA设计基本原则在FPGA设计中,需要遵循以下基本原则:1. 模块化设计:将复杂问题分解为多个简单的子问题,逐个解决,便于调试和维护。

2. 尽量使用硬件加速器:利用FPGA的并行处理能力,提高系统性能。

主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS模式(active serial configuration mode):FPGA器件每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程配置数据通过DATA0引脚送入FPGA,配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS模式(passive serial configuration mode):则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,EPCS作为控制器件,把FPGA当作存储器,把数据写人到FPGA中,实现对FPGA的编程。

该模式可以实现对FPGA在线可编程。

在下载配置的时候对于Cyclone II的器件,如EP2C8,在JTAG下载方式对应.sof,AS下载方式对应.pof。

JTAG:JTAG是直接烧到FPGA里面的,由于是SRAM,断电后要重烧;AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里。

一般情况下,Cyclone II开发板上应该有两种下载模式,AS和JTAG。

AS就是下载.pof文件到EPCS中。

而JTAG就是下载.sof文件到FPGA中的RAM中。

2.烧写步骤:一)打开软件—>tools—>Programmer,弹出对话框。

点击hardware setup,再点击Add hardware选择添加你的烧写工具。

二)回到对话框,Delete窗口中的文件,点击Add files添加你的新文件(.sof格式),在program/configure中打钩。

三)点击Start按钮,下载开始。

FPGA的配置/加载方式FPGA有多种配置/加载方式。

粗略可以分为主动和被动两种。

主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

最常见的被动配置模式就是JTAG下载bit文件。

此模式下,主动发起操作的设备是计算机,数据通路是JTAG,FPGA会被动接收数据,根据需要的操作来进行更新FPGA配置。

而上位机如何获取配置数据就非常灵活了,可能是本地运行EDA工具生成的,也可以是网络/USB存储设备获取的。

主动配置就是FPGA在配置过程中处于主导地位,主动发起对Flash的读写,获取配置信息进行配置。

下面利用间EDA工具自带的烧录Flash的操作为例,分析一下具体的烧录过程。

通常情况下,完整的过程是:1.上位机主动发起配置,FPGA被动接收数据进行重配置,此时的配置模式是上文提到的基于JTAG的被动配置。

此操作的结果是将FPGA配置为一个Flash的读写器。

2.配置完成后,上位机开始发送/接收Flash的数据,数据通道为JTAG。

FPGA通过JTAG 接收到数据之后,根据需求发起对Flash的读写操作,将需要更新的数据写入Flash,完成更新。

此过程是更新Flash的过程,烧录过程中Flash只收到FPGA的控制。

3.Flash更新完毕后,在合适的时候让FPGA进行重新配置(例如重新上下电),FPGA会开始主动配置过程,从Flash中读取配置数据完成加载。

Intel(Altera)的这种模式使用的文件后缀是jic,全称是JTAG Indirect Configuration File。

直接翻译是JTAG间接配置文件。

在Quartus的Programmer界面中,当添加了Jic文件之后,可以看到有一个Factory default SFL image,就是将FPGA配置为Flash控制器的镜像。

根据配置的不同,也可以分为主动更新和被动更新两种。

如果是被动更新,那么通常配置过程会有一个主动发起的设备,常见有MCU。

fpga的配置流程

FPGA的配置流程分为设计、综合、布局布线、生成比特流、下载五个步骤。

1. 设计:首先,在设计软件中画出功能图,实现所需功能。

2. 综合:将设计好的功能图与设计文档进行综合,生成电路网表。

3. 布局布线:将生成的电路网表翻译成可以实际生产的芯片图,并进行布线。

4. 生成比特流:将布局布线后的电路图生成对应的bits流,bits流是一种二进制的数字编码格式。

5. 下载:通过编程器将生成的bits流下载到FPGA芯片中,实现所需的功能。

以上是FPGA的配置流程,需要注意的是,不同的FPGA厂家、不同型号之间的配置流程有所区别,需要按照厂家提供的官方文档进行操作。

FPGA的下载方式〔配置方式)与掉电不丧失下载下载FPGA里面 有三种方式JTAG下载sof文件,掉电丧失ﻫ 可以将sof转换为jic文件,用EPCSx配置,掉电不丧失AS 下载pof文件,配置EPCSx,掉电不丧失ﻫPS 比拟老的下载方式,很少使用更新:解释下JTAG下的掉电不丧失下载方法JTAG接口的EPCS间接编程:用JTAG模式下载,其本身模式只是用于调试,因此该模式为掉电丧失模式。

但是,在JTAG模式下可以通过配置映像的方式,对EPCS配置芯片进展编程配置。

它是利用FPGA的JTAG接口以及Altera提供的用于编程时配置FPGA 的Serial FlashLoader〔SFL〕来对EPCS进展配置.其配置的接口连接方式与JTAG一样。

通过SFL,利用FPGA作为JTAG接口和串行配置器件EPCS的桥梁,用户通过JTAG接口来对EPCS进展在系统编程。

这是因为串行器件EPCS并不支持JTAG接口,传统的方式通过AS编程接口直接对EPCS进展编程.CPLD是英文Complex Programmable Logic Device的缩写,即复杂可编程逻辑器件,CPLD基于EEPROM工艺〔掉电不丧失〕,集成度相对fpga较低,以MicroCell〔包括组合局部与存放器)为根本单元.具有非挥发特性,可以重复写入。

cpld掉电数据不丧失,芯片比拟廉价,硬件设计本钱比拟低.fpga掉电数据丧失,硬件设计时要而外加配置flash芯片,或者单片机负责上电时把程序写到fpga里面,〔如果程序较大,灵活的方案为fpga+单片机+大容量的flash〕;集成度高,以LE〔包括查找表、触发器及其他〕为根本单元,有内嵌Memory、DSP等,支持IO标准丰富.具有易挥发性,需要有上电加载过程。

可以简单的理解为:cpld比拟简单,主要是逻辑运算能力,fpga=cpld+算法处理模块.2 FPGA中,中选用AS 下载pof文件,无法成功时将sof转换为jic文件,用EPCSx配置,下载时选用JTAG 下载转换后的jic文件。

1 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

主动串行(AS)由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Stratix II 和Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

配置数据通过DA TA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

AS配置器件是一种非易失性、基于flash存储器的存储器,用户可以使用altera的ByteBlaster II 加载电缆、altera的“altera programming unit”或者第三方的编程器来对配置芯片进行编程。

它与FPGA的接口为以下简单的4个信号线:. 串行时钟输入(DCLK):是在配置模式下FPGA内部的振荡器(oscillator)产生的,在配置完成后,该振荡器将被关掉。

工作时钟在20MHz左右,而fast AS方式下(stratix II和cyclone II支持该种配置方式),DCLK时钟工作在40MHz左右,在altera的主动串行配置芯片中,只有EPCS16和EPCS64的DCLK可以支持到40MHz,EPCS1和EPCS4只能支持20MHz。

. AS控制信号输入(ASDI). 片选信号(nCS);. 串行数据输出(DATA)。

多片配置:控制配置芯片的FPGA为“主”,其后面的FPGA为“从”。

主片的nCE需要直接接地,其nCEO输出脚驱动从片的nCE,而从片的nCEO悬空,nCEO脚在FPGA未配置时输出为低。

这样,AS配置芯片中的配置数据首先写到主片的FPGA中,当其接收到它的所有的配置数据以后,随即驱动nCEO信号为高,使能从片的FPGA,这样配置芯片后面的读出的数据将被写入到从片的FPGA中。

在生成配置文件对串行配置器件编程时,Quartus II 工具需要将两个配置文件合并到一个AS配置文件中,编程到配置器件中。

如果这两个FPGA 的配置数据完全一样,就可以将从片的nCE也直接接地,这样只需要在配置芯片中放一个配置文件,两个FPGA同时配置。

被动串行(PS):PS(被动串行)则由外部计算机或控制器控制配置过程。

所有altera FPGA都支持这种配置模式。

通过altera 的下载电缆、加强型配置器件(EPC16,EPC8,EPC4)等配置器件或智能主机(如微处理器和CPLD)来完成,在PS配置期间,配置数据从外部储存部件(这些存储器可以是altera配置器件或单板上的其他flash器件),通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

FPP(快速被动并行):该配置模式只有在stratix系列和APEX II中支持;PPA(被动并行异步):该配置模式在stratix 系列、APEX II、APEX 20K、mercury、ACEX 1K和FLEX 10K中支持;PPS(被动并行同步):这种模式只有一些较老的器件支持,APEX II、APEX 20K、mercury、ACEX 1K和FLEX 10K。

PSA(被动串行异步):只有在FLEX 6000器件中支持。

是使用最多的一种配置方式。

与FPGA的信号接口:. DCLK(配置时钟);. DATA0(配置数据);. nCONFIG(配置命令);. nSTATUS(状态信号);.CONF_DONE(配置完成指示)。

在PS方式下,FPGA处于完全被动的地位。

FPGA接收配置时钟、配置命令和配置数据,给出配置的状态信号以及配置完成指示信号等。

PS配置可以使用altera的配置器件(EPC1、EPC4等),可以使用系统中的微处理器,也可以使用单板上的CPLD,或者altera的下载电缆,不管配置的数据源从哪里来,只要可以模拟出FPGA需要的配置时序来,将配置数据写入FPGA就可以。

在上电以后,FPGA会在nCONFIG管脚上检测到一个从低到高的跳变沿,因此可以自动启动配置过程。

支持多片配置方式。

JTAG配置方式:JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

JTAG接口是一个业界标准接口,主要用于芯片测试等功能。

altera FPGA基本上都可以支持JTAG命令来配置FPGA的方式,而且JTAG配置方式比其他任何方式优先级都高。

JTAG 接口有4个必需的信号TDI, TDO, TMS和TCK以及1个可选信号TRST构成,其中:. TDI,用于测试数据的输入;. TDO,用于测试数据的输出;. TMS,模式控制管脚,决定JTAG电路内部的TAP状态机的跳变;. TCK,测试时钟,其他信号线都必须与之同步;. TRST,可选,如果JTAG电路不用,可以讲其连到GND。

用户可以使用altera的下载电缆,也可以使用微处理器等智能设备从JTAG接口设置FPGA。

nCONFIG、MESL和DCLK信号都是用在其他配置方式下。

如果只用JTAG配置,则需要将nCONFIG拉高,将MSEL拉成支持JTAG的任一方式,并将DCLK拉成高或低的固定电平。

JTAG配置方式支持菊花链方式,级联多片FPGA。

FPGA 在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA 主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

专用配置器件:epc型号的存储器常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等。

对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列.除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。

当然所外挂的电路也和PS有一些区别。

还有处理器配置比如JRUNNER 等等,如果需要再baidu吧,至少不下十种。

比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive Parallel Asynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种.2 FPGA配置过程:在FPGA正常工作时,配置数据存储在SRAM中,这个SRAM单元也被称为配置存储器(configure RAM)。

由于SRAM是易失性存储器,因此在FPGA上电之后,外部电路需要将配置数据重新载入到芯片内的配置RAM中。

在芯片配置完成之后,内部的寄存器以及I/O管脚必须进行初始化(initialization),等到初始化完成以后,芯片才会按照用户设计的功能正常工作,即进入用户模式。

FPGA上电以后首先进入配置模式(configuration),在最后一个配置数据载入到FPGA以后,进入初始化模式(initialization),在初始化完成后进入用户模式(user-mode)。

在配置模式和初始化模式下,FPGA的用户I/O处于高阻态(或内部弱上拉状态),当进入用户模式下,用户I/O 就按照用户设计的功能工作。

altera FPGA配置全过程:一个器件完整的配置过程将经历复位、配置和初始化等3个过程。

FPGA 正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态管脚nSTATUS和CONFIG_DONE管脚也将输出为低。

当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。

随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。

在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

在接收配置数据的过程中,配置数据由DATA管脚送入,而配置时钟信号由DCLK管脚送入,配置数据在DCLK的上升沿被锁存到FPGA中,当配置数据被全部载入到FPGA中以后,FPGA 上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。

因此,CONF_DONE管脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该管脚。

在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。

当初始化完成以后,器件上漏极开始输出的INIT_DONE管脚被释放,同时被外部的上拉电阻拉高。

这时,FPGA完全进入用户模式,所有的内部逻辑以及I/O都按照用户的设计运行,这时,那些FPGA配置过程中的I/O弱上拉将不复存在。

不过,还有一些器件在用户模式下I/O也有可编程的弱上拉电阻。

在完成配置以后,DCLK信号和DA TA管脚不应该被浮空(floating),而应该被拉成固定电平,高或低都可以。

如果需要重新配置FPGA,就需要在外部将nCONFIG重新拉低一段时间,然后再拉高。

当nCONFIG被拉低吼,nSTATUS和CONF_DONE也将随即被FPGA芯片拉低,配置RAM被清,所有I/O都变成三态。

当nCONFIG和nSTATUS都变为高时,重新配置就开始了。

3对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。

让配置方式在跳线中切换,上拉电阻的阻值可以采用10K4在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号。