时序逻辑电路的应用举例共18页文档

- 格式:ppt

- 大小:3.11 MB

- 文档页数:18

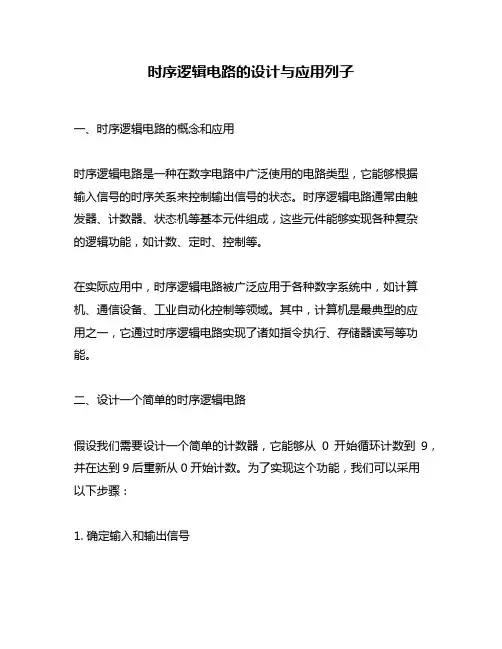

时序逻辑电路的设计与应用列子一、时序逻辑电路的概念和应用时序逻辑电路是一种在数字电路中广泛使用的电路类型,它能够根据输入信号的时序关系来控制输出信号的状态。

时序逻辑电路通常由触发器、计数器、状态机等基本元件组成,这些元件能够实现各种复杂的逻辑功能,如计数、定时、控制等。

在实际应用中,时序逻辑电路被广泛应用于各种数字系统中,如计算机、通信设备、工业自动化控制等领域。

其中,计算机是最典型的应用之一,它通过时序逻辑电路实现了诸如指令执行、存储器读写等功能。

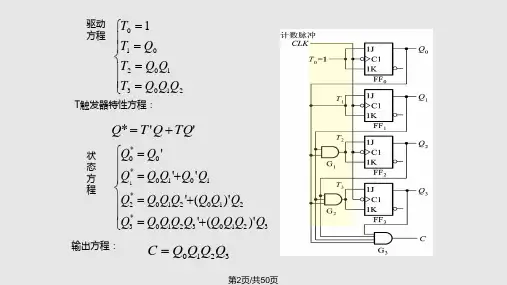

二、设计一个简单的时序逻辑电路假设我们需要设计一个简单的计数器,它能够从0开始循环计数到9,并在达到9后重新从0开始计数。

为了实现这个功能,我们可以采用以下步骤:1. 确定输入和输出信号首先,我们需要确定输入和输出信号。

对于这个计数器而言,输入信号可以是一个时钟脉冲信号(CLK),每当CLK上升沿到来时就进行一次计数操作;输出信号可以是一个4位二进制数码(BCD),用于表示当前的计数值。

2. 选择适当的触发器为了实现计数操作,我们需要使用一个触发器来存储当前的计数值,并在时钟脉冲到来时更新计数值。

在这个例子中,我们可以选择一个4位D触发器作为存储器,它能够存储4位二进制数。

3. 设计逻辑电路根据计数器的功能要求,我们需要设计一组逻辑电路来实现以下功能:(1)初始化:当CLK上升沿到来时,如果当前计数值为9,则将其清零(即重新开始计数);否则将其加1。

(2)输出:将当前的二进制计数值转换为4位BCD码,并输出到外部接口。

为了实现这些功能,我们可以采用以下电路设计:首先,我们需要将CLK信号输入到一个D触发器中,并设置其初始状态为0。

每当CLK上升沿到来时,该触发器会将其输入端的信号存储到输出端,并且同时产生一个反相输出Q'信号。

接下来,我们需要将Q'信号输入到一个与门中,并且将该门的另一输入端连接到一个4位全加器中。

全加器的另一输入端连接到一个常量1信号源。

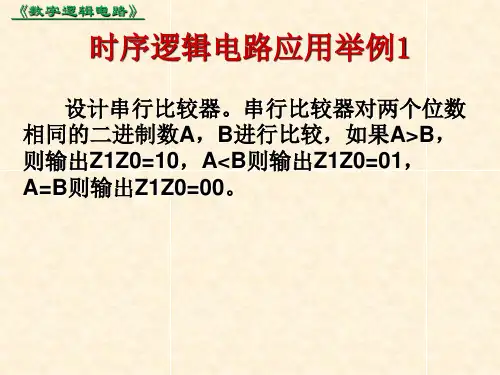

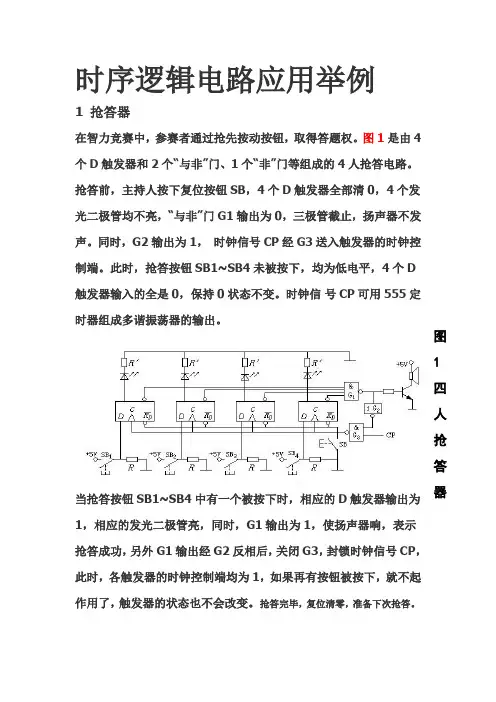

时序逻辑电路应用举例1 抢答器在智力竞赛中,参赛者通过抢先按动按钮,取得答题权。

图1是由4个D触发器和2个“与非”门、1个“非”门等组成的4人抢答电路。

抢答前,主持人按下复位按钮SB,4个D触发器全部清0,4个发光二极管均不亮,“与非”门G1输出为0,三极管截止,扬声器不发声。

同时,G2输出为1,时钟信号CP经G3送入触发器的时钟控制端。

此时,抢答按钮SB1~SB4未被按下,均为低电平,4个D 触发器输入的全是0,保持0状态不变。

时钟信号CP可用555定时器组成多谐振荡器的输出。

当抢答按钮SB1~SB4中有一个被按下时,相应的D触发器输出为1,相应的发光二极管亮,同时,G1输出为1,使扬声器响,表示抢答成功,另外G1输出经G2反相后,关闭G3,封锁时钟信号CP,此时,各触发器的时钟控制端均为1,如果再有按钮被按下,就不起作用了,触发器的状态也不会改变。

抢答完毕,复位清零,准备下次抢答。

图1四人抢答器2。

八路彩灯控制器八路彩灯控制器由编码器、驱动器和显示器(彩灯)组成,编码器根据彩灯显示的花型按节拍送出八位状态编码信号,通过驱动器使彩灯点亮、熄灭。

图2给出的八路彩灯控制器电路图中,编码器用两片双向移位寄存器74LS194实现,接成自启动脉冲分配器(扭环形计数器),其中D1为左移方式,D2为右移方式。

驱动器电路如图3,当寄存器输出Q为高电平时,三极管T导通,继电器K通电,其动合触点闭合,彩灯亮;当Q为低电平时,三极管截止,继电器复位,彩灯灭。

图2 八路彩灯控制器电路工作时,先用负脉冲清零,使寄存器输出全部为0,然后在节拍脉冲(可由555定时器构成的多谐振荡器输出)的控制下,寄存器的各个输出Q按下表所示的状态变化,每8个节拍重复一次。

这里假定8路彩灯的花型是:由中间向两边对称地逐次点亮,全亮后,再由中间向两边逐次熄灭。

图3 驱动器电路寄存器输出状态3 数字钟在许多场合大量使用的数字电子钟,具有显示时、分、秒,以及自动计时和校正对时的功能。