时序逻辑电路应用举例1

- 格式:pdf

- 大小:113.53 KB

- 文档页数:17

时序逻辑电路cp脉冲信参与输出时序逻辑电路是一种特殊类型的数字电路,其输出状态不仅取决于当前输入信号,还取决于输入信号的先前状态。

时序逻辑电路能够用于实现计数器、寄存器、状态机等电路,广泛应用于数字逻辑系统中。

在时序逻辑电路中,时钟信号是非常重要的一个输入信号。

时钟信号通常以周期性的脉冲信号形式存在,它会定时触发电路中的各个逻辑门或触发器。

当时钟信号上升沿或下降沿到来时,电路中的计算、存储或状态转换等操作会被触发。

因此,时钟信号的频率和相位是时序逻辑电路设计中需要考虑的重要因素之一。

时序逻辑电路中的脉冲信号也是一种重要的参与输出的信号。

脉冲信号使时序逻辑电路能够在特定的时钟脉冲到来时,对输入信号进行处理并生成输出信号。

举例来说,假设我们设计了一个简单的4位二进制计数器。

计数器需要从0开始依次计数到15,然后再回到0重新计数。

在这个计数器电路中,时钟信号驱动计数器进行计数操作,而脉冲信号则用于检测计数值是否达到15,如果达到15,则产生一个输出脉冲信号来表示计数器已经溢出。

具体实现时,我们可以使用触发器来存储当前计数值。

在每个时钟脉冲到来时,计数器会根据当前计数值进行加1操作,并将加1后的结果存储回触发器中。

当计数值为15时,则产生一个脉冲信号来表示溢出。

在这个例子中,脉冲信号直接参与计数器的输出,用于表示计数器是否溢出。

这种设计方式非常常见,在许多应用中都能见到。

脉冲信号作为一种简洁、高效的输出形式,通常用于表示某些特定事件的发生或状态的改变。

除了计数器,时序逻辑电路中的脉冲信号还可以用于实现状态机。

状态机是一种能够根据输入信号的不同而切换不同状态的电路。

在状态机中,脉冲信号通常用于触发状态的转换。

当输入信号满足某些条件时,状态机会生成一个脉冲信号,该脉冲信号用于切换到下一个状态或执行某个特定的操作。

总的来说,时序逻辑电路中的脉冲信号是一种重要的参与输出的信号。

脉冲信号能够在特定的时钟脉冲到来时,实现一些特定的操作,如计数、状态转换等。

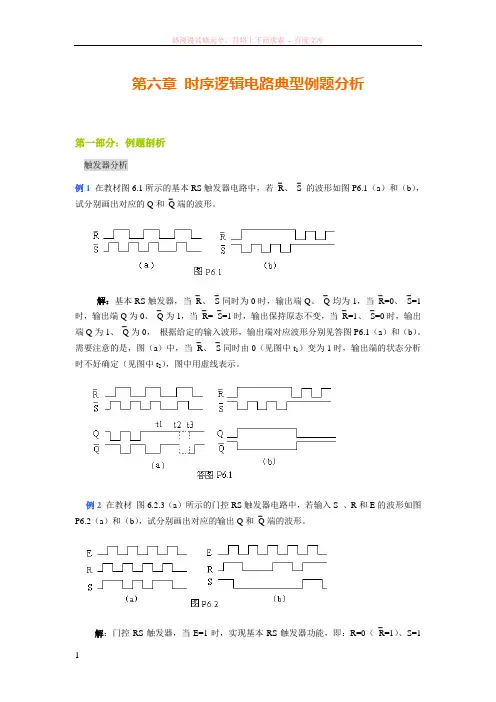

第六章时序逻辑电路典型例题分析第一部分:例题剖析触发器分析例1在教材图6.1所示的基本RS触发器电路中,若⎺R、⎺S 的波形如图P6.1(a)和(b),试分别画出对应的Q和⎺Q端的波形。

解:基本RS触发器,当⎺R、⎺S同时为0时,输出端Q、⎺Q均为1,当⎺R=0、⎺S=1时,输出端Q为0、⎺Q为1,当⎺R=⎺S=1时,输出保持原态不变,当⎺R=1、⎺S=0时,输出端Q为1、⎺Q为0,根据给定的输入波形,输出端对应波形分别见答图P6.1(a)和(b)。

需要注意的是,图(a)中,当⎺R、⎺S同时由0(见图中t1)变为1时,输出端的状态分析时不好确定(见图中t2),图中用虚线表示。

例2 在教材图6.2.3(a)所示的门控RS触发器电路中,若输入S 、R和E的波形如图P6.2(a)和(b),试分别画出对应的输出Q和⎺Q端的波形。

解:门控RS触发器,当E=1时,实现基本RS触发器功能,即:R=0(⎺R=1)、S=1(⎺S=0),输出端Q为1、⎺Q为0;R=1(⎺R=0)、S=0(⎺S=1)输出端Q为0、⎺Q为1;当E=0时,输出保持原态不变。

输出端波形见答图P6.2。

例3在教材图6.2.5所示的D锁存器电路中,若输入D、E的波形如图P6.3(a)和(b)所示,试分别对应地画出输出Q和Q端的波形。

解:D锁存器,当E=1时,实现D锁存器功能,即:Q n+1=D,当E=0时,输出保持原态不变。

输出端波形见答图P6.3。

例4在图P6.4(a)所示的四个边沿触发器中,若已知CP、A、B的波形如图(b)所示,试对应画出其输出Q端的波形。

设触发器的初始状态均为0。

解:图中各电路为具有异步控制信号的边沿触发器。

图(a)为边沿D触发器,CP上升沿触发,Q1n+1= A,异步控制端S D接信号C(R D=0),当C=1时,触发器被异步置位,输出Q n+1=1 ;图(b)为边沿JK触发器,CP上升沿触发,Q2n+1= A⎺Q2n +⎺BQ2n,异步控制端⎺R D接信号C(⎺S D =1),当C=0时,触发器被异步复位,输出Q n+1=0;图(c)为边沿D触发器,CP下降沿触发,Q3n+1= A,异步控制端⎺S D接信号C(⎺R D =1),当C=0时,触发器被异步置位,输出Q n+1=1;图(d)为边沿JK触发器,CP下降沿触发,Q4n+1= A⎺Q4n +⎺BQ4n,异步控制端R D接信号C(S D =0),当C=1时,触发器被异步复位,输出Q n+1=0。

第五章时序逻辑电路前面介绍的组合逻辑电路无记忆功能。

而时序逻辑电路的输出状态不仅取决于当时的输入信号,而且与电路原来的状态有关,或者说与电路以前的输入状态有关,具有记忆功能。

触发器是时序逻辑电路的基本单元。

本章讨论的内容为时序逻辑电路的分析方法、寄存器和计数器的原理及应用。

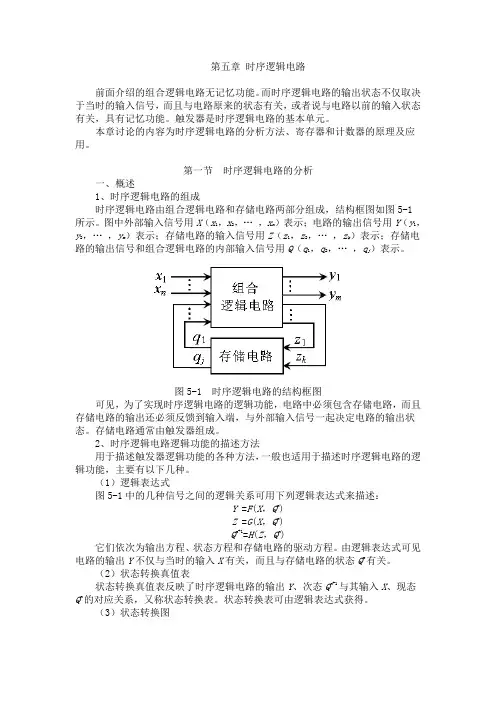

第一节时序逻辑电路的分析一、概述1、时序逻辑电路的组成时序逻辑电路由组合逻辑电路和存储电路两部分组成,结构框图如图5-1所示。

图中外部输入信号用X(x1,x2,…,x n)表示;电路的输出信号用Y(y1,y,…,y m)表示;存储电路的输入信号用Z(z1,z2,…,z k)表示;存储电2路的输出信号和组合逻辑电路的内部输入信号用Q(q1,q2,…,q j)表示。

图5-1 时序逻辑电路的结构框图可见,为了实现时序逻辑电路的逻辑功能,电路中必须包含存储电路,而且存储电路的输出还必须反馈到输入端,与外部输入信号一起决定电路的输出状态。

存储电路通常由触发器组成。

2、时序逻辑电路逻辑功能的描述方法用于描述触发器逻辑功能的各种方法,一般也适用于描述时序逻辑电路的逻辑功能,主要有以下几种。

(1)逻辑表达式图5-1中的几种信号之间的逻辑关系可用下列逻辑表达式来描述:Y =F(X,Q n)Z =G(X,Q n)Q n+1=H(Z,Q n)它们依次为输出方程、状态方程和存储电路的驱动方程。

由逻辑表达式可见电路的输出Y不仅与当时的输入X有关,而且与存储电路的状态Q n有关。

(2)状态转换真值表状态转换真值表反映了时序逻辑电路的输出Y、次态Q n+1与其输入X、现态Q n的对应关系,又称状态转换表。

状态转换表可由逻辑表达式获得。

(3)状态转换图状态转换图又称状态图,是状态转换表的图形表示,它反映了时序逻辑电路状态的转换与输入、输出取值的规律。

(4)波形图波形图又称为时序图,是电路在时钟脉冲序列CP的作用下,电路的状态、输出随时间变化的波形。

应用波形图,便于通过实验的方法检查时序逻辑电路的逻辑功能。

常用的时序逻辑电路时序逻辑电路是数字电路中一类重要的电路,它根据输入信号的顺序和时序关系,产生对应的输出信号。

时序逻辑电路主要应用于计时、控制、存储等领域。

本文将介绍几种常用的时序逻辑电路。

一、触发器触发器是一种常见的时序逻辑电路,它具有两个稳态,即SET和RESET。

触发器接受输入信号,并根据输入信号的变化产生对应的输出。

触发器有很多种类型,常见的有SR触发器、D触发器、JK 触发器等。

触发器在存储、计数、控制等方面有广泛的应用。

二、时序计数器时序计数器是一种能按照一定顺序计数的电路,它根据时钟信号和控制信号进行计数。

时序计数器的输出通常是一个二进制数,用于驱动其他电路的工作。

时序计数器有很多种类型,包括二进制计数器、BCD计数器、进位计数器等。

时序计数器在计时、频率分频、序列生成等方面有广泛的应用。

三、时序比较器时序比较器是一种能够比较两个信号的大小关系的电路。

它接受两个输入信号,并根据输入信号的大小关系产生对应的输出信号。

时序比较器通常用于判断两个信号的相等性、大小关系等。

常见的时序比较器有两位比较器、四位比较器等。

四、时序多路选择器时序多路选择器是一种能够根据控制信号选择不同输入信号的电路。

它接受多个输入信号和一个控制信号,并根据控制信号的不同选择对应的输入信号作为输出。

时序多路选择器常用于多路数据选择、时序控制等方面。

五、时序移位寄存器时序移位寄存器是一种能够将数据按照一定规律进行移位的电路。

它接受输入信号和时钟信号,并根据时钟信号的变化将输入信号进行移位。

时序移位寄存器常用于数据存储、数据传输等方面。

常见的时序移位寄存器有移位寄存器、移位计数器等。

六、状态机状态机是一种能够根据输入信号和当前状态产生下一个状态的电路。

它由状态寄存器和状态转移逻辑电路组成,能够实现复杂的状态转移和控制。

状态机常用于序列识别、控制逻辑等方面。

以上是几种常用的时序逻辑电路,它们在数字电路设计中起着重要的作用。

时序逻辑电路的设计与应用列子一、时序逻辑电路的概念和应用时序逻辑电路是一种在数字电路中广泛使用的电路类型,它能够根据输入信号的时序关系来控制输出信号的状态。

时序逻辑电路通常由触发器、计数器、状态机等基本元件组成,这些元件能够实现各种复杂的逻辑功能,如计数、定时、控制等。

在实际应用中,时序逻辑电路被广泛应用于各种数字系统中,如计算机、通信设备、工业自动化控制等领域。

其中,计算机是最典型的应用之一,它通过时序逻辑电路实现了诸如指令执行、存储器读写等功能。

二、设计一个简单的时序逻辑电路假设我们需要设计一个简单的计数器,它能够从0开始循环计数到9,并在达到9后重新从0开始计数。

为了实现这个功能,我们可以采用以下步骤:1. 确定输入和输出信号首先,我们需要确定输入和输出信号。

对于这个计数器而言,输入信号可以是一个时钟脉冲信号(CLK),每当CLK上升沿到来时就进行一次计数操作;输出信号可以是一个4位二进制数码(BCD),用于表示当前的计数值。

2. 选择适当的触发器为了实现计数操作,我们需要使用一个触发器来存储当前的计数值,并在时钟脉冲到来时更新计数值。

在这个例子中,我们可以选择一个4位D触发器作为存储器,它能够存储4位二进制数。

3. 设计逻辑电路根据计数器的功能要求,我们需要设计一组逻辑电路来实现以下功能:(1)初始化:当CLK上升沿到来时,如果当前计数值为9,则将其清零(即重新开始计数);否则将其加1。

(2)输出:将当前的二进制计数值转换为4位BCD码,并输出到外部接口。

为了实现这些功能,我们可以采用以下电路设计:首先,我们需要将CLK信号输入到一个D触发器中,并设置其初始状态为0。

每当CLK上升沿到来时,该触发器会将其输入端的信号存储到输出端,并且同时产生一个反相输出Q'信号。

接下来,我们需要将Q'信号输入到一个与门中,并且将该门的另一输入端连接到一个4位全加器中。

全加器的另一输入端连接到一个常量1信号源。

时序逻辑电路应用举例1 抢答器在智力竞赛中,参赛者通过抢先按动按钮,取得答题权。

图1是由4个D触发器和2个“与非”门、1个“非”门等组成的4人抢答电路。

抢答前,主持人按下复位按钮SB,4个D触发器全部清0,4个发光二极管均不亮,“与非”门G1输出为0,三极管截止,扬声器不发声。

同时,G2输出为1,时钟信号CP经G3送入触发器的时钟控制端。

此时,抢答按钮SB1~SB4未被按下,均为低电平,4个D 触发器输入的全是0,保持0状态不变。

时钟信号CP可用555定时器组成多谐振荡器的输出。

当抢答按钮SB1~SB4中有一个被按下时,相应的D触发器输出为1,相应的发光二极管亮,同时,G1输出为1,使扬声器响,表示抢答成功,另外G1输出经G2反相后,关闭G3,封锁时钟信号CP,此时,各触发器的时钟控制端均为1,如果再有按钮被按下,就不起作用了,触发器的状态也不会改变。

抢答完毕,复位清零,准备下次抢答。

图1四人抢答器2。

八路彩灯控制器八路彩灯控制器由编码器、驱动器和显示器(彩灯)组成,编码器根据彩灯显示的花型按节拍送出八位状态编码信号,通过驱动器使彩灯点亮、熄灭。

图2给出的八路彩灯控制器电路图中,编码器用两片双向移位寄存器74LS194实现,接成自启动脉冲分配器(扭环形计数器),其中D1为左移方式,D2为右移方式。

驱动器电路如图3,当寄存器输出Q为高电平时,三极管T导通,继电器K通电,其动合触点闭合,彩灯亮;当Q为低电平时,三极管截止,继电器复位,彩灯灭。

图2 八路彩灯控制器电路工作时,先用负脉冲清零,使寄存器输出全部为0,然后在节拍脉冲(可由555定时器构成的多谐振荡器输出)的控制下,寄存器的各个输出Q按下表所示的状态变化,每8个节拍重复一次。

这里假定8路彩灯的花型是:由中间向两边对称地逐次点亮,全亮后,再由中间向两边逐次熄灭。

图3 驱动器电路寄存器输出状态3 数字钟在许多场合大量使用的数字电子钟,具有显示时、分、秒,以及自动计时和校正对时的功能。

时序逻辑电路在实际中的应用时序逻辑电路是一种重要的数字逻辑电路,其特点是电路任何一个时刻的输出状态不仅取决于当时的输入信号,而且与电路的原状态有关,具有记忆功能。

构成组合逻辑电路的基本单元是逻辑门,而构成时序逻辑电路的基本单元是触发器。

时序逻辑电路在实际中的应用很广泛,数字钟、交通灯、计算机、电梯的控制盘、门铃和防盗报警系统中都能见到。

主要介绍典型的时序逻辑部件:集成计数器的识别与应用,集成寄存器的识别与应用;时序逻辑电路的分析和设计。

计数器在计算机及各种数字仪表中应用广泛,具有记忆输入脉冲个数的功能,还可以实现分频、定时等。

计数器种类繁多,按技术体制可分为二进制计数器和N进制计数器;按增减趋势可分为加计数器和减计数器;按技术脉冲引入方式可分为同步计数器和异步计数器。

同步计数器的特点是构成计数器的所有触发器共用同一个时钟脉冲,触发器的状态同时更新,计数速度快;而异步计数的特点是构成计数器的触发器不共用同一个时钟脉冲,所有触发器更新状态的时刻不一致,计数速度相对较慢。

在实际应用中,计数器是以集成电路形式存在的,主要有集成二进制计数器、集成十进制计数器两大类,其他进制计数器可由它们通过外电路设计来实现。

在每一大类计数器中,又以同步与异步、加计数与可逆计数来细分。

寄存器具有接收数码、存放或传递数码的功能,由触发器和逻辑门组成。

其中,触发器用来存放二进制数,逻辑门用来控制二进制数的接收、传送和输出。

由于一个触发器只能存放1位二进制数,因此,存放n位二进制数的n位寄存器,需要n个触发器来组成。

寄存器有数码寄存器和移位寄存器2种。

输入输出方式有并入-并出、并入-串出、串入-并出、串入-串出4种。

当寄存器的每一位数码由一个时钟脉冲控制同时接收或输出时,称为并入或并出。

而每个时钟脉冲只控制寄存器按顺序逐位移入或移出数码时,称为串入或串出。

移位寄存器除了具有存储数码的功能以外,还具有移位功能。

所谓移位功能,是指寄存器里存储的数码能在时钟脉冲作用下依次左移或右移。