《认识数据选择器和分配器 》加法器和数值比较器

- 格式:pptx

- 大小:3.13 MB

- 文档页数:8

)数据选择器

定义:根据需要将多路信号中选择一路送到公共数据线上的逻又称多路开关)。

输入端:2n个;输出端:1个。

11201110110()()(A A D A A D A A D +++12201210120()()(A A D A

A D A A D +++ 1数据选择器(74HC151、74HC25174HC251为输出三态端口,若使能输入为高电平,

100000C i C S i B i A i 00i

i i i i i i i i i B A B A C B A C B A ⊕⊕+++--11

☞ 集成4位加法器的级联——扩展为8位二进制数加法电路

例1:分析由集成四位加法器74HC283构成电路的逻辑功能。

74HC283

A 3A 2A 1A 0

B 3B 2B 1B 0

C 4

C 0

S 3S 2

S 1

S 0

"1"

反码+1=补码

组合逻辑电路中的竞争-冒险现象

(1)竞争-冒险的概念

竞争:数字电路从一个稳定状态转换到另一个稳定状态时,电路的2个输入信号出现同时向相反逻辑电平跳变的现象。

延迟:由于逻辑门的传输延迟时间和电路的负载电容、传输线分布电容效应等因素的影响,使得传输到同一个门输入端的一组信号到达的时间有先后之分。

实验十 加法器与数值比较器一、实验目的1、掌握半加器和全加器的工作原理。

2、掌握数值比较器的工作原理。

3、掌握四位数值比较器74LS85的逻辑功能。

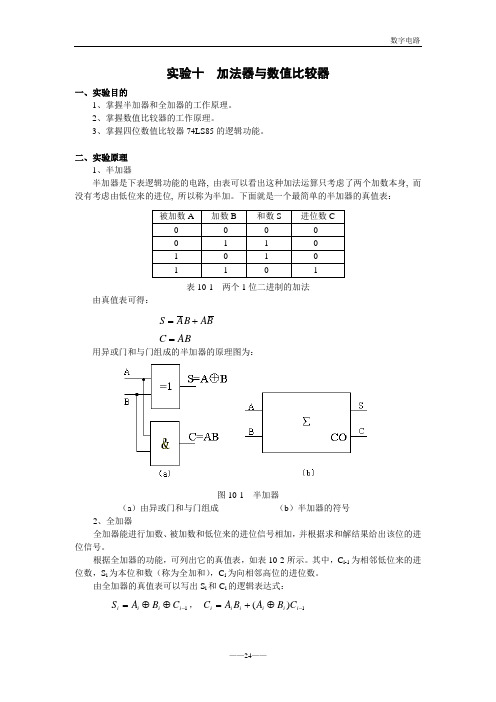

二、实验原理1、半加器半加器是下表逻辑功能的电路, 由表可以看出这种加法运算只考虑了两个加数本身, 而没有考虑由低位来的进位, 所以称为半加。

下面就是一个最简单的半加器的真值表:表10-1 两个1位二进制的加法由真值表可得:B A B A S += ABC =用异或门和与门组成的半加器的原理图为:图10-1 半加器(a )由异或门和与门组成 (b )半加器的符号2、全加器全加器能进行加数、被加数和低位来的进位信号相加,并根据求和解结果给出该位的进位信号。

根据全加器的功能,可列出它的真值表,如表10-2所示。

其中,C i-1为相邻低位来的进位数,S i 为本位和数(称为全加和),C i 为向相邻高位的进位数。

由全加器的真值表可以写出S i 和C i 的逻辑表达式: 1-⊕⊕=i i i i C B A S , 1)(-⊕+=i i i i i i C B A B A C表10-2 全加器的真值表它的原理图为:图10-2 全加器(a)由异或门、或门和与门组成(b) 全加器的符号3、数值比较器的原理在数字系统中, 常常要比较两个数的大小。

数值比较器就是对两数A、B进行比较,以判断其大小的逻辑电路。

比较结果有A>B、A<B、A=B三种情况。

下面是最简单的一位数表10-3 一位数值比较器的真值表图10-3 一位数值比较器的逻辑电路图对于多位的情况,一般说来,先比较高位,当高位不等时,两个数的比较结果就是高位的比较结果。

当高位相等时,两数的比较结果由低位决定。

4、集成数值比较器74LS85集成数值比较器74LS85是四位数值比较器,它的管脚图和真值表如下:图10-4 74LS85的管脚图其中10、12、13、15(或1、9、11、14)脚是输入端,2、3、4(或5、6、7)脚为输出端。

实验五半加器、全加器及选择器、分配器一、实验目的1. 掌握半加器、全加器及数据选择器、分配器工作原理2. 掌握数据选择器、分配器扩展方法。

3. 熟悉常用半加器、全加器及数据选择器、分配器、的管脚排列和逻辑功能。

4. 学会分析逻辑电路的逻辑方法。

二、实验器材1. 数字实验箱1台2. 集成电路:74LS00、74LS86、74LS183、74LS151、74LS138、各1片三、预习要求1.复习半加器、全加器,数据选择器、数据分配器的工作原理和特点。

2.了解本实验中所用集成电路的逻辑功能和使用方法。

3.准备好实验记录图表。

四、实验原理和电路(一)加法器加法器电路分为半加器和全加器两种。

半加器在运算时不考虑前位的进位;全加器则考虑前位的进位。

因此,全加器在电路的实现上也较复杂些。

1.半加器半加器的真值表见表4.1。

①半加器的逻辑式:图4.1 半加器逻辑电路'.(b)用异或门和与非门组成ABSC ..(a)用与非门组成BA CB A B A B A S ⋅=⊕=+=..........①若只用用“与非门”来实现,则为:ABAB C B AB A AB B A B A S ==⋅⋅⋅=+=...②注:②式中的S 也可表为:B A B A S ⋅=,仍是与非表达式且更简单。

但以②式组成的电路,在求和S 电路中,同时生成进位信号 AB C =,可节省单独生成进位C 的门。

所以实用中常使用②式的逻辑电路。

③ 半加器逻辑电路:从逻辑表达式可看出,半加器可由非门、与门 、与非门、或门、异或门等门电路组合而成。

用与非门74LS00及异或门74LS86实现半加器逻辑功能的电路如图4.1所示。

2.全加器① 全加器的真值表见表4.2 。

② 全加器的逻辑式:i i i i C B A S ⊕⊕=()()ii i i i ii i i i 1i B A C B A B A C B A C ⋅⋅⋅⊕=+⊕=+③ 由门电路组成的全加器电路用上述两个半加器可组成全加器,其逻辑电路如图4.2所示。