飞思卡尔XS128_各模块整理资料

- 格式:pdf

- 大小:381.95 KB

- 文档页数:37

言归正传,开始讲PIT,讲PIT,我准备先简单讲讲寄存器,之前不讲主要是基本上买的到的书都是DG128的,里面关于IO口的寄存器和PWM的寄存器都是完全可以照搬的,而这一章的东西照搬是要出问题的。

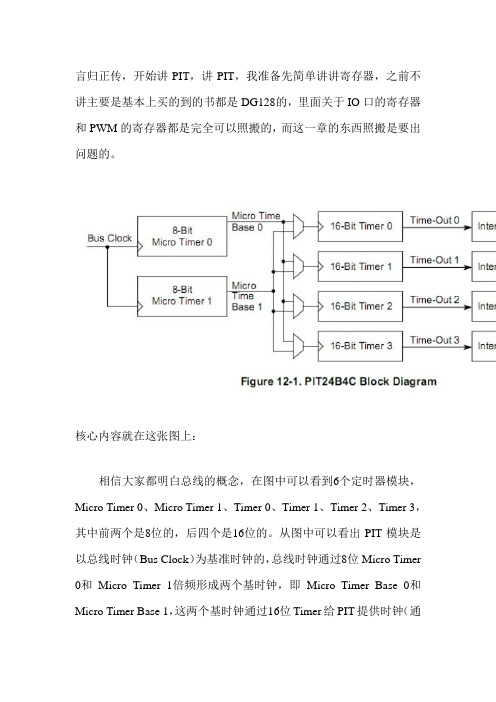

核心内容就在这张图上:相信大家都明白总线的概念,在图中可以看到6个定时器模块,Micro Timer 0、Micro Timer 1、Timer 0、Timer 1、Timer 2、Timer 3,其中前两个是8位的,后四个是16位的。

从图中可以看出PIT模块是以总线时钟(Bus Clock)为基准时钟的,总线时钟通过8位Micro Timer 0和Micro Timer 1倍频形成两个基时钟,即Micro Timer Base 0和Micro Timer Base 1,这两个基时钟通过16位Timer给PIT提供时钟(通过寄存器PITMUX设置)。

原理讲完了,其实相对于PIT模块是一个24位的定时器(51单片机最多也就16位),这个计数范围还是蛮大的。

下面是一些寄存器的解释,解释完还是看代码吧。

S12PIT24B4CV1是一个模数递减计数器。

首先给计数寄存器设定一个初值,每经过一个总线周期,计数器进行一次减一操作,当计数器自减溢出时,触发中断。

因为总线周期是已知的,即可以通过计数器自减实现定时。

在XS128PIT模块中,需要用到得是如下几个寄存器。

1)、PIT Contorl and force Lad Micro Timer Register(PITCFLMT)该寄存器用于PIT模块的使能设置和工作方式设置。

通常设置该寄存器中的PITE为即可,即PITCFLMT_PITE=1,使PIT使能。

2)、PIT Channel Enable Register(PITCE)该寄存器用于对PIT模块中的4个通道使能进行设置。

如果使用某个通道时,对对应位进行置一即可,即PITCE_PCEx=1,其中x代表通道序号,为0~3。

xs128-PWM设置pwm模块.用于舵机电机控制.1. 开启pwmpwme寄存器8位[ pwme7 pwme6 ..]pwme1 = 1 一号通道开启pwme2 = 0 二号关闭2.pwm极性选择初始波形1 or 0pwmpol寄存器8位[ ppol7 ppol6 ..]pwmpol1 = 1; 一号通道先高电平.3.pwm时钟选择pwmclk寄存器8位[ pclk7 pclk6 ..]0 1 4 5 可选A SA时钟2 3 6 7 可选B SB时钟pclk1 = 1 ;一通道选择SApclk1 = 0 ;一通道选择A4. A ,B时钟分频PWMPRCLK寄存器8位高[0 b2 b1 b0 0 a2 a1 a0] 低PCKB0~PCKB2 B分频PCKA0~PCKA2 A分频PCK*2 PCK*1 PCK*0 频率0 0 0 E0 0 1 E/20 1 0 E/40 1 1 E/81 0 0 E/161 0 1 E/321 1 0 E/641 1 1 E/1285.SA SB时钟分频PWMSCLA SA时钟分频8位PWMSCLB SB时钟分频8位分频公式SA = A/(2*PWMSCLA)SB = B/(3*PWMSCLB)6.输出选项左对齐or 居中对齐PWMCAE寄存器8位[ CAE7 CAE6 ..]CAEX = 1 居中对齐7.通道串联设置PWNCTL寄存器8 位[con67 con45 con23 con01 pswai pfrz 0 0]CON67 = 1 ;6 7 通道串联7通道控制有效8. PWNCNTx 计数寄存器PWMCNTx 8个PWMCNT0 PWMCNT1 ..9.PWMPERx 周期寄存器PWMPERx 8个PWMPER0 PWMPER1 ..左对齐PWMx周期= 时钟周期* PWMPERx居中对齐PWMx周期= 时钟周期* PWMPERx * 210.PWMDTYx 占空比寄存器PWMCTYx 8个PWMDTY0 PWMDTY1 ..ppol=0占空比=[(PWMPERx-PWMDTYx)/PWMPERx]*100%ppol=1占空比=(PWMDTYx/PWMPERx)*100%。

用了一年多飞思卡尔MC9S12XS128这款处理器,现在总结下各个功能模块的驱动.//锁相环时钟的初始化总线频率为40MHz(总线时钟为锁相环时钟的一半)//晶振为11.0592MHzvoid PLL_init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) { //锁相环时钟= 2*11.0592*(39+1)/(10+1)=80MHz 总线时钟为40MHzREFDV=0x0A;SYNR=0x67; //0110_0111 低6位的值为19,高两位的值为推荐值while(CRGFLG_LOCK != 1);CLKSEL_PLLSEL = 1; //选定锁相环时钟//FCLKDIV=0x0F; //Flash Clock Divide Factor 16M/16=1M}//周期中断定时器的初始化-// //周期中断通道1用于脉冲累加器的定时采样,定时周期为: 10ms= (199+1)*(1999+1)/(40M) (没有使用)//周期中断通道0用于控制激光管的轮流发射,定时周期为: 2000us= (399+1)*(199+1)/(40M)//2011/4/4 15:24 定时时间改为1msvoid PIT_init(void){PITCFLMT_PITE = 0; // 禁止使用PIT模块 PITCFLMT :PIT 控制强制加载微计数器寄存器。

PITCE_PCE0 = 1; // 使能定时器通道0//PITCE_PCE1 = 1; //使能定时器通道1PITMUX = 0; //通道0,和通道1均选择8位微计数器0//修改时间只需要改下面四行PITMTLD0 = 199; //向8位微计数器中加载的值PITLD0 = 199; //向16位计数器中加载的值//PITMTLD1 = 39; //向8位微计数器中加载的值 8位,最大值不要超过255//PITLD1 = 1999; //向16位计数器中加载的值PITINTE |= 0x01; //使能定时器通道0的中断PITCFLMT_PITE = 1;//使能PIT模块}//脉冲累加器的初始化, PT7口外接光电编码器//最新修改: 2011/3/25 16:53void PT7_PulAcc_Init(void){DDRT &= 0x77;//设置PT7,PT3口为输入(硬件上PT7,PT3通过跳线联到了一块)PERT |= 0x80; //使能通道7的上拉电阻PPST &= 0x7f; //电阻设为上拉电阻TCTL4 &= 0x3f; //禁止PT3的输入捕捉功能PACTL = 0x50; //启动脉冲累加计数器,上升沿触发,禁止触发中断和溢出中断,主定时器禁止}//通道1用于控制舵机1 PWM 高电平有效,//通道3用于控制电机1 PWM 低电平有效,这与前两代车高电平有效有区别!!!!!//通道7用于给上排激光管提供PWM信号 PWM高电平有效!!!!!//通道6用于给下排激光管提供PWM信号 PWM高电平有效!!!!!// 2011-03-17 7:56 增加了A端口的使用新增通道6//2011-6-9 23:03 //增加了通道4,5的联合使用,用于控制下排方向舵机 void PWM_init(void){PWME = 0x00;//PWM禁止PWMPRCLK = 0x03; // ClockA=40M/8=5M, Clock B = 40M/1=40M PWMSCLB = 10; // Clock SB= 40/2*10= 2MHz(供电机)PWMSCLA = 5; // SA = Clock A/2*5 = 5M/10 = 500K = SA 用于控制舵机PWMPOL = 0xe2; //1110_0010通道7,通道6与通道1、通道5先输出高电平然后输出低电平,POLx=1先输出高电平后输出低电平; PPOLx=0先输出低电平)PWMCAE = 0x00; // 左对齐输出(CAEx=0为左对齐,反之为中心对齐)//PWMCLK = 0010_1010 (0 1 4 5位控制SA_1;或A_0; 2 3 6 7位控制SB_1 或B_0)//为PWM通道1选择时钟 SA(500KHz),//为PWM通道5选择时钟 SA(500KHz),//为通道3选择时钟 SB(10MHz)//为通道7选择时钟B(40MHz)//为通道6选择时钟B(40MHz)PWMCLK = 0x2A; //0010_1010PWMCTL = 0x70; //0111_0000 CON45=1,把通道4,5联合使用。

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释//**************************************************************************// 武狂狼2014.5.1 整理// 新手入门的助手////***************************************************************************注释不详细/*********************************************************/函数名称:void ATD0_init(void)函数功能:ATD初始化入口参数:出口参数:/***********************************************************/void ATD0_init(void){ATD0DIEN=0x00; //使用模拟输入功能|=1;数字输入功能// ATD0CTL0=0x07; //Bit[3:0]WRAP[3:0] 反转通道选择位ATD0CTL1=0x40; // 12位精度,采样前不放电 Bit[7]ETRIGSEL(外部触发源选择位。

=0选择A/D通道AN[15:0] |=1选择 ERTIG3~0)和Bit[3:0]ETRIGCH[3:0]选择外部触发通道// Bit[6:5]SRES[1:0]A/D分辨率选择位。

Bit[4]SMP_DIS =0采样前不放电|=1采样前内部电容放电,这会增加2个A/D时钟周期的采样时间,有助于采样前进行开路检测ATD0CTL2=0x40; // 快速清零,禁止中断,禁止外部触发ATD0CTL3=0x90; // 右对齐,转换序列长度为2,非FIFOATD0CTL4=0x03; // 采样时间4个周期,PRS=31,F(ATDCLK)=F(BUS)/(2(PRS+1))// ATD0CTL5=0x30; //启动AD转换序列//:对每项数据采集时,用到哪个通道采样可在相应子函数内设置某一通道(见Sample_AD.c)while(!ATD0STAT2L_CCF0);/*********************************************************/函数名称:void PIT_init(void)函数功能:初始化PIT 设置精确定时时间(1s)入口参数:无出口参数:无说明:无/***********************************************************/void PIT_init(void){PITCFLMT=0x00; //禁止PIT模块Bit[7] PITE:PIT模块使能位,0禁用|1使能// Bit[6] PITSWAI:等待模式下PIT停止位,0等待模式下,PIT模块正常运行| 1等待模式下,PIT模块停止产生时钟信号,冻结PIT模块// Bit[5] PITFRZ: 冻结模式下PIT计数器冻结位。

飞思卡尔16位单片机9S12XS128使用收藏最近做一个关于飞思卡尔16位单片机9S12XS128MAA的项目,以前未做过单片机,故做此项目颇有些感触。

现记录下这个艰辛历程。

以前一直是做软件方面的工作,很少接触硬件,感觉搞硬件的人很高深,现在接触了点硬件发现,与其说使用java,C#等语言写程序是搭积木,不如说搞硬件芯片搭接的更像是在搭积木(因为芯片是实实在在拿在手里的东西,而代码不是滴。

还有搞芯片内部电路的不在此列,这个我暂时还不熟悉)。

目前我们在做的这个模块,就是使用现有的很多芯片,然后根据其引脚定义,搭接出我们需要的功能PCB板,然后为其写程序。

废话不多说,进入正题。

单片机简介:9S12XS128MAA单片机是16位的单片机80个引脚,CPU是CPU12X,内部RAM 8KB,EEPROM:2KB,FLASH:128KB,外部晶振16M,通过内部PLL可得40M总线时钟。

9S12XS128MAA单片机拥有:CAN:1个,SCI:2个,SPI:1个,TIM:8个,PIT:4个,A/D:8个,PWM:8个下面介绍下我们项目用到的几个模块给出初始化代码1、时钟模块初始化单片机利用外部16M晶振,通过锁相环电路产生40M的总线时钟(9S12XS128系列标准为40M),初始化代码如下:view plaincopy to clipboardprint?/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}}/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}}上面的代码是汇编写的,这个因为汇编代码量比较少,所以用它写了,具体含义注释已经给出,主函数中调用此函数即可完成时钟初始化,总线时钟为40M.2、SCI模块初始化单片机电路做好了当然少不了和PC之间的通信,通信通过单片机串口SCI链接到PC 端的COM口上去。

来源:电子设计吧整理:大学生电子设计联盟smile_keyang/index.php欢迎访问!!!手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0 时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

,他们提供了一个宽范围的时7、有4个时钟源可供选择(A、SA、B、SB)钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

S128学习笔记(一)GPIO 模块S128 IO操作主要有三个寄存器数据寄存器(PORTX)数据方向寄存器(DDRX) 上拉上拉电阻控制寄存器PUCR)一. GPIO概述通用I/O:GPIO(General Purpose I/O),是I/O的最基本形式,它是一组输入或输出引脚,有时也称为并行I/O(parallel I/O)。

作为普通输入引脚,MCU内部程序可以读取该引脚,知道该引脚是“1”(高电平)或“0”(低电平),即开关量输入。

作为普通输出引脚,MCU内部程序由该引脚输出“1”(高电平)或“0”(低电平),即开关量输出。

大多数通用I/O引脚可以通过编程来设定工作方式为输入或输出,称之为双向通用I/O。

2. I/O口的使用方法MC9S12DG128 MCU有10个普通I/O口,分别是A口、B口、E口、H口、J口、K口、M 口、P口、S口、T口。

这些引脚中的大部分具有双重功能,其中A、B、E、K口只用做GPIO 功能,这里仅讨论它们编程方法。

使用这些I/O口主要设置如下寄存器:1)数据方向寄存器(Data Direction Register x,DDRx)DDRx的第7~0位分别记为DDRx7~DDRx0,这些位分别控制着x口引脚PORTx7~PORTx0是输入还是输出,若DDRxn=0,则引脚PORTAxn为输入,若DDRxn=1,则引脚PORTxn为输出。

复位时DDRx为$00。

(注:x代表A、B、E、K口中的某一个,n表示某一位)2)数据寄存器(Port x I/O Register,PORTx)PORTx的第7~0位分别记为PORTx7~PORTx0。

若A口的某一引脚PORTxn被定义。

成输出,程序使x口I/O寄存器PORTx的相应位PORTxn=0,则引脚PORTxn输出“低电平”;程序使PORTxn=1,则引脚PORTxn输出“高电平”。

若x口的某一引脚PORTxn被定义成输入,程序通过读取x口I/O寄存器PORTx,获得输入情况,0表示输入为“低电平”,1表示输入为“高电平”。