拉电流(source current)与灌电流(sink current)

- 格式:pdf

- 大小:101.13 KB

- 文档页数:1

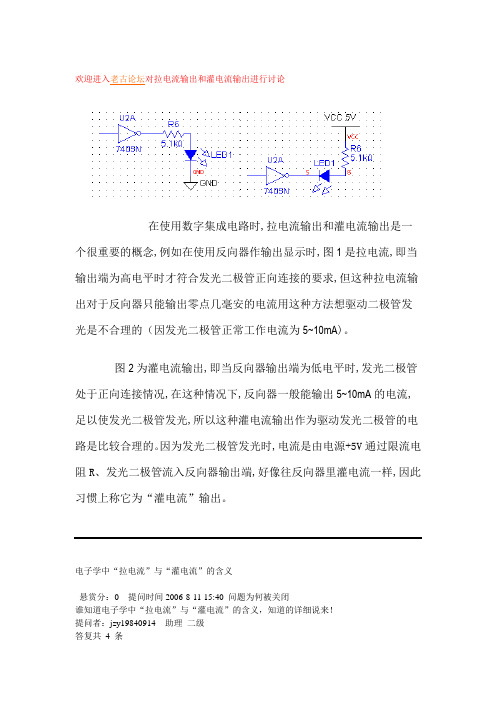

欢迎进入老古论坛对拉电流输出和灌电流输出进行讨论在使用数字集成电路时,拉电流输出和灌电流输出是一个很重要的概念,例如在使用反向器作输出显示时,图1是拉电流,即当输出端为高电平时才符合发光二极管正向连接的要求,但这种拉电流输出对于反向器只能输出零点几毫安的电流用这种方法想驱动二极管发光是不合理的(因发光二极管正常工作电流为5~10mA)。

图2为灌电流输出,即当反向器输出端为低电平时,发光二极管处于正向连接情况,在这种情况下,反向器一般能输出5~10mA的电流,足以使发光二极管发光,所以这种灌电流输出作为驱动发光二极管的电路是比较合理的。

因为发光二极管发光时,电流是由电源+5V通过限流电阻R、发光二极管流入反向器输出端,好像往反向器里灌电流一样,因此习惯上称它为“灌电流”输出。

电子学中“拉电流”与“灌电流”的含义悬赏分:0 - 提问时间2006-8-11 15:40 问题为何被关闭谁知道电子学中“拉电流”与“灌电流”的含义,知道的详细说来!提问者:jzy19840914 - 助理二级答复共4 条垃,既通过器件向电源索取。

灌,既通过器件向电源回输(流)。

回答者:老瓢虫- 高级魔法师七级8-11 16:35器件通过负载接电源称为灌;器件通过负载接地称为拉。

回答者:lnaslzt - 同进士出身七级8-11 18:59拉电流即元气件从它的负载输入电流;灌电流即该元气件向负载输出电流。

回答者:lncysun - 助理三级8-13 10:48数字电路中的0,1,是根据电位的高低来区分的。

在电位高时,下一级电路会从本级电路中拉出一部分电流,在电位低时,上一级电路会向本级电路中灌入一部分电流,这就是你所谓的:电子学中“拉电流”与“灌电流”的含义回答者:高级电灯泡- 见习魔法师二级8-13 21:17什么是灌电流,拉电流和扇出系数当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。

灌电流(sink current),对一个端口而言,如果电流方向是向其内部流动的则是“灌电流”,比如一个IO通过一个电阻和一个LED连接至VCC,当该IO输出为逻辑0时能不能点亮LED,去查该器件手册中sink current参数。

拉电流(sourcing current),对一个端口而言,如果电流方向是向其外部流动的则是“拉电流”,比如一个IO通过一个电阻和一个LED连至GND,当该IO输出为逻辑1时能不能点亮LED,去查该器件手册中sourcing current参数。

一般来说上拉或下拉电阻的作用是增大电流,加强电路的驱动能力。

也有时用来平衡电平,是的处理器可以得到更稳定的逻辑电平,减少因干扰造成的盲区误判断。

说一下基础概念

电源到元件间的叫上拉电阻,作用是平时使该脚为高电平

地到元件间的叫下拉电阻,作用是平时使该脚为低电平

上拉电阻和下拉电阻的范围由器件来定(我们一般用10K)

+Vcc---上拉电阻---|IO口元件|(该情况为上拉电阻方式)

|IO口元件|---下拉电阻---GND|(该情况为下拉电阻方式)

而对于51处理器的P0口必须接上拉电阻才可以作为IO口输出使用上拉和下拉的区别是一个为拉电流,一个为灌电流

一般来说灌电流比拉电流要大

也就是灌电流驱动能力强一些。

电路常识性概念(5)-上拉电阻、下拉电阻/ 拉电流、灌电流 / 扇出系数(一)上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

同時管脚悬空就比较容易接受外界的电磁干扰(MOS器件为高输入阻抗,极容易引入外界干扰)。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

(二)上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大:电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小:电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理。

(三)对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4.频率特性。

(一)上拉电阻的使用场合:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

同時管脚悬空就比较容易接受外界的电磁干扰(MOS器件为高输入阻抗,极容易引入外界干扰)。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

(二)上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大:电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小:电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理。

(三)对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4.频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

拉电流灌电流扇入扇出准双向双向定义很详细实用当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。

由三极管输出特性曲线也可以看出,灌电流越大,饱和压降越大,低电平越大。

逻辑门的低电平是有一定限制的,它有一个最大值UOLMA某。

在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOLMA某≤0.4~0.5V。

当逻辑门输出端是高电平时,逻辑门输出端的电流是从逻辑门中流出,这个电流称为拉电流。

拉电流越大,输出端的高电平就越低。

这是因为输出级三极管是有内阻的,内阻上的电压降会使输出电压下降。

拉电流越大,高电平越低。

逻辑门的高电平是有一定限制的,它有一个最小值UOHMIN。

在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOHMIN≥2.4V。

由于高电平输入电流很小,在微安级,一般可以不必考虑,低电平电流较大,在毫安级。

所以,往往低电平的灌电流不超标就不会有问题,用扇出系数来说明逻辑门来同类门的能力。

扇出系数NO是描述集成电路带负载能力的参数,它的定义式如下:NO=IOLMA某/IILMA某其中IOLMA某为最大允许灌电流,IILMA某是一个负载门灌入本级的电流。

No越大,说明门的负载能力越强。

一般产品规定要求No≥8。

对于标准TTL门,NO≥10;对于低功耗肖特基系列的TTL门,NO≥20扇入、扇出系数:扇入系数--门电路允许的输入端数目。

一般门电路的扇入系数Nr为1—5,最多不超过8。

若芯片输入端数多于实际要求的数目,可将芯片多余输入端接高电平(+5V)或接低电平(GND)。

扇出系数--一个门的输出端所驱动同类型门的个数,或称负载能力。

一般门电路的扇出系数Nc为8,驱动器的扇出系数Nc可达25。

Nc体现了门电路的负载能力。

对于输入电流的器件而言:灌入电流和吸收电流都是输入的,灌入电流是被动的,吸收电流是主动的。

如果外部电流通过芯片引脚向芯片内流入称为灌电流;反之如果内部电流通过很详细实用芯片引脚从芯片内‘流出’称为拉电流。

PLC与接近开关、光电开关的接线问题摘要:本文主要分析了数字量输入时PLC内部电路常见的几种形式,SINK- 拉电流输入,SOURCE- 灌电流输入,并结合传感器常见几种输出形式和经常遇到的NPN和PNP输出,以及单端与双端接口,给出了和不同的PLC电路形式连接时的接线方法。

关键词:PLC SINK- 拉电流输入NPN输出SOURCE- 灌电流输入PNP输出单端双端接口一:引言PLC的数字量输入接口并不复杂,我们都知道PLC为了提高抗干扰能力,输入接口都采用光电耦合器来隔离输入信号与内部处理电路的传输。

因此,输入端的信号只是驱动光电耦合器的内部LED导通,被光电耦合器的光电管接收,即可使外部输入信号可靠传输。

目前PLC数字量输入端口一般分单端共点与双端输入,各厂商的单端共点(Com)的接口有光电耦合器正极共点与负极共点之分,日系PLC通常采用正极共点,欧系PLC习惯采用负极共点;日系PLC供应欧洲市场也按欧洲习惯采用负极共点;为了能灵活使用又发展了单端共点(S/S)可选型,根据需要单端共点可以接负极也可以接正极。

由于这些区别,用户在选配外部传感器时接法上需要一定的区分与了解才能正确使用传感器与PLC为后期的编程工作和系统稳定奠定基础。

二:输入电路的形式1、输入类型的分类PLC的数字量输入端子,按电源分直流与交流,按输入接口分类由单端共点输入与双端输入,单端共点接电源正极为SINK(sink Current 拉电流),单端共点接电源负极为SRCE (source Current 灌电流)。

2、术语的解释SINK漏型SOURCE源型SINK漏型为电流从输入端流出,那么输入端与电源负极相连即可,说明接口内部的光电耦合器为单端共点为电源正极,可接NPN型传感器。

SOURCE源型为电流从输入端流进,那么输入端与电源正极相连即可,说明接口内部的光电耦合器为单端共点为电源负极,可接PNP型传感器。

国内对这两种方式的说法有各种表达:1)、根据TI的定义,sink Current 为拉电流,source Current为灌电流,2)、由按接口的单端共点的极性,共正极与共负极。

接近开关与PLC的接线方法摘要:本文主要分析了数字量输入时PLC内部电路常见的几种形式,SINK- 拉电流输入,SOURCE- 灌电流输入,并结合传感器常见几种输出形式和经常遇到的NPN和PNP输出,以及单端与双端接口,给出了和不同的PLC电路形式连接时的接线方法。

关键词: PLC SINK- 拉电流输入 NPN输出 SOURCE- 灌电流输入 PNP输出单端双端接口一:引言PLC的数字量输入接口并不复杂,我们都知道PLC为了提高抗干扰能力,输入接口都采用光电耦合器来隔离输入信号与内部处理电路的传输。

因此,输入端的信号只是驱动光电耦合器的内部LED导通,被光电耦合器的光电管接收,即可使外部输入信号可靠传输。

目前PLC数字量输入端口一般分单端共点与双端输入,各厂商的单端共点(Com)的接口有光电耦合器正极共点与负极共点之分,日系PLC通常采用正极共点,欧系PLC习惯采用负极共点;日系PLC供应欧洲市场也按欧洲习惯采用负极共点;为了能灵活使用又发展了单端共点(S/S)可选型,根据需要单端共点可以接负极也可以接正极。

由于这些区别,用户在选配外部传感器时接法上需要一定的区分与了解才能正确使用传感器与PLC为后期的编程工作和系统稳定奠定基础。

二:输入电路的形式1、输入类型的分类PLC的数字量输入端子,按电源分直流与交流,按输入接口分类由单端共点输入与双端输入,单端共点接电源正极为SINK(sink Current 拉电流),单端共点接电源负极为SRCE(source Current 灌电流)。

2、术语的解释SINK漏型SOURCE源型全球独家推出 全覆盖型省配线解决方案SINK漏型为电流从输入端流出,那么输入端与电源负极相连即可,说明接口内部的光电耦合器为单端共点为电源正极,可接NPN型传感器。

SOURCE源型为电流从输入端流进,那么输入端与电源正极相连即可,说明接口内部的光电耦合器为单端共点为电源负极,可接PNP型传感器。

当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。

由三极管输出特性曲线也可以看出,灌电流越大,饱和压降越大,低电平越大。

逻辑门的低电平是有一定限制的,它有一个最大值UOLMAX。

在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOLMAX ≤0.4~0.5V。

当逻辑门输出端是高电平时,逻辑门输出端的电流是从逻辑门中流出,这个电流称为拉电流。

拉电流越大,输出端的高电平就越低。

这是因为输出级三极管是有内阻的,内阻上的电压降会使输出电压下降。

拉电流越大,高电平越低。

逻辑门的高电平是有一定限制的,它有一个最小值UOHMIN。

在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOHMIN ≥2.4V。

由于高电平输入电流很小,在微安级,一般可以不必考虑,低电平电流较大,在毫安级。

所以,往往低电平的灌电流不超标就不会有问题,用扇出系数来说明逻辑门来同类门的能力。

扇出系数NO是描述集成电路带负载能力的参数,它的定义式如下:NO= IOLMAX / IILMAX其中IOLMAX为最大允许灌电流,IILMAX是一个负载门灌入本级的电流。

No越大,说明门的负载能力越强。

一般产品规定要求No≥8。

对于标准TTL门,NO≥10;对于低功耗肖特基系列的TTL门,NO≥20扇入、扇出系数:扇入系数--门电路允许的输入端数目。

一般门电路的扇入系数Nr为1—5,最多不超过8。

若芯片输入端数多于实际要求的数目,可将芯片多余输入端接高电平(+5V)或接低电平(GND)。

扇出系数--一个门的输出端所驱动同类型门的个数,或称负载能力。

一般门电路的扇出系数Nc为8,驱动器的扇出系数Nc可达25。

Nc体现了门电路的负载能力。

对于输入电流的器件而言:灌入电流和吸收电流都是输入的,灌入电流是被动的,吸收电流是主动的。

如果外部电流通过芯片引脚向芯片内‘流入’称为灌电流;反之如果内部电流通过芯片引脚从芯片内‘流出’称为拉电流。

© October 2008Altera Corporation Implementing LED Drivers in MAX and MAX II DevicesAN-286-2.3© October 2008Implementing LED Drivers in MAXand MAX II DevicesIntroductionDiscrete LED driver chips are common on many system boards. Altera ®MAX ®II,MAX 7000B, MAX 7000A, MAX 3000A, and MAX 7000S devices offer unique capabilities that allow you to integrate single or multiple LED driver chips into a single device. This application note explains how to implement LED drivers in MAX and MAX II devices.Commercial LED Driver ChipsMany LEDs, such as the seven-segment display, are common-anode LEDs. The LEDs anode connects to V CC and each cathode connects to an output pin of the current-sinking LED driver chip. The driver chip sinks the DC current required to drive the display, and the LED turns on when the driver chip's output pins drive low. Current-regulating circuits are implemented inside the LED driver chips.Current-sinking LED drivers are more common than current-sourcing drivers are. Table 1 lists some common LED driver chips manufactured by Texas Instruments, NationalSemiconductor, and Toshiba. The manufacturer data sheets provide additional information about LED driver chips.Table 1.Current-Sinking LED Driver ChipsPage2Implementing LED Drivers in MAX and MAX II DevicesImplementing LED Drivers in MAX and MAX II DevicesWhen using a MAX or MAX II device as an LED driver chip, place a current-limitingresistor between the cathode side of the LEDs diode and the MAX or MAX II deviceI/O. The LEDs anode is tied to V CC, and is turned on when the MAX or MAX IIdevice I/O drive low.The most important aspect of an LED driver chip is the amount of current it has tosink. Many LED applications call for a current sink specification of 5 to 15mA.Because MAX II, MAX7000B, MAX7000A, MAX3000A, and MAX7000S devices cansink up to 50mA per pin, these MAX and MAX II device families can directlyintegrate commercial current-sinking LED driver chips.Table2 shows the maximum sink current per pin for MAX and MAX II devices.Table2.Maximum Sink Current for MAX and MAX II DevicesNote to Table2:(1)25mA is the absolute maximum rating for the sink current per pin in the MAX II device. Device operation at the absolute maximum ratings forextended periods of time may have adverse affects on the device. For the absolute maximum ratings of the MAX II device family, refer to the DC and Switching Characteristics chapter of the MAX II Handbook .Although a single pin from a MAX7000B device can sink up to 50mA of DC current,each GNDIO group can concurrently sink up to 200mA of current due to the supportof advanced I/O standards.Table3 shows the maximum source current for a set of I/O pins between any twoVCCIO pads or maximum sink current between any two GNDIO pads (regardless ofthe I/O bank) in MAX and MAX II devices.Table3.Maximum Source Current for Each VCCIO Group and Maximum Sink Current for Each GNDIO Group in MAX and MAX II DevicesFor example, the EPM240 device has six GNDIO pads, which provide six I/O regionsthat can sink up to 130mΑ. If you need to sink 15mA for the outputs, you can haveeight outputs per region. With the six regions of I/O between GNDIO pads, there are48 possible outputs, each sinking 15mA.Implementing LED Drivers in MAX and MAX II Devices© October 2008Altera Corporationf For more information about GNDIO grouping, refer to the MAX II Device Pin-OutFiles, and the MAX 7000B Device Pin-Out Files. These files are on the Pin-Outs page ofthe Literature section of the Altera website ().Implementing LED Driver ChipsFigure1 shows an example of an application circuit with the Toshiba TB62701ANLED, its 16-bit constant current LED driver with shift registers and latch functions.The 16 outputs of the circuit sink current for two seven-segment displays. You canimplement the LED driver chip in the circuitry using only one MAX or MAX II device,provided the device has enough register and pin capabilities to replace thefunctionality of the entire LED driver chip.Figure1.Application Circuit Example Using the Toshiba TB62701AN LED Driver ChipFigure2 shows a block diagram of the Toshiba TB62701AN LED driver chip. TheAltera LED driver reference design has the same architecture as the TB62701AN. Itconsists of three main categories:■16-bit serial shift registers■16-bit latches■An array of AND gatesThe data from serial-in that determines which LED to be driven is shifted serially intothe 16-bit shift registers for every low-to-high transition on the clock signal. With ahigh-to-low transition on the latch signal, the 16-bit data, which stores the 16-bit shiftregisters, is latched into 16-bit latches to drive the LED when the enable signals drivelow.© October 2008Altera Corporation Implementing LED Drivers in MAX and MAX II DevicesFigure2.Block Diagram of the Toshiba TB62701AN LED Driver ChipThe Altera LED driver reference design only emulates the functioning of the ToshibaTB62701AN. To implement the external resistor (R-EXT) and the current-regulatingcircuit, place an individual current-limiting resistor between the cathode side of theLEDs diodes and the I/O pins of the MAX or MAX II device.Figure3 shows the implementation of the LED driver using a MAX or MAX II device. Figure3.Implementing the LED Driver Using a MAX or MAX II DeviceImplementing LED Drivers in MAX and MAX II Devices© October 2008Altera CorporationThe right hand side of Figure3 shows the connection between discrete LEDs and theI/O pins of a MAX or MAX II device, while the left hand side shows the connectionbetween a seven-segment LED and the MAX or MAX II device. The output pins of theMAX or MAX II device connected to the LEDs are driven low to turn on the LEDs.1To download the LED drivers reference design, refer to the design files listed with AN286:Implementing LED Drivers in MAX and MAX II Devices, on the Literaturesection of the Altera web site ().Design ImplementationYou can target the LED drivers reference design in MAX II (EPM240T100C3) orMAX3000A (EPM3064ATC44) devices using the Quartus®II software. The designutilization in MAX II and MAX3000A devices is shown in Table4 and Table5.Table4.EPM240 LED Drivers Design UtilizationTable5.EPM3064A LED Drivers Design UtilizationDesign VerificationYou can achieve design verification for the LED driver by using the Quartus IIsoftware. MAX II and MAX3000A design verification occurs in both functional andtiming simulations. Figure4 shows the timing simulation of the LED drivers.© October 2008Altera Corporation Implementing LED Drivers in MAX and MAX II DevicesPage 6AdvantagesImplementing LED Drivers in MAX and MAX II Devices © October 2008Altera CorporationAs shown in Figure 4, the LED driver is first configured so that the parallel_out drives an output value of 1010101010101010. In the final configuration, the parallel_out output value is 1111111100000000.AdvantagesThe major advantage of implementing LED drivers with MAX or MAX II devices is that MAX or MAX II devices can also integrate other user logic using theirprogrammable logic. If you have to implement user logic on the same board as the LED driver, additional devices are required if you use a commercial LED driver chip. However, if a MAX or MAX II device is used, additional chips would not be required, saving valuable board space and reducing the overall system cost.ConclusionAltera’s MAX and MAX II devices not only provide solutions to the communications and industrial fields, but also offer simple solutions to integrate commodity products such as LED drivers. MAX and MAX II devices can integrate LED drivers and provide user logic, which saves on board space and reduces overall system cost.Referenced DocumentThis application note references the following documents:■DC and Switching Characteristics chapter of the MAX II Handbook■MAX II Device Pin-Out Files on the Pin-Outs page of the Literature section of the Altera website ( )■MAX 7000B Device Pin-Out Files on the Pin-Outs page of the Literature section of the Altera website ( ).Figure 4.LED Driver Timing Simulation in the Quartus II SoftwareNotes to Figure 4:(1)The high-to-low transition of the latch signal latches the serially-shifted input to drive the LED.(2)The low signal enables output to drive the LED.101 Innovation Drive San Jose, CA 95134Revision HistoryRevision HistoryTable 6shows the revision history for this FrameMaker template.Table 6.Template Revision History。

吸电流、拉电流、灌电流2011-03-03 18:19:16| 分类:默认分类阅读84 评论0 字号:大中小订阅拉即泄,主动输出电流,从输出口输出电流;灌即充,被动输入电流,从输出端口流入;吸则是主动吸入电流,从输入端口流入。

吸电流和灌电流就是从芯片外电路通过引脚流入芯片内的电流;区别在于吸收电流是主动的,从芯片输入端流入的叫吸收电流。

灌入电流是被动的,从输出端流入的叫灌入电流;拉电流是数字电路输出高电平给负载提供的输出电流,灌电流时输出低电平是外部给数字电路的输入电流。

这些实际就是输入、输出电流能力。

拉电流输出对于反向器只能输出零点几毫安的电流,用这种方法想驱动二极管发光是不合理的(因发光二极管正常工作电流为5~10mA)。

上、下拉电阻一、定义1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理!2、上拉是对器件注入电流,下拉是输出电流3、弱强只是上拉电阻的阻值不同,没有什么严格区分4、对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

二、拉电阻作用1、一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

2、数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!3、一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻,也就是说,如果该端口正常时为高电平;C通过一个电阻和地连接在一起的时候,该电阻称为下拉电阻,使该端口平时为低电平,作用吗:比如:“当一个接有上拉电阻的端口设为输入状态时,他的常态就为高电平,用于检测低电平的输入”。

丹东奥拓电子有限公司 201505 ATE/QB 01.07-2015 共1页 第1页 技术交流

对一个互补输出的驱动器而言,从输出端向外电路流出的负载电流称为拉电流(SOURCE CURRENT );从外电路流入输出端的负载电流称为灌电流(SINK CURRENT );在没有负载的情况下,驱动器没有工作的时候本身消耗的静态电流称为QUIESCENT CURRENT ,一般越小越好。

也可以简单理解为,对与IC 的驱动管脚,从该脚流出的是source current (拉电流),流入的是sink current (灌电流);而quiscent current (静态电流)可以指单个驱动管脚的漏电流(由工艺决定)也可以指具有静态模式的IC 的IDD 电流(由功能决定)。

拉电流(source current)与灌电流(sink current)。