拉电流和灌电流详细介绍

- 格式:doc

- 大小:260.50 KB

- 文档页数:4

拉电流与灌电流1、概念拉电流和灌电流是衡量电路输出驱动能力(注意:拉、灌都是对输出端而言的,所以是驱动能力)的参数,这种说法一般用在数字电路中。

这里首先要说明,芯片手册中的拉、灌电流是一个参数值,是芯片在实际电路中允许输出端拉、灌电流的上限值(允许最大值)。

而下面要讲的这个概念是电路中的实际值。

由于数字电路的输出只有高、低(0,1)两种电平值,高电平输出时,一般是输出端对负载提供电流,其提供电流的数值叫“拉电流”;低电平输出时,一般是输出端要吸收负载的电流,其吸收电流的数值叫“灌(入)电流”。

对于输入电流的器件而言:灌入电流和吸收电流都是输入的,灌入电流是被动的,吸收电流是主动的。

如果外部电流通过芯片引脚向芯片内‘流入'称为灌电流(被灌入);反之如果内部电流通过芯片引脚从芯片内‘流出’称为拉电流(被拉出)2、为什么能够衡量输出驱动能力当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。

由三极管输出特性曲线也可以看出,灌电流越大,饱和压降越大,低电平越大。

然而,逻辑门的低电平是有一定限制的,它有一个最大值UOLMAX.在逻辑门工作时,不允许超过这个数值,TTL 逻辑门的规范规定UOLMAX ≤0.4~0.5V.所以,灌电流有一个上限.当逻辑门输出端是高电平时,逻辑门输出端的电流是从逻辑门中流出,这个电流称为拉电流。

拉电流越大,输出端的高电平就越低.这是因为输出级三极管是有内阻的,内阻上的电压降会使输出电压下降。

拉电流越大,输出端的高电平越低。

然而,逻辑门的高电平是有一定限制的,它有一个最小值UOHMIN。

在逻辑门工作时,不允许超过这个数值,TTL 逻辑门的规范规定UOHMIN ≥2。

4V.所以,拉电流也有一个上限。

可见,输出端的拉电流和灌电流都有一个上限,否则高电平输出时,拉电流会使输出电平低于UOHMIN;低电平输出时,灌电流会使输出电平高于UOLMAX。

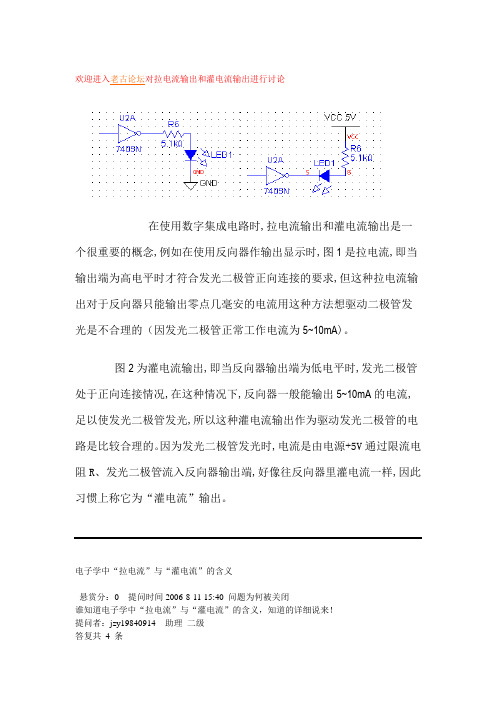

欢迎进入老古论坛对拉电流输出和灌电流输出进行讨论在使用数字集成电路时,拉电流输出和灌电流输出是一个很重要的概念,例如在使用反向器作输出显示时,图1是拉电流,即当输出端为高电平时才符合发光二极管正向连接的要求,但这种拉电流输出对于反向器只能输出零点几毫安的电流用这种方法想驱动二极管发光是不合理的(因发光二极管正常工作电流为5~10mA)。

图2为灌电流输出,即当反向器输出端为低电平时,发光二极管处于正向连接情况,在这种情况下,反向器一般能输出5~10mA的电流,足以使发光二极管发光,所以这种灌电流输出作为驱动发光二极管的电路是比较合理的。

因为发光二极管发光时,电流是由电源+5V通过限流电阻R、发光二极管流入反向器输出端,好像往反向器里灌电流一样,因此习惯上称它为“灌电流”输出。

电子学中“拉电流”与“灌电流”的含义悬赏分:0 - 提问时间2006-8-11 15:40 问题为何被关闭谁知道电子学中“拉电流”与“灌电流”的含义,知道的详细说来!提问者:jzy19840914 - 助理二级答复共4 条垃,既通过器件向电源索取。

灌,既通过器件向电源回输(流)。

回答者:老瓢虫- 高级魔法师七级8-11 16:35器件通过负载接电源称为灌;器件通过负载接地称为拉。

回答者:lnaslzt - 同进士出身七级8-11 18:59拉电流即元气件从它的负载输入电流;灌电流即该元气件向负载输出电流。

回答者:lncysun - 助理三级8-13 10:48数字电路中的0,1,是根据电位的高低来区分的。

在电位高时,下一级电路会从本级电路中拉出一部分电流,在电位低时,上一级电路会向本级电路中灌入一部分电流,这就是你所谓的:电子学中“拉电流”与“灌电流”的含义回答者:高级电灯泡- 见习魔法师二级8-13 21:17什么是灌电流,拉电流和扇出系数当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。

灌电流(sink current),对一个端口而言,如果电流方向是向其内部流动的则是“灌电流”,比如一个IO通过一个电阻和一个LED连接至VCC,当该IO输出为逻辑0时能不能点亮LED,去查该器件手册中sink current参数。

拉电流(sourcing current),对一个端口而言,如果电流方向是向其外部流动的则是“拉电流”,比如一个IO通过一个电阻和一个LED连至GND,当该IO输出为逻辑1时能不能点亮LED,去查该器件手册中sourcing current参数。

一般来说上拉或下拉电阻的作用是增大电流,加强电路的驱动能力。

也有时用来平衡电平,是的处理器可以得到更稳定的逻辑电平,减少因干扰造成的盲区误判断。

说一下基础概念

电源到元件间的叫上拉电阻,作用是平时使该脚为高电平

地到元件间的叫下拉电阻,作用是平时使该脚为低电平

上拉电阻和下拉电阻的范围由器件来定(我们一般用10K)

+Vcc---上拉电阻---|IO口元件|(该情况为上拉电阻方式)

|IO口元件|---下拉电阻---GND|(该情况为下拉电阻方式)

而对于51处理器的P0口必须接上拉电阻才可以作为IO口输出使用上拉和下拉的区别是一个为拉电流,一个为灌电流

一般来说灌电流比拉电流要大

也就是灌电流驱动能力强一些。

自动化专业面试最常见的16个问题1. 硅材料与锗材料的二极管导通后的压降各为多少?在温度升高后,二极管的正向压降,反向电流各会起什么变化?试说出二极管用途(举3个例子即可)2. 如何用万用表测试二极管的好坏?在选用整流二极管型号时,应满足主要参数有哪些?如何确定?3. 在发光二极管LED电路中,已知LED正向压降UF=1.4V,正向电流IF=10mA,电源电压5V,试问如何确定限流电阻。

4. 三极管运用于放大工作状态时,对NPN管型的,各极电位要求是:c极b极,b极e极,而对PNP管型,是c极b极,b极e 极。

5. 场效应管是型控制器件,是由极电压,控制极电流,对P 沟道及N沟道场效应管,漏极电压的极性如何?6. 集成运算放大器作为线性放大时,信号从同相端输入,试画出其电路图,并说明相应电阻如何取?7. 说出一个你熟悉的运算放大器的型号,指出输入失调电压的意义。

8. 试画出用运算放大器组成比例积分电路的电路图,说明各元件参数的选择。

9. 某电子线路需要一组5V,1A的直流稳压电源,请设计一个电源线路,并说明所需元件的大致选择。

10. 在一台电子设备中需要±15V两组电源,负载电流200mA,主用三端集成稳压器,1、画出电路图,2、试确定变压器二次侧电压有效值及容量。

11. TTL电路和CMOS电路是数字电子电路中最常用的,试说出TTL电路和CMOS电路主要特点及常用系列型号。

12. 什么是拉电流?什么是灌电流?TTL带动负载的能力约为多少?是拉电流还是灌电流?13. 在51系列单片机中,PO□,P1□、P2□、P3□引脚功能各是什么?14. 单片机有哪些中断源?中断处理的过程有哪些?中断服务程序的入口地址是由用户决定,对吗?15. 计算机与外设交换信息的主要方法有并行通信及串行通信两种,试说出两者的主要的优缺点。

16. 为什么采用I调节器及PI调节器能实现无静差?。

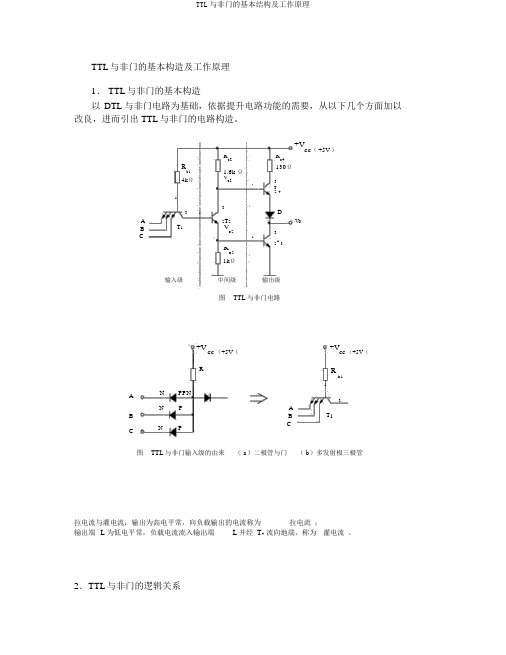

TTL 与非门的基本构造及工作原理 1. TTL 与非门的基本构造以 DTL 与非门电路为基础,依据提升电路功能的需要,从以下几个方面加以改良,进而引出 TTL 与非门的电路构造。

+VCC ( +5V )Rc2Rc4Rb11.6k Ω 130Ω4k ΩV c231T2 413 D31A T 12T 2V oB Ve23C12T3Re21k Ω输入级中间级输出级图 TTL 与非门电路+VCC (+5V (+V CC (+5V (RRb11ANPPN3A BNP T 1B CNPC图 TTL 与非门输入级的由来 ( a )二极管与门 ( b )多发射极三极管拉电流与灌电流:输出为高电平常,向负载输出的电流称为 拉电流 ; 输出端 L 为低电平常,负载电流流入输出端 L 并经 T 4 流向地端,称为 灌电流 。

2.TTL 与非门的逻辑关系因为该电路的输出高低电均分别为和 ,因此在下边的剖析中假定输入高低电平也分别为和。

( 1)输入全为高电平常。

T 2 、T 3 导通, V B1=× 3=(V ),进而使 T 1 的发射结因反偏而截止。

此时 T 1 的发射结反偏,而集电结正偏,称为倒置放大工作状态。

因为 T 3 饱和导通,输出电压为: V O =V CES3≈。

这时 V E2=V B3=,而 V CE2=,故有 V C2=V E2+ V CE2=1V 。

1V 的电压作用于 T 4 的基极,若要 T 4 和二极管 D 导通, T 4 的基极要,现在 1V<,因此使 T 4 和二极管 D 都截止。

可见实现了与非门的逻辑功能之一:输入全为高电平常,输出为低电平。

+V CC)(+5VR c2R c4Rb11.6k Ω130Ω34k Ω1V1截止T242.1V11.4V3D 截止312T 2 饱和A T 1V oB 0.7V30.3VC倒置状态12T 33.6VRe2饱和1K图 输入全为高电平常的工作状况 (2)输入有低电平常。

看来很多网友都搞不清灌电流和拉电流的概念,下面就此解释一下,希望看过本文后不再就此困扰。

一个重要的前提:灌电流和拉电流是针对端口而言的。

名词解释——灌:注入、填充,由外向内、由虚而实。

渴了,来一大杯鲜榨橙汁,一饮而尽,饱了,这叫“灌”。

灌电流(sink current),对一个端口而言,如果电流方向是向其内部流动的则是“灌电流”,比如一个IO通过一个电阻和一个LED连接至VCC,当该IO输出为逻辑0时能不能点亮LED,去查该器件手册中sink current参数。

名词解释——拉:流出、排空,由内向外,由实而虚。

一大杯鲜橙汁喝了,过会儿,憋的慌,赶紧找卫生间,一阵“大雨”,舒坦了,这叫“拉”。

拉电流(sourcing current),对一个端口而言,如果电流方向是向其外部流动的则是“拉电流”,比如一个IO通过一个电阻和一个LED 连至GND,当该IO输出为逻辑1时能不能点亮LED,去查该器件手册中sourcing current参数。

/viewthread.php?tid=219138&highlight=%2Byez hubenyue单片机输出低电平时,将允许外部器件,向单片机引脚内灌入电流,这个电流,称为“灌电流”,外部电路称为“灌电流负载”(sink current)单片机输出高电平时,则允许外部器件,从单片机的引脚,拉出电流,这个电流,称为“拉电流”,外部电路称为“拉电流负载“(source current)这些电流一般是多少?最大限度是多少?这就是常见的单片机输出驱动能力的问题。

分析一下TTL 的输入特性,就可以发现,51 单片机基本上就没有什么驱动能力。

它的引脚,甚至不能带动当时的LED 进行正常发光。

记得是在AT89C51 单片机流行起来之后,做而论道才发现:单片机引脚的能力大为增强,可以直接带动LED 发光了。

看看下图,图中的D1、D2 就可以不经其它驱动器件,直接由单片机的引脚控制发光显示。

什么时候需要用上拉电阻什么时候需要用下拉?一般要用多大的阻值呀?--------------------用上拉还是用下拉,根据你平时需要的电平。

至于阻值大小,如果是一般IO口,10k左右,不要小于1k。

但是如果是特殊用途的管腿,则有特殊要求。

比如I2C接口的SCL和SDA线,对上拉电阻的最大最小值都有要求,要结合实际情况计算。

--------------------通常在数字电路中,上拉是为了提高驱动能力。

例如:集电极开路的输出电路。

就必须加上拉电阻。

否则无法驱动下一级的设备。

或者,上拉下拉同时使用,例如,在数据和地址总线上。

是为了在没有输出的时候将电平钳制在一个电位。

不用的空脚要下拉,防止拴锁。

--------------------1。

信号需要外部的电源来提供高低电平时,需要加上拉或下拉电阻;2。

虽然系统能提供相应的电平,但是在不工作的状态下,信号的状态如果需要为高或低时,需要加上拉或下拉;3。

IC的输出为Open-Drain时,需要外加上拉电阻。

上拉或下拉的电阻大小取决于信号的驱动能力及信号的需求。

常用的有10K, 100K, 47K等。

但有些上拉电阻或下拉电阻的大小需要靠实验得到。

--------------------电路中的上拉和下拉电阻的连接是要通过计算而得到了,根据有三:1。

驱动器件输入电流的大小,需要在使用上拉时考虑。

解决的是高电平的匹配。

2。

电路速度的大小。

如果传送的数字信息速度较高,就要注意验证线路的延迟有没有走出信息的转折频率。

3。

与负责端的输入输出电流能力有关,需要验证能否承受。

--------------------上拉电阻和下拉电阻之所以需要,是为了给不匹配电流接口提供额外的电流通路,具体讲,驱动方输出电流小于负载方的吸入电流时加上拉电阻,以提供额外的电流供给;驱动方吸入电流小于负载方的灌出电流时加下拉电阻,以提供额外的电流泄放回路;上拉电阻和下拉电阻带来的附加效应是在接口无驱动时有一个固定电平(该特点常常被用固定口线初始及空闲时的状态)。

当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。

由三极管输出特性曲线也可以看出,灌电流越大,饱和压降越大,低电平越大。

逻辑门的低电平是有一定限制的,它有一个最大值UOLMAX。

在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOLMAX ≤0.4~0.5V。

当逻辑门输出端是高电平时,逻辑门输出端的电流是从逻辑门中流出,这个电流称为拉电流。

拉电流越大,输出端的高电平就越低。

这是因为输出级三极管是有内阻的,内阻上的电压降会使输出电压下降。

拉电流越大,高电平越低。

逻辑门的高电平是有一定限制的,它有一个最小值UOHMIN。

在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOHMIN ≥2.4V。

由于高电平输入电流很小,在微安级,一般可以不必考虑,低电平电流较大,在毫安级。

所以,往往低电平的灌电流不超标就不会有问题,用扇出系数来说明逻辑门来同类门的能力。

扇出系数NO是描述集成电路带负载能力的参数,它的定义式如下:NO= IOLMAX / IILMAX其中IOLMAX为最大允许灌电流,IILMAX是一个负载门灌入本级的电流。

No越大,说明门的负载能力越强。

一般产品规定要求No≥8。

对于标准TTL门,NO≥10;对于低功耗肖特基系列的TTL门,NO≥20扇入、扇出系数:扇入系数--门电路允许的输入端数目。

一般门电路的扇入系数Nr为1—5,最多不超过8。

若芯片输入端数多于实际要求的数目,可将芯片多余输入端接高电平(+5V)或接低电平(GND)。

扇出系数--一个门的输出端所驱动同类型门的个数,或称负载能力。

一般门电路的扇出系数Nc为8,驱动器的扇出系数Nc可达25。

Nc体现了门电路的负载能力。

对于输入电流的器件而言:灌入电流和吸收电流都是输入的,灌入电流是被动的,吸收电流是主动的。

如果外部电流通过芯片引脚向芯片内‘流入’称为灌电流;反之如果内部电流通过芯片引脚从芯片内‘流出’称为拉电流。

C8051F学习笔记:单片机的驱动能力学习51单片机的时候我们就知道51单片机的I/O口的特点:P0口没有弱上拉,所以做地址线时不用上拉,但输出“1”时就要加上拉电阻,不然输出电平到不了高电平,P1~P3则不存在这个问题,每个输出管脚都有弱上拉电阻(也就是电阻很大的上拉电阻),造成的结果是输出高电平电流很小,为uA量级,驱动不了LED、数码管之类的,所以要么在外加一个NPN的三极管增强驱动,要么LED、数码管用共阳极接法(也就是LED正接VCC,负接MCU的I/O;数码管用共阳数码管,COM口接VCC)。

虽然道理懂得,但很多时候脑子太死了,MCU接其他器件的时候,就要MCU的I/O输出驱动电流这事给忘了。

下面是一个教训:三个不同类型MCU 控制继电器的电路。

图1 MCU采用STC89C51,增加一个PNP,增强了驱动能力,能控制继电器TQ-RELAY的闭合图2 MCU用的是C8051F120,I/O端口高低电平能控制光耦继电器AQW610的闭合图3 MCU用的是ADI公司的单片机ADuC842,这种解法,MCU的I/O控制不了AQW610的闭合图2和图3基本是相同的电路,只不过是MCU不一样,为什么一个能控制AQW610,一个不行呢?让我们先来看看AQW610的DataSheet.AQW610的电气特性AQW610光耦继电器里的二极管工作电流常闭端为3.0mA,常开端为1.3mA。

再来看看单片机ADuC842(ADI公司兼容的51单片机)ADuC842的电气特性I SINK为灌电流,是指低电平输出时,能够吸收的电流;I SOUCE为拉电流,指高电平输出时,能够输出的电流;在这里虽然没有明确给出拉电流灌电流的最大值,只是把这两个作为输出高电流和低电平的测试条件,但可以认为这个测试条件也就是这款MCU能输出的最大电流了。

ADuC842高电平的驱动电流只能到80uA,P0~02、ALE低电平的驱动电流为1.6mA,P3低电平的驱动电流能达到3mA。