集成电路版图设计

- 格式:doc

- 大小:908.00 KB

- 文档页数:15

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

集成电路设计综合实验报告班级:微电子学1201班姓名:学号:日期:2016年元月13日一.实验目的1、培养从版图提取电路的能力2、学习版图设计的方法和技巧3、复习和巩固基本的数字单元电路设计4、学习并掌握集成电路设计流程二.实验内容1. 反向提取给定电路模块(如下图所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

2. 设计一个CMOS结构的二选一选择器。

(1)根据二选一选择器功能,分析其逻辑关系。

(2)根据其逻辑关系,构建CMOS结构的电路图。

(3)利用EDA工具画出其相应版图。

(4)利用几何设计规则文件进行在线DRC验证并修改版图。

三.实验原理1. 反向提取给定电路模块方法一:直接将版图整体提取(如下图)。

其缺点:过程繁杂,所提取的电路不够直观,不易很快分析出其电路原理及实现功能。

直接提取的整体电路结构图方法二:将版图作模块化提取,所提取的各个模块再生成symbol,最后将symbol按版图连接方式组合成完整电路结构(如下图)。

其优点:使电路结构更简洁直观、结构严谨、层次清晰,更易于分析其原理及所实现的功能。

CMOS反相器模块CMOS反相器的symbolCMOS传输门模块 CMOS传输门的symbolCMOS三态门模块 CMOS三态门的symbolCMOS与非门模块 CMOS与非门的symbol各模块symbol按版图连接方式组合而成的整体电路经分析可知,其为一个带使能端的D锁存器,逻辑功能如下:①当A=1,CP=0时,Q=D,Q—=D—;②当A=1,CP=1时,Q、Q—保持;③当A=0,Q=0,Q—=1。

2.CMOS结构的二选一选择器二选一选择器(mux2)的电路如图所示,它的逻辑功能是:①当sel=1时,选择输入A通过,Y=A;②当sel=0时,选择输入B通过,Y=B。

二选一选择器(mux2)由三个与非门(nand)和一个反相器(inv)构成(利用实验1 的与非门和反相器symbol即可)。

集成电路版图设计岗位职责职位要求(实用版)编制人:______审核人:______审批人:______编制单位:______编制时间:__年__月__日序言下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!并且,本店铺为大家提供各种类型的实用资料,如教学心得体会、工作心得体会、学生心得体会、综合心得体会、党员心得体会、培训心得体会、军警心得体会、观后感、作文大全、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor.I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!And, this store provides various types of practical materials for everyone, such as teaching experience, work experience, student experience, comprehensive experience, party member experience, training experience, military and police experience, observation and feedback, essay collection, other materials, etc. If you want to learn about different data formats and writing methods, please pay attention!集成电路版图设计岗位职责职位要求第1篇集成电路版图设计岗位职责职位要求职责描述:岗位职责:1、熟练掌握模拟集成电路或数字集成电路的设计概念和流程,独立或合作完成线路设计。

《集成电路版图设计》课内实验学院:信息学院专业班级:学号:学生姓名:指导教师:模拟集成电路版图设计集成电路版图是电路系统与集成电路工艺之间的中间环节,是一个不可少的重要环节。

通过集成电路的版图设计,可以将立体的电路系统变为一个二维的平面图形,再经过工艺加工还原于基于硅材料的立体结构。

因此,版图设计是一个上承的电路系统,下接集成电路芯片制造的中间桥梁,其重要性可见一斑。

但是,集成电路版图设计是一个令设计者感到困惑的一个环节,我们常常感到版图设计似乎没有什么规矩,设计的经验性往往掩盖了设计的科学性,即使是许多多年版设计经验的人有时候也说不清楚为何要这样或者那样设计。

在此,集成电路版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。

但它更需要设计者的创造性,空间想象力和耐性,需要设计者长期工作的经验和知识的积累,需要设计者对日异月新的集成电路发展密切关注和探索。

一个优秀的版图设计者对于开发超性能的集成电路是极其关键的。

在版图的设计和学习中,我们一直会面临匹配技术降低寄生参数技术熟悉电路作用(功能,频率)电流密度的计算(大电流和小电流的电流路径以及电流流向)等这些基本,它们也是最重要的问题。

版图的设计,从半导体制造工艺,到最后的后模拟过程都是非常关键的,里面所涉及的规则有1500——2000条,一些基本问题的解决方法和设计的调理化都将在下面提及。

模拟集成电路版图设计流程:阅读研究报告理解电路原理图了解电路的作用熟悉电流路径晶大小知道匹配器件明白电路中寄生,匹配,噪声的产生及解决方案对版图模块进行平面布局对整个版图进行平面布局熟练运用cadence软件进行版图绘制Esd的保护设计进行drc与lvs检查整理整个过程中的信息时刻做记录注意在设计过程中的交流集成电路制造工艺双极工艺:Cmos(p阱)工艺:版图设计经验总结:1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2 Cell名称不能以数字开头.否则无法做DRACULA检查.3 布局前考虑好出PIN的方向和位置4 布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

北京工业大学集成电路板图设计报告姓名:张靖维学号:12023224 2015年6 月1日目录目录 (1)1 绪论 (2)1.1 介绍 (2)1.1.1 集成电路的发展现状 (2)1.1.2 集成电路设计流程及数字集成电路设计流程 (2)1.1.3 CAD发展现状 (3)2 电路设计 (4)2.1 运算放大器电路 (4)2.1.1 工作原理 (4)2.1.2 电路设计 (4)2.2 D触发器电路 (12)2.2.1 反相器 (12)2.2.2 传输门 (12)2.2.3 与非门 (13)2.2.4 D触发器 (14)3 版图设计 (15)3.1 运算放大器 (15)3.1.1 运算放大器版图设计 (15)3.2 D触发器 (16)3.2.1 反相器 (16)3.2.2 传输门 (17)3.2.3 与非门 (17)3.2.4 D触发器 (18)4 总结与体会 (19)1 绪论随着晶体管的出现,集成电路随之产生,并极大地降低了电路的尺寸和成本。

而由于追求集成度的提高,渐渐设计者不得不利用CAD工具设计集成电路的版图,这样大大提高了工作效率。

在此单元中,我将介绍集成电路及CAD发展现状,本次课设所用EDA工具的简介以及集成电路设计流程等相关内容。

1.1 介绍1.1.1集成电路的发展现状2014年,在国家一系列政策密集出台的环境下,在国内市场强劲需求的推动下,我国集成电路产业整体保持平稳较快增长,开始迎来发展的加速期。

随着产业投入加大、技术突破与规模积累,在可以预见的未来,集成电路产业将成为支撑自主可控信息产业的核心力量,成为推动两化深度融合的重要基础。

、1.1.2集成电路设计流程及数字集成电路设计流程集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。

芯片硬件设计包括:功能设计阶段,设计描述和行为级验证,逻辑综合,门级验证(Gate-Level Netlist Verification),布局和布线。

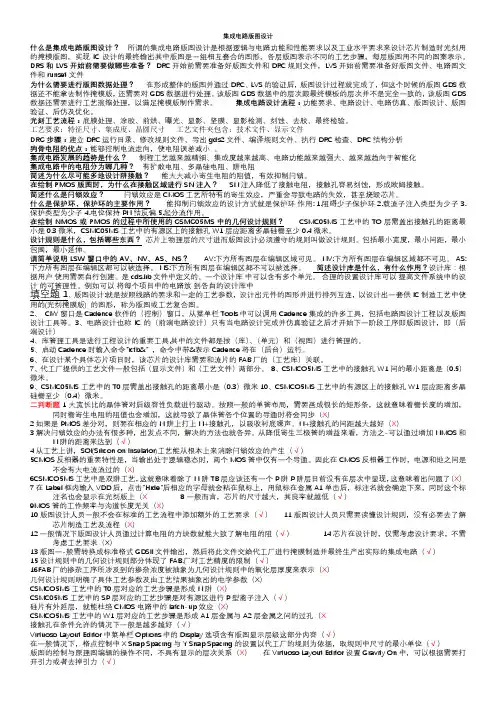

集成电路版图设计什么是集成电路版图设计?所谓的集成电路版图设计是根据逻辑与电路功能和性能要求以及工业水平要求来设计芯片制造时光刻用的掩模版图,实现IC设计的最终输出其中版图是一组相互套合的图形,各层版图表示不同的工艺步骤,每层版图用不同的图案表示。

DRS和LVS开始前需要做哪些准备?DRC开始前需要准备好版图文件和DRC规则文件,LVS开始前需要准备好版图文件、电路图文件和runset文件为什么需要进行版图数据处理?在形成整体的版图并通过DRC、LVS的验证后,版图设计过程就完成了,但这个时候的版图GDS数据还不能拿去制作掩模版,还需要对GDS数据进行处理。

该版图GDS数据中的层次跟最终模板的层次并不是完全一致的,该版图GDS 数据还需要进行工艺涨缩处理,以满足掩模版制作需求。

集成电路设计流程:功能要求、电路设计、电路仿真、版图设计、版图验证、后仿及优化。

光刻工艺流程:底膜处理、涂胶、前烘、曝光、显影、坚膜、显影检测、刻蚀、去胶、最终检验。

工艺要求:特征尺寸、集成度、晶圆尺寸工艺文件夹包含:技术文件、显示文件DRC步骤:建立DRC运行目录、修改规则文件、导出gds2文件、编译规则文件、执行DRC检查、DRC结构分析狗骨电阻的优点:能够控制电流走向,使电阻误差减小。

集成电路发展的趋势是什么?制程工艺越来越精细、集成度越来越高、电路功能越来越强大、越来越趋向于智能化集成电路中的电阻分为哪几种?有扩散电阻、多晶硅电阻、阱电阻简述为什么尽可能多地设计阱接触?能大大减小寄生电阻的阻值,有效抑制闩锁。

在绘制PMOS版图时,为什么在接触区域进行SN注入?SN注入降低了接触电阻,接触孔容易刻蚀,形成欧姆接触。

简述什么是闩锁效应?闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。

什么是保护环,保护环的主要作用?能抑制闩锁效应的设计方式就是保护环作用: 1.阻碍少子保护环 2.载流子注入类型为少子 3.保护类型为少子 4.电位保持PN结反偏 5.起分流作用。

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。

集成电路版图设计

集成电路版图设计是指将电子元器件(如晶体管、电阻、电容等)根据电路图的要求进行布局和连线的过程,实现电路功能并将其制作成一张版图以供电路的制造和生产。

集成电路版图设计主要包括以下几个步骤:

1. 电路分析:根据电路的功能及要求,进行电路分析,确定电路的基本结构和模块。

2. 元件选择:根据电路的功能和性能要求,选择合适的元件进行布局。

不同的元件具有不同的特性,如低噪声、快速开关、高频率等,需根据实际要求进行选择。

3. 布局设计:根据电路的结构和模块,将元件进行合理的布局。

布局的目的是使得电路平衡,减少干扰和噪声,并提高电路的稳定性和可靠性。

4. 连线设计:根据电路的功能要求,将各个元件进行连线,形成完整的电路。

连线的设计需要合理安排电路信号的传输路径,避免信号干扰和交叉干扰。

5. 优化设计:对布局和连线进行优化,以提高电路的性能。

例如,优化连线的长度和宽度,减少信号延迟和功耗。

6. 输出版图:将优化后的电路设计转化成计算机可识别的格式,并输出成版图文件。

版图文件可以用于电路的制造和生产。

集成电路版图设计的目的是在满足电路功能要求的前提下,使电路布局和连线达到最佳性能。

对于大规模集成电路(VLSI)设计,还需要考虑功耗、热量和信号完整性等因素,以实现高集成度和高性能的电路设计。

随着技术的不断发展,集成电路版图设计也在不断演进,从传统的手工设计发展到计算机辅助设计(CAD)和自动化设计(EDA),大大提高了设计效率和准确性。

《集成电路版图设计》

学院:_____________ 专业班级:_____________ 学号:_____________ 学生姓名:_____________ 指导教师:_____________

摘要

什么是集成电路?把组成电路的元件、器件以及相互间的连线放在单个芯片上,整个电路就在这个芯片上,把这个芯片放到管壳中进行封装,电路与外部的连接靠引脚完成。

什么是集成电路设计?根据电路功能和性能的要求,在正确选择系统配置、电路形式、器件结构、工艺方案和设计规则的情况下,尽量减小芯片面积,降低设计成本,缩短设计周期,以保证全局优化,设计出满足要求的集成电路。

《集成电路版图设计》基于Cadence软件的集成电路版图设计原理、编辑和验证的方法。

本次实验是基于Cadence版图设计软件平台,采用L50C7工艺库,设计一个运算放大器,并且,为了防止电路中各元件间产生闩锁效应,在实际生产流片中每个元件都应该添加保护环,以防止各元件间电流之间产生各种影响。

并且增加电路的稳定性和可靠性。

电路的验证采用的是Calibre验证工具,对电路版图进行了DRC验证和LVS验证。

关键词:Calibre,运算放大器

目录

一、电路设计流程 (1)

二、版图的制作流程 (2)

三、二级运算放大器的原理图 (3)

四、器件尺寸的计算 (4)

五、二级运算放大器原理图 (5)

六、二级运算放大器版图 (9)

心得体会 (11)

参考文献 (12)

一、电路设计流程

二、版图的制作流程

由于设计目标已经电路的构造课本已经讲述的十分详细。

所以我讲接着阐述版图的制作过程。

首先将电路图转为相应的版图, 意思就是把相对 应的器件进行布局布线。

因制造工艺精度有限,所以版图必须满足一定的规则要求。

按照设计规则布局布线后,接着就要对它进行检查。

由于版图是人工布局布线,因此 或多或少的存在一些错误。

这时就需要软件来进行“设计规则检查”(DRC )。

软件所依 据的是DRC 文件,它与画版图时使用的规则是一致的,只不过规则文件是给版图设计 者参考使用的,而DRC 文件是由软件编写的。

当版图没有了DRC 错误,完全符合设计规则之后,再依靠LVS 文件,将其与电路原理 图进行比较。

若有不同之处,LVS 将进行报错,经过修改之后还要重复DRC 、LVS 过程。

若两者相同,说版图与原理图一致。

到这一步就完成了版图的制作了。

完成版图之后, 还可以利用工具提取版图中的寄生参数,对包含这些寄生参数的电路再次进行仿真, 从而更准确确定电路的性能。

最后把图形格式的版图文件转换为通用二进制文件(GDS 文件),提交给生产厂制造。

三、二级运算放大器的原理图

我们要设计的是以上这个原理图所示的二级运算放大器。

其中二级运算放大器每个管子的参数如下表:

运算放大器框图:

输入中间输出

偏

置

二级运放结构原理:

输入级:输入电阻高,能减小零点漂移和抑制干扰信号,都采用带恒流源的差分放大器。

中间级:要求电压放大倍数高。

常采用带恒流源的共发射极放大电路构成。

输出级:与负载相接,要求输出电阻低,带负载能力强,一般由互补对称电路或射极输出器构成。

偏置电路: 由镜像恒流源等电路组成

工作原理图:

四、器件尺寸的计算

五、二级运算放大器原理图

1.打开虚拟机,键入代码打开cadence软件。

2.选择tool-library manager-来先建立一个库。

3.键入要设置的名字,按ok。

4. view,建立子元器件库,Cell Name键入名字czc_yuanlitu。

并且在View Name选择schematic (一般默认为这个)。

Tool选择Composer Schematic(一般也是默认的)。

最后点ok。

5.下边的是对各个cmos管的参数及位置、连线等进行编辑。

万变不离其宗,下边只介绍其中一个步骤,其他照葫芦画瓢就可以了。

在菜单栏点击add--instance,此时弹出对话框。

在此对话框选择browse。

选择工艺库L50C7--pmos_P--symbol.

选择nmos的话就在同一个工艺库中选择nmos_N--symbol.

选择电容:L50C7--cap_CI--symbol.

选择电阻:L50C7--res_M1--symbol.

6.当所有元器件都按以上步骤摆好了,然后就需要连线,按照原理图连线就可以了。

操作是:add--wire(narrow),此时弹出对话框:直接选择hide就可以连线了。

原理图完成后的效果:

7.连线完成后,还需要更改各个元器件的参数。

步骤如下:

选中要编辑的器件--点击左边的property,弹出对话框,只需要按图下表示更改四个指标就可。

六、二级运算放大器版图

最终结果图:

7.DRC验证及其操作

菜单栏选择Calibre--run DRC,然后选rules,在第一个框上选择路径,如图所示路径。

然后在左边选择inputs,files栏文件名正确就可以直接按左边菜单栏的”Run DRC”结果如图示,显示出来的错误按所示位置进行修改,修改到没有出现错误为止。

心得体会:

这次版图实验中我做了与非门。

二级运放和基准电流源的设计。

在我做集成电路版图设计过程的一开始分不清楚集成器件的工艺层次结构。

因此导致一开始画得很困难。

后来经过慢慢的练习,使我慢慢的熟悉了器件的工艺层次结构。

在设计版图的过程中。

对于工艺部分的尺寸调节这个环节是个相当繁琐的工作,不过在后来的摸索中我使我熟悉了调节的规则。

方便了我在后来的版图设计与调试。

在画版图之前。

首先我们要画好原理图,然后仿真。

这有助于检验电路是否设

计正确和有助于在版图设计中如何连线。

在画版图时。

我们要注意的地方非常多。

例如管子的匹配,给器件画保护环,

布局布线等等。

由于一开始不熟悉。

所以很多地方画得不好。

后来慢慢的在老师和同学的帮助下逐渐改进,逐步完善版图。

因为每个工艺库的工艺都不一样。

所以在画版图之前应该了解工艺的尺寸。

这样可以更好帮助我们画版图,以减少错误。

我认为学好半导体制造对画版图时非常有帮助的,因为它可以使你更好的理解怎么样去画,可以很好的帮助你去解决错误。

本次实验中我的收获还是比较大的,初始设计出版图的时候错误非常多,违反

设计规则的也有很多内容,修改的过程也是头痛不已,一开始很多地方不懂,但是在老师和同学们的帮助下,使我慢慢的了解设计规则和解决问题。

当所有问题解决之后,心里有一种成就感。

因为觉得自己很多地方都画得不好,后来我就通过不断的练习以提高和巩固老师说的知识。

版图设计的要点在于,在设计版图之前一定要对电路的原理进行分析,同时也要根据电流的流向和器件的对称等因素综合考虑器件的布局。

可以使用交叉匹配式的的电路,满足电路的设计业更加的美观。

通过本次实践,我对版图设计的整个流程有了深刻的认识。

在这次版图实验中,不仅让我学到了画版图的技巧。

还让我学会了做事要有耐心和细心,不能急于求成。

最后感谢老师的指导和同学们的帮助。

参考文献:

1、王自强.CMOS集成放大器设计.国防工业出版社.2007.269~310

2、Alan Hastings.王志功译.模拟电路版图艺术(第二版).电子工业出版社.2007

3、朱正涌.半导体集成电路.清华大学出版社.2000.282~285

4、饶妮妮.模拟电路基础.成都:电子科技大学出版社.2001

5、Saint J.Saintz 著周润德金申美译.集成电路掩模设计——基础版图技术.

清华大学出版社.2012

6、Phillip E.Allen,Douglas R.Holberg 著冯军李智群译.CMOS模拟集成电路设

计(第二版).电子工业出版社.2011

7、何乐年王忆模拟集成电路设计与仿真.科学出版社。