集成电路基础工艺和版图设计测试试卷

- 格式:doc

- 大小:31.50 KB

- 文档页数:3

集成电路技术集成电路工艺原理试卷(练习题库)1、用来做芯片的高纯硅被称为(),英文简称(),有时也被称为()。

2、单晶硅生长常用()和()两种生长方式,生长后的单晶硅被称为()。

3、晶圆的英文是(),其常用的材料是()和()。

4、晶圆制备的九个工艺步骤分别是()、整型、()、磨片倒角、刻蚀、()、清洗、检查和包装。

5、从半导体制造来讲,晶圆中用的最广的晶体平面的密勒符号是()、O 和()。

6、CZ直拉法生长单晶硅是把()变为()并且()的固体硅锭。

7、CZ直拉法的目的是()。

8、影响CZ直拉法的两个主要参数是O和()。

9、晶圆制备中的整型处理包括()、()和()。

10、制备半导体级硅的过程:1、();2、();3、O011、热氧化工艺的基本传输到芯片的不同部分。

77、多层金属化指用来连接硅片上高密度堆积器件的那些金属层。

78、阻挡层金属是淀积金属或金属塞,其作用是增加上下层材料的附着。

79、关键层是指那些线条宽度被刻蚀为器件特征尺寸的金属层。

80、传统互连金属线的材料是铝,即将取代它的金属材料是铜。

81、溅射是个化学过程,而非物理过程。

82、表面起伏的硅片进行平坦化处理,主要采用将低处填平的方法。

83、化学机械平坦化,简称CMP,它是一种表面全局平坦化技术。

84、平滑是一种平坦化类型,它只能使台阶角度圆滑和侧壁倾斜,但高度没有显著变化。

85、反刻是一种传统的平坦化技术,它能够实现全局平坦化。

86、电机电流终点检测不适合用作层间介质的化学机械平坦化。

87、在CMP为零的转换器。

133、CD是指硅片上的最小特征尺寸。

134、集成电路制造就是在硅片上执行一系列复杂的化学或者物理操作。

简而言之,这些操作可以分为四大基本类:薄膜135、人员持续不断地进出净化间,是净化间沾污的最大来源。

136、硅片制造厂可分为六个的区域,各个区域的照明都采用同一种光源以达到标准化。

137、世界上第一块集成电路是用硅半导体材料作为衬底制造的。

第1篇引言:集成电路(IC)设计是一项复杂而精细的工作,要求设计者具备深厚的理论知识、丰富的实践经验以及出色的逻辑思维能力。

为了帮助您了解自己在IC设计领域的智力水平,我们特别设计了以下智力测试题。

请您认真作答,完成后可对自己的设计能力有一个初步的认识。

第一部分:基础知识1. 选择题- 下列哪个选项不是IC设计中所使用的制造工艺?A. CMOSB. TTLC. ECLD. LED2. 填空题- 在IC设计中,版图(Layout)是电路的__________,而原理图(Schematic)则是电路的__________。

3. 简答题- 简述CMOS工艺的基本原理。

第二部分:逻辑分析与设计1. 选择题- 下列哪个电路可以实现逻辑与功能?A. OR门B. AND门C. NOT门D. XOR门- 在组合逻辑电路中,如果某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称为__________。

3. 简答题- 解释竞争与冒险现象,并说明如何消除它们。

第三部分:版图设计1. 选择题- 下列哪个工具常用于IC版图设计?A. Altium DesignerB. CadenceC. OrCADD. Pro/ENGINEER2. 填空题- 在版图设计中,为了防止寄生效应,通常需要将__________与__________保持一定的距离。

3. 简答题- 简述版图设计中的规则检查(DRC)和设计规则约束(DRC)。

第四部分:IC制造1. 选择题- 下列哪个步骤是IC制造过程中的关键步骤?A. 光刻B. 化学气相沉积C. 离子注入D. 刻蚀- 在IC制造中,__________是将电路图形转移到硅片上的关键步骤。

3. 简答题- 简述IC制造过程中可能遇到的问题及解决方法。

第五部分:模拟IC设计1. 选择题- 下列哪个电路属于模拟电路?A. 741运算放大器B. 555定时器C. 74LS00D. 74HC002. 填空题- 在模拟IC设计中,__________是放大信号的关键元件。

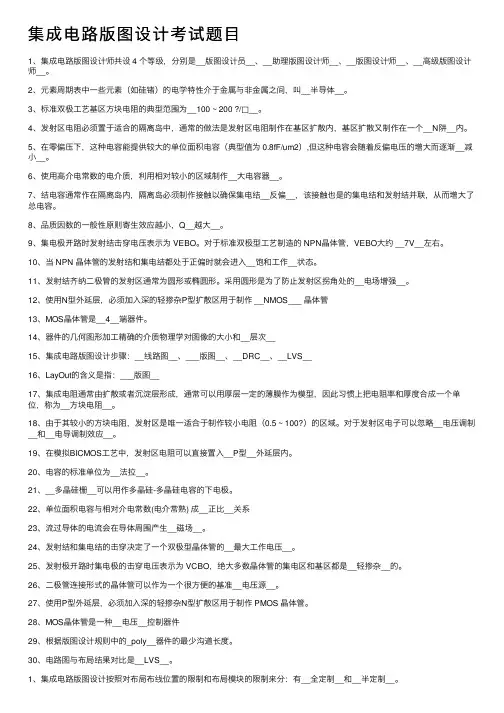

集成电路版图设计考试题⽬1、集成电路版图设计师共设 4 个等级,分别是__版图设计员__、__助理版图设计师__、__版图设计师__、__⾼级版图设计师__。

2、元素周期表中⼀些元素(如硅锗)的电学特性介于⾦属与⾮⾦属之间,叫__半导体__。

3、标准双极⼯艺基区⽅块电阻的典型范围为__100 ~ 200 ?/□__。

4、发射区电阻必须置于适合的隔离岛中,通常的做法是发射区电阻制作在基区扩散内,基区扩散⼜制作在⼀个__N阱__内。

5、在零偏压下,这种电容能提供较⼤的单位⾯积电容(典型值为 0.8fF/um2),但这种电容会随着反偏电压的增⼤⽽逐渐__减⼩__。

6、使⽤⾼介电常数的电介质,利⽤相对较⼩的区域制作__⼤电容器__。

7、结电容通常作在隔离岛内,隔离岛必须制作接触以确保集电结__反偏__,该接触也是的集电结和发射结并联,从⽽增⼤了总电容。

8、品质因数的⼀般性原则寄⽣效应越⼩,Q__越⼤__。

9、集电极开路时发射结击穿电压表⽰为 VEBO。

对于标准双极型⼯艺制造的 NPN晶体管,VEBO⼤约 __7V__左右。

10、当 NPN 晶体管的发射结和集电结都处于正偏时就会进⼊__饱和⼯作__状态。

11、发射结齐纳⼆极管的发射区通常为圆形或椭圆形。

采⽤圆形是为了防⽌发射区拐⾓处的__电场增强__。

12、使⽤N型外延层,必须加⼊深的轻掺杂P型扩散区⽤于制作 __NMOS___ 晶体管13、MOS晶体管是__4__端器件。

14、器件的⼏何图形加⼯精确的介质物理学对图像的⼤⼩和__层次__15、集成电路版图设计步骤:__线路图__、___版图__、__DRC__、__LVS__16、LayOut的含义是指:___版图__17、集成电阻通常由扩散或者沉淀层形成,通常可以⽤厚层⼀定的薄膜作为模型,因此习惯上把电阻率和厚度合成⼀个单位,称为__⽅块电阻__。

18、由于其较⼩的⽅块电阻,发射区是唯⼀适合于制作较⼩电阻(0.5 ~ 100?)的区域。

电子与通信技术:集成电路工艺原理考试试题(题库版)1、判断题对于大马士革工艺,重点是在于金属的刻蚀而不是介质的刻蚀。

正确答案:错2、判断题虽然直至今日我们仍普遍采用扩散区一词,但是硅片制造中已不再用杂质扩散来制作p(江南博哥)n结,取而代之的是离子注入。

正确答案:对3、判断题人员持续不断地进出净化间,是净化间沾污的最大来源。

正确答案:对4、问答题倒装焊芯片凸点的分类、结构特点及制作方法?正确答案:蒸镀焊料凸点:蒸镀焊料凸点有两种方法,一种是C4技术,整体形成焊料凸点;电镀焊料凸点:电镀焊料是一个成熟的工艺。

先整体形成UBM层并用作电镀的导电层,然后再用光刻胶保护不需要电镀的地方。

电镀形成了厚的凸点。

印刷焊料凸点:焊膏印刷凸点是一种广泛应用的凸点形成方法。

印刷凸点是采用模板直接将焊膏印在要形成凸点的焊盘上,然后经过回流而形成凸点钉头焊料凸点:这是一种使用标准的球形导线键合技术在芯片上形成的凸点方法。

可用Au丝线或者Pb基的丝线。

化学凸点:化学镀凸点是一种利用强还原剂在化学镀液中将需要镀的金属离子还原成该金属原子沉积在镀层表面形成凸点的方法。

5、问答题简要说明IC制造的平坦化工艺的作用是什么?主要有哪些方式?并解释各种方式的详细内容。

正确答案:在多层布线立体结构中,把成膜后的凸凹不平之处进行抛光研磨,使其局部或全局平坦化。

A.关于ECMP(电化学机械研磨方法),其工作步骤如下:首先,用电能使Cu氧化,再用络合剂使之生成Cu的络合物,最终研磨掉Cu络合物。

从对加工面进行研磨加工的原理观察,除了Cu的氧化方法之外,ECMP和CMP是同样的,而且加工面获得的平坦度性能也是同等水平。

但是,ECMP的必要条件是底座盘应具备导电性。

B.关于电解研磨ECP方法,利用电镀的逆反应。

从电场集中之处开始进行刻蚀,可获得平滑的研磨加工表面;但是,它能刻蚀平坦的区域只限于突起部分。

C.关于化学蚀刻CE构成的平坦化技术,它是把Si的精细加工等领域里使用的各向异性刻蚀用湿式刻蚀法实现的。

1+X集成电路理论考试题及答案一、单选题(共39题,每题1分,共39分)1.封装工艺的电镀工序中,完成前期的清洗后,下一步操作是()。

A、高温退火B、电镀C、装料D、后期清洗正确答案:B2.湿度卡的作用是( )。

A、去潮湿物质中的水分B、可以防止静电C、起到防水的作用D、显示密封空间的湿度状况正确答案:D答案解析:湿度卡是用来显示密封空间湿度状况的卡片。

3.“对刀”操作时,点击显示屏上主菜单的()按钮,使承载盘真空从关闭状态转为开启状态。

A、θ角度调整B、开始C、Work SetD、Manual Align正确答案:C答案解析:点击显示屏上主菜单的“Work Set”(设置)按钮,使承载盘真空从关闭状态转为开启状态。

点击显示屏上的“Manual Align”(手动对位)按钮,界面跳转到“切割道调整界面”。

点击“4.利用平移式分选机进行芯片分选时,吸嘴从()上吸取芯片,然后对芯片进行分选。

A、入料梭B、收料盘C、出料梭D、待测料盘正确答案:C5.如果遇到需要加温的晶圆,对晶圆的加温是在扎针调试( )。

A、之前B、之后C、过程中D、都可以正确答案:A答案解析:根据热胀冷缩的原理,需要加温的晶圆要在加温结束后再进行扎针调试。

若先进行扎针调试再加温可能会扎透铝层。

6.下列对芯片检测描述正确的是()。

A、集成电路测试是确保产品良率和成本控制的重要环节B、所有芯片的测试、分选和包装的类型相同C、测试完成后直接进入市场D、测试机分为数字测试机和模拟测试机正确答案:A7.口罩和发罩()。

A、需要定期清洗B、不得重复使用C、一周必须更换一次D、每天下班时放入消毒柜,下次对应取用正确答案:B答案解析:口罩和发罩不得重复使用,每天需穿戴全新的口罩和发罩。

8.待测芯片的封装形式决定了测试、分选和包装的不同类型,而不同的性能指标又需要对应的测试方案进行配套完成测试,测试完成后,经()即可进入市场。

A、运行测试后包装B、人工目检C、机器检测、人工目检D、人工目检、包装正确答案:D9.下列语句的含义是()。

版图设计笔试题及答案一、选择题(每题2分,共20分)1. 版图设计中,以下哪个不是版图设计的基本要求?A. 布局合理B. 布线简洁C. 颜色鲜艳D. 信号完整性答案:C2. 在版图设计中,以下哪个不是布线规则?A. 避免直角布线B. 保持线宽一致C. 尽量使用单层布线D. 避免信号线与电源线并行答案:C3. 以下哪个是版图设计中常用的软件工具?A. AutoCADB. MATLABC. PhotoshopD. Cadence Virtuoso答案:D4. 在版图设计中,电源和地线的设计原则是什么?A. 尽量短B. 尽量长C. 随意布置D. 与信号线交叉答案:A5. 以下哪个不是版图设计中需要考虑的电磁兼容性(EMC)问题?A. 信号完整性B. 电源完整性C. 电磁干扰D. 颜色搭配答案:D二、简答题(每题10分,共30分)1. 请简述版图设计中信号完整性的重要性。

答案:信号完整性是版图设计中的关键因素之一,它涉及到信号在传输过程中的保真度和稳定性。

如果信号完整性差,可能会导致信号失真、噪声干扰、时钟偏移等问题,从而影响整个电路的性能和可靠性。

2. 描述版图设计中布线的基本原则。

答案:版图设计中布线的基本原则包括:避免直角布线以减少信号反射;保持线宽一致以减少阻抗不连续;尽量使用地线作为信号线的参考平面;避免信号线与电源线并行以减少串扰。

3. 解释版图设计中的热设计考虑。

答案:热设计在版图设计中同样重要,它涉及到电路的散热问题。

设计时需要考虑功率器件的布局、散热路径的设计、以及散热材料的选择等,以确保电路在工作时温度保持在安全范围内。

三、计算题(每题25分,共50分)1. 假设有一个集成电路,其工作频率为100MHz,信号线长度为5cm。

请计算信号线上的最大允许电容值,以保证信号的传输速率不受电容影响。

答案:信号的传输速率与信号线上的电容值有关,可以通过以下公式计算最大允许电容值:C_max = (1 / (2πf)) * (t / v_p),其中f 为工作频率,t为信号传输时间,v_p为信号传播速度。

集成电路基础知识单选题100道及答案解析1. 集成电路的英文缩写是()A. ICB. CPUC. PCBD. ROM答案:A解析:集成电路的英文是Integrated Circuit,缩写为IC。

2. 以下不属于集成电路制造工艺的是()A. 光刻B. 蚀刻C. 焊接D. 扩散答案:C解析:焊接通常不是集成电路制造的核心工艺,光刻、蚀刻和扩散是常见的制造工艺。

3. 集成电路中,负责存储数据的基本单元是()A. 晶体管B. 电容器C. 电阻器D. 触发器答案:D解析:触发器是集成电路中用于存储数据的基本单元。

4. 以下哪种材料常用于集成电路的制造()A. 玻璃B. 塑料C. 硅D. 铝答案:C解析:硅是集成电路制造中最常用的半导体材料。

5. 集成电路的发展遵循()定律A. 摩尔B. 牛顿C. 爱因斯坦D. 法拉第答案:A解析:集成电路的发展遵循摩尔定律。

6. 集成电路封装的主要作用不包括()A. 保护芯片B. 散热C. 提高性能D. 便于连接答案:C解析:封装主要是保护、散热和便于连接,一般不能直接提高芯片的性能。

7. 在数字集成电路中,逻辑门是由()组成的A. 二极管B. 三极管C. 场效应管D. 晶闸管答案:C解析:场效应管常用于数字集成电路中构成逻辑门。

8. 以下哪种集成电路属于模拟集成电路()A. 微处理器B. 计数器C. 放大器D. 编码器答案:C解析:放大器属于模拟集成电路,其他选项通常属于数字集成电路。

9. 集成电路的集成度是指()A. 芯片面积B. 晶体管数量C. 工作频率D. 功耗答案:B解析:集成度通常指芯片上晶体管的数量。

10. 集成电路设计中,常用的硬件描述语言有()A. C 语言B. Java 语言C. VerilogD. Python 语言答案:C解析:Verilog 是集成电路设计中常用的硬件描述语言。

11. 以下关于集成电路测试的说法错误的是()A. 可以检测芯片的功能是否正常B. 可以提高芯片的可靠性C. 测试只在生产完成后进行D. 有助于筛选出不合格的芯片答案:C解析:集成电路测试在生产过程的多个阶段都可能进行,不只是在生产完成后。

集成电路基础⼯艺和版图设计测试试卷集成电路基础⼯艺和版图设计测试试卷(考试时间:60分钟,总分100分)第⼀部分、填空题(共30分。

每空2分)1、NMOS是利⽤电⼦来传输电信号的⾦属半导体;PMOS是利⽤空⽳来传输电信号的⾦属半导体。

2、集成电路即“IC”,俗称芯⽚,按功能不同可分为数字集成电路和模拟集成电路,按导电类型不同可分为双极型集成电路和单极型集成电路,前者频率特性好,但功耗较⼤,⽽且制作⼯艺复杂,不利于⼤规模集成;后者⼯作速度低,但是输⼊阻抗⾼、功耗⼩、制作⼯艺简单、易于⼤规模集成。

3、⾦属(metal)—氧化物(oxid)—半导体(semiconductor)场效应晶体管即MOS管,是⼀个四端有源器件,其四端分别是栅极、源极、漏极、背栅。

4、集成电路设计分为全定制设计⽅法和半定制设计⽅法,其中全定制设计⽅法⼜分为基于门阵列和标准单元的设计⽅法,芯⽚利⽤率最低的是基于门阵列的设计⽅法。

第⼆部分、不定项选择题(共45分。

每题3分,多选,错选不得分,少选得1分)1、在CMOS集成电路中,以下属于常⽤电容类型的有(ABCD)A、MOS电容B、双层多晶硅电容C、⾦属多晶硅电容D、⾦属—⾦属电容2、在CMOS集成电路中,以下属于常⽤电阻类型的有(ABCD)A、源漏扩散电阻B、阱扩散电阻C、沟道电阻D、多晶硅电阻3、以下属于⽆源器件的是(CD )A、MOS晶体管B、BJT晶体管C、POL Y电阻D、MIM电容4、与芯⽚成本相关的是(ABC)A、晶圆上功能完好的芯⽚数B、晶圆成本C、芯⽚的成品率D、以上都不是5、通孔的作⽤是(AB )A、连接相邻的不同⾦属层B、使跳线成为可能C、连接第⼀层⾦属和有源区D、连接第⼀层⾦属和衬底6、IC版图的可靠性设计主要体现在(ABC)等⽅⾯,避免器件出现毁灭性失效⽽影响良率。

A、天线效应B、闩锁(Latch up)C、ESD(静电泄放)保护D、⼯艺⾓(process corner)分析7、减⼩晶体管尺⼨可以有效提⾼数字集成电路的性能,其原因是(AB)A、寄⽣电容减⼩,增加开关速度B、门延时和功耗乘积减⼩C、⾼阶物理效应减少D、门翻转电流减⼩8、⼀般在版图设计中可能要对电源线等⾮常宽的⾦属线进⾏宽⾦属开槽,主要是抑制热效应对芯⽚的损害。

IC设计基础(流程、工艺、版图、器件)笔试集锦1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

(仕兰微面试题目)什么是MCU?MCU(Micro Controller Unit),又称单片微型计算机(Single Chip Microcomputer),简称单片机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机。

MCU的分类MCU按其存储器类型可分为MASK(掩模)ROM、OTP(一次性可编程)ROM、FLASH ROM等类型。

MASK ROM的MCU 价格便宜,但程序在出厂时已经固化,适合程序固定不变的应用场合;FALSH ROM的MCU程序可以反复擦写,灵活性很强,但价格较高,适合对价格不敏感的应用场合或做开发用途;OTP ROM的MCU价格介于前两者之间,同时又拥有一次性可编程能力,适合既要求一定灵活性,又要求低成本的应用场合,尤其是功能不断翻新、需要迅速量产的电子产品。

RISC为Reduced Instruction Set Computing的缩写,中文翻译为精简执令运算集,好处是 CPU核心很容易就能提升效能且消耗功率低,但程式撰写较为复杂;常见的RISC处理器如 Mac的Power PC系列。

CISC就是Complex Instruction Set Computing的缩写,中文翻译为复杂指令运算集,它只是 CPU分类的一种,好处是CPU所提供能用的指令较多、程式撰写容易,常见80X86相容的CPU即是此类。

DSP有两个意思,既可以指数字信号处理这门理论,此时它是Digital Signal Processing的缩写;也可以是Digital Signal Processor的缩写,表示数字信号处理器,有时也缩写为DSPs,以示与理论的区别。

集成电路设计基础(工艺、版图、流程、器件)1、什么叫Latchup,如何预防闩锁效应?(仕兰、科广试题)Q1为一纵向PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一横向的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate电阻。

以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT 处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

产生Latch up 的具体原因:• 芯片一开始工作时VDD变化导致nwell和P substrate间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起Latch up。

• 当I/O的信号变化超出VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致SCR的触发。

• E SD静电加压,可能会从保护电路中引入少量带电载子到well或substrate中,也会引起SCR的触发。

• 当很多的驱动器同时动作,负载过大使power和gnd突然变化,也有可能打开SCR的一个BJT。

• Well 侧面漏电流过大。

消除“Latch-up”效应的方法:版图设计时:①为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;②避免source和drain的正向偏压;③使用Guard ring: P+ ring环绕nmos并接GND;N+ ring环绕pmos并接VDD,一方面可以降低Rwell和Rsub的阻值,另一方面可阻止载流子到达BJT的基极。

集成电路基础知识试题### 集成电路基础知识试题#### 一、选择题(每题2分,共20分)1. 集成电路的英文缩写是:A. ICB. CPUC. RAMD. ROM2. 下列哪个不是集成电路的基本元件?A. 晶体管B. 电阻C. 电容D. 硬盘3. 集成电路的制造工艺中,光刻是用于:A. 形成电路图案B. 清洗硅片C. 检测电路D. 封装电路4. CMOS技术中,CMOS代表:A. 互补金属氧化物半导体B. 计算机操作与制造系统C. 复杂多输出系统D. 连续多输入系统5. 以下哪个是集成电路设计中的后端流程?A. 逻辑综合B. 电路仿真C. 布局与布线D. 原理图绘制#### 二、填空题(每空2分,共20分)6. 集成电路按照制造材料可以分为______和______两大类。

7. 集成电路的最小特征尺寸通常用______来表示。

8. 集成电路的功耗主要由______和______组成。

9. 在数字集成电路中,最基本的逻辑门是______、______、非门和或门。

10. 集成电路的封装类型包括DIP、BGA、______等。

#### 三、简答题(每题15分,共30分)11. 简述集成电路的发展历程及其对未来电子技术的影响。

集成电路自20世纪50年代诞生以来,经历了从小规模集成电路(SSI)到超大规模集成电路(VLSI)的快速发展。

这一过程不仅极大地推动了电子技术的革新,也为现代信息技术、通信技术、计算机技术等领域的发展奠定了基础。

集成电路的高集成度、低功耗、低成本等特点,使其成为现代电子设备不可或缺的核心组件。

未来,随着新材料、新工艺的不断涌现,集成电路将继续向着更高性能、更小尺寸的方向发展,为人类社会带来更多的便利和创新。

12. 解释什么是互补金属氧化物半导体(CMOS)技术,并简述其优缺点。

互补金属氧化物半导体(CMOS)技术是一种广泛应用于现代集成电路制造的工艺技术。

它利用了P型和N型MOSFET的互补特性,实现了低功耗、高集成度的电路设计。

集成电路基础工艺和版图设计测试试卷

(考试时间:60分钟,总分100分)

第一部分、填空题(共30分。

每空2分)

1、NMOS是利用电子来传输电信号的金属半导体;PMOS是利用空穴来传输电信号的金属半导体。

2、集成电路即“IC”,俗称芯片,按功能不同可分为数字集成电路和模拟集成电路,按导电类型不同可分为

双极型集成电路和单极型集成电路,前者频率特性好,但功耗较大,而且制作工艺复杂,不利于大规模集成;后者工作速度低,但是输入阻抗高、功耗小、制作工艺简单、易于大规模集成。

3、金属(metal)—氧化物(oxid)—半导体(semiconductor)场效应晶体管即MOS管,是一个四端有源器件,其四端分别是栅

极、源极、漏极、背栅。

4、集成电路设计分为全定制设计方法和半定制设计方法,其中全定制设计方法又分为基于门阵列和标准单元

的设计方法,芯片利用率最低的是基于门阵列的设计方法。

第二部分、不定项选择题(共45分。

每题3分,多选,错选不得分,少选得1分)

1、在CMOS集成电路中,以下属于常用电容类型的有(ABCD)

A、MOS电容

B、双层多晶硅电容

C、金属多晶硅电容

D、金属—金属电容

2、在CMOS集成电路中,以下属于常用电阻类型的有(ABCD)

A、源漏扩散电阻

B、阱扩散电阻

C、沟道电阻

D、多晶硅电阻

3、以下属于无源器件的是(CD )

A、MOS晶体管

B、BJT晶体管

C、POL Y电阻

D、MIM电容

4、与芯片成本相关的是(ABC)

A、晶圆上功能完好的芯片数

B、晶圆成本

C、芯片的成品率

D、以上都不是

5、通孔的作用是(AB )

A、连接相邻的不同金属层

B、使跳线成为可能

C、连接第一层金属和有源区

D、连接第一层金属和衬底

6、IC版图的可靠性设计主要体现在(ABC)等方面,避免器件出现毁灭性失效而影响良率。

A、天线效应

B、闩锁(Latch up)

C、ESD(静电泄放)保护

D、工艺角(process corner)分析

7、减小晶体管尺寸可以有效提高数字集成电路的性能,其原因是(AB)

A、寄生电容减小,增加开关速度

B、门延时和功耗乘积减小

C、高阶物理效应减少

D、门翻转电流减小

8、一般在版图设计中可能要对电源线等非常宽的金属线进行宽金属开槽,主要是抑制热效应对芯片的损害。

下面哪些做法符合宽金属开槽的基本规则?(ABCD)

A、开槽的拐角处呈45度角,减轻大电流密度导致的压力

B、把很宽的金属线分成几个宽度小于规则最小宽度的金属线

C、开槽的放置应该总是与电流的方向一致

D、在拐角、T型结构和电源PAD区域开槽之前要分析电流流向

9、以下版图的图层中与工艺制造中出现的外延层可能直接相接触的是(AB)。

A、AA(active area)

B、NW(N-Well)

C、POLY

D、METAL1

10、以下内容哪些被包含在设计规则检查中?(ABD)

A、宽度规则

B、间距规则

C、时序约束

D、交叠规则

11、属于PAD单元组成部分的是(ABC)。

A、ESD保护结构

B、绑定金属线所需的可靠连接区域

C、与PAD功能相关的逻辑电路,如输入/输出缓冲

D、片上存储单元

12、实际的MOS晶体管存在一些二阶效应,以下属于二阶效应的是(ABCD)。

A、阈值变化(受沟道长度影响,受源漏电压影响等)

B、热载流子效应

C、体效应

D、沟道长度调制效应

13、模拟差分对由于不匹配会存在一定的输入失调(offset),这主要由于(AB)的原因。

A、晶体管阈值电压存在偏差

B、晶体管的形状在制造上存在随机偏差

C、版图设计者的失误

D、制造过程中栅氧局部击穿

14、常见的CMOS工艺中,MOS晶体管的栅极采用多晶硅作为电极材料,下面关于多晶硅的表述正确的是(ABC)

A、多晶硅能承受源/漏参杂和退火时所需的高温

B、掺磷的多晶硅能够固定离子污染物

C、使用多晶硅可以更好的控制MOS晶体管的门限电压

D、可多用来制作PN结

15、以下哪些做法有利于提高MOS晶体管的匹配度(AD)。

A、采用相同的几何形状,摆放紧凑

B、采用比较小的有源区

C、采用较大的过驱动电压来保持电压匹配

D、尽量将晶体管采用共质心版图

第三部分、简答题(共15分。

每题5分)

1、根据你的理解,请用1~5标出IC设计流程的先后顺序

系统设计(1)版图设计(4)逻辑设计(2)版图后仿真(5)电路设计(3)

2、如果一条给定CMOS的工艺线有如下的层次,请按各层次在工艺制造过程中的先后顺序排列他们。

POL Y1 N_WELL DIFF N+(NPLUS) PAD P+(PPLUS) METAL1 CONTACT(CONT) VIA METAL2 顺序:N_WELL—DIFF—POL Y1—N+(NPLUS)或P+(PPLUS)—CONTACT(CONT)—METAL1—VIA—METAL2—PAD

3、请解释如下design rule 语句的含义。

Minimum DIFFUSION width for interconnect 0.5um

解释:用于连线的DIFFUSION层的最小宽度为0.5um.

Minimum N_WELL to P+ DIFFUSION spacing 1.0um

解释:N_WELL 层到P+ DIFFUSION 层的最小间距为 1.0um.

第四部分、分析题(共10分)

1、从下图分析Latch up现象产生机理,并指出在版图设计中如何抑制该现象的产生。

如何抑制该现象的产生:

尽量减小Rn 和Rp 两个电阻的大小,在版图上表现为在电源和地线上尽量多打tub_ties的孔。

尽量拉大nmos管与pmos管的间距。