第三章 集成电路版图设计基础

- 格式:ppt

- 大小:3.45 MB

- 文档页数:49

第三章集成电路版图设计每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:最小线宽 Minimum Width最小间距 Minimum Spacing最小延伸 Minimum Extension最小包围 Minimum Enclosure 最小覆盖 Minimum Overlay集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!3.2模拟集成电路版图设计中遵从的法则3.2.1电容的匹配对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容易达到高精度的匹配。

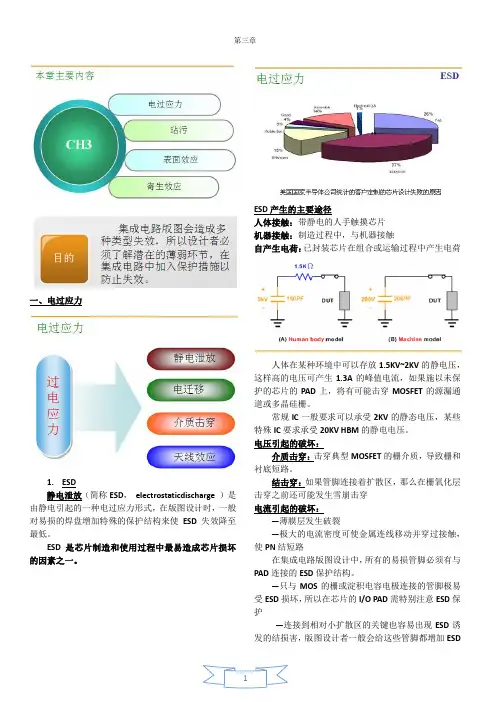

一、电过应力1.ESD静电泄放(简称ESD,electrostaticdischarge )是由静电引起的一种电过应力形式,在版图设计时,一般对易损的焊盘增加特殊的保护结构来使ESD失效降至最低。

ESD是芯片制造和使用过程中最易造成芯片损坏的因素之一。

ESD产生的主要途径人体接触:带静电的人手触摸芯片机器接触:制造过程中,与机器接触自产生电荷:已封装芯片在组合或运输过程中产生电荷人体在某种环境中可以存放1.5KV~2KV的静电压,这样高的电压可产生1.3A的峰值电流,如果施以未保护的芯片的PAD上,将有可能击穿MOSFET的源漏通道或多晶硅栅。

常规IC一般要求可以承受2KV的静态电压,某些特殊IC要求承受20KV HBM的静电电压。

电压引起的破坏:介质击穿:击穿典型MOSFET的栅介质,导致栅和衬底短路。

结击穿:如果管脚连接着扩散区,那么在栅氧化层击穿之前还可能发生雪崩击穿电流引起的破坏:—薄膜层发生破裂—极大的电流密度可使金属连线移动并穿过接触,使PN结短路在集成电路版图设计中,所有的易损管脚必须有与PAD连接的ESD保护结构。

—只与MOS的栅或淀积电容电极连接的管脚极易受ESD损坏,所以在芯片的I/O PAD需特别注意ESD保护—连接到相对小扩散区的关键也容易出现ESD诱发的结损害,版图设计者一般会给这些管脚都增加ESD保护器件。

—一些特殊的管脚可以抗ESD,因此可以不加防护。

典型的功率管的管脚会与大的扩散区连接,这类管脚可以不加ESD保护电路。

2.电迁移:集成电路中电迁移是由极高的电流密度引起的缓慢的损耗现象,移动的载流子对静止的金属原子的影响引起了金属的逐渐移位。

铝的电流密度接近5X105A/cm2时,电迁移现象变得很明显。

由于金属层厚度很薄,所以在亚微米工艺中最小线宽的金属在几毫安的电流下就会出现电迁移。

电迁移引起金属原子逐渐移出,形成空隙,这使得连线的有效横截面积减小引起连线剩余部分的电流密度增大,电迁移现象更加明显并逐渐结合,最终切断连线,导致断路。