- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

需要匹配的器件彼此靠近 注意周围器件 保持匹配器件方向一致

遵守这 3条基本原则, 就可以很好的实现匹配.

school of phye

basics of ic layout design

12

匹配方法 之一:根器件方法 root device method 之一:

根部件,在这里指这样一个电阻,可以根据这一个电阻设计出所 有其他的电阻. 我们经常在选择根器件的时侯, 用最小的电阻作为根器件,这样的 选择当然也可以实现我们需要的匹配, 但同时我们却忽略了另外 一个问题,那就是像 2 K 这样的电阻如果用 2 5 0 做根器件, 那么就需要 8个根器件串联起来实现, 这就导致了这 8个电阻之 间接触电阻也同时加大了,这是我们不希望看到的. 采用根部件的最好方法是找出一个中间值,例如用 1 K 的电阻 作为值将电阻串联和并联起来.这种方法节省了接触电阻的总数 接触电阻的总数 使其所占的比例减少 面积 减少, 减少,因为电阻之间的间隙数 减少 面积也许会减少 减少 薄层电阻,而非接触 少了,现在占主导地位 主导地位的是电阻器件本身的薄层电阻 而非接触 主导地位 薄层电阻 电阻. 电阻 利用根部件时, 如果所有的电阻尺寸一样, 形状一样, 方向一致而 且相互靠近, 那么就可以得到一个很好的匹配.

2

匹配规则

之一:把匹配器件相互靠近放置. 把匹配器件相互靠近放置.

place matched devices close to each other.

之二:使器件保持同一方向. 使器件保持同一方向.

keep devices in the same orientation.

之三:选择一个中间值作为根部件. 选择一个中间值作为根部件. choose a middle value for a root component.

regular (rectangular shape)

parallel elements

Possibly, the current flowing in the same direction.

school of phye

basics of ic layout design

8

简单匹配 - asymmetry due to fabrication

cross-guad your device pairs.

school of phye

basics of ic layout design

4

匹配规则

之七:使布线上的寄生参数匹配. 使布线上的寄生参数匹配.

match the parasitics on your wiring.

之八:使每一样东西都对称. 使每一样东西都对称.

school of phye basics of ic layout design 13

匹配方法 之一:根器件方法 root device method 之一:

1k

2k

2k

500

250

1k

2k

2k

500

250

school of phye

basics of ic layout design

14

匹配方法 之二:交叉法 interdigitating device 之二:

河

南

大

学

Henan

University

集成电路版图设计基础

basics of IC layout design

instructor: Zhang Qihui e-mail:qhzhang07@

第六章 寄生参数

匹配规则 简单匹配 匹配方法

school of phye

basics of ic layout design

20 19.8 20 20.5

basics of ic layout design

2 1.8

2 2.5

school of phye

11

匹配方法

当集成电路产业刚刚起步的时候,制造工业仍然相对落 后.即使你将两个需要匹配的器件放的很近, 我们也仍 然无法保证它们的一致性. 现在虽然制造工艺越来越 精确,但是匹配问题的研究从来就没有停止过, 相反地, 匹配问题显得日益突出和重要. 匹配分为横向匹配, 纵向匹配和中心匹配.实现匹配 有三个要点需要考虑:

school of phye

basics of ic layout design

18

匹配方法 之二:交叉法 interdigitating device 之二:

1

2

3

AABBAABB pattern

ABBAABBA pattern

school of phye

basics of ic layout design

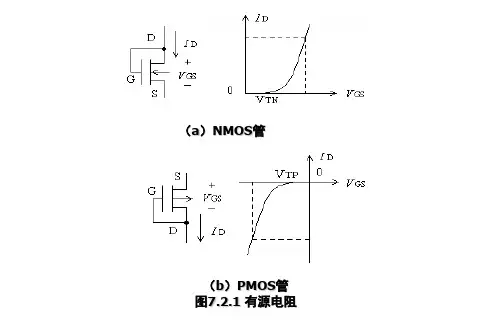

大角度离子注入( 离子注入工艺) 大角度离子注入(100nm离子注入工艺) 离子注入工艺 随着器件特征尺寸的不断缩小,工艺制造进入0.100.13m技术代,此时短沟道效应的现象最为突出即: 当FET源极和漏极之间的距离变小时MOSFET的阈电 压下降. 100nm器件工艺必须用到大角度离子注入工艺,即 Halo的注入工艺.主要是防止漏源相通,降低延伸区 的结深以及缩短沟道长度,使载流子分布更陡,提高 芯片的性能.

19

匹配方法 之二:交叉法 interdigitating device 之二:

Axis of Symmetries:

school of phye

basics of ic layout design

20

匹配方法 之二:交叉法 interdigitating device 之二:

Interdigitation Patterns:

school of phye

basics of ic layout design

9

简单匹配 - asymmetry due to fabrication

an MOS transistor is not a symmetrical device. to avoid channeling of implanted ions the wafer is tilted by about 7 degrees.

之十一:采用尺寸较大的器件. 采用尺寸较大的器件.

go large.

之十二:总是与电路设计者交流. 总是与电路设计者交流.

always communicate with your circuit designer.

school of phye

basics of ic layout design

6

匹配规则

school of phye

basics of ic layout design

3

匹配规则

之四:采用指状交叉方式. 采用指状交叉方式.

interdigitate.

之五:用虚设器件包围起来. 用虚设器件包围起来.

surround yourself with dummies.

之六:四方交叉成对器件. 四方交叉成对器件.

analog transistors often have a large W/L ratio. Interdigitization can be used in a multiple transistor circuit layout to distribute process gradients across the circuit. This improves matching. two matched transistors with one node in common: ★ split them in an equal part of fingers (for example 4) ★ interdigitate the 8 elements: AABBAABB or ABBAABBA

通常在电路中有些大堆部件都必须与一个给定的器件匹配,这个 器件称为定义部件 定义部件(图5-5,P104). 定义部件

两组电阻指状交叉排列

将其指状交叉匹配 指状交叉部件的布线

school of phye basics of ic layout design 15

匹配方法 之二:交叉法 interdigitating device 之二:

school of phye

basics of ic layout design

16

匹配方法 之二:交叉法 interdigitating device 之二:

school of phye

basics of ic layout design

17

匹配方法 之二:交叉法 interdigitating device 之二:

keep everything in symmetry.

之九:使差分布线一致. 使差分布线一致.

make differential logic identical.

school of phye

basics of ic layout design

5

匹配规则

之 十:使器件宽度一致. 使器件宽度一致.

match device widths.

之十三:掩模设计者不会心灵感应. 掩模设计者不会心灵感应.

mask designer are not phychic.

之十四:注意临近的器件. 注意临近的器件.

watch the neighbors.

school of phye

basics of ic layout design

7

简单匹配 - matching single transistor

Interdigitize large aspect ratio devices to reduce source/drain depletion capacitance Using an even capacitance. number (n) of gate fingers can reduce Cdb, Csb to oneonehalf or (n+2)/2n depending on source/drain designation. Typically it is preferred to reduce drain capacitance more so than source capacitance. Also use dummy poly strips to minimize mismatch induced by etch undercutting during fab. And these widths of dummy gates can be shorter than the actual gates gates.