Full Suite Overview Presentation for CPs FINAL - Chinese V2

- 格式:ppt

- 大小:6.12 MB

- 文档页数:51

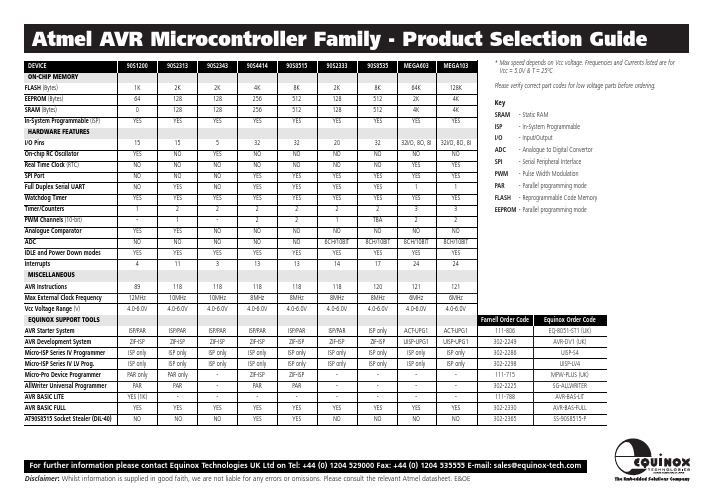

Continued....Errata•Reset During EEPROM Write•Verifying EEPROM in System•Serial Programming at Voltages below 3.0 Volts3.Reset During EEPROM WriteIf reset is activated during EEPROM write the result is not what should be expected. The EEPROM write cycle completes as normal, but the address regis-ters are reset to 0. The result is that both the address written and address 0 in the EEPROM can be corrupted.Problem Fix/WorkaroundAvoid using address 0 for storage, unless you can guarantee that you will not geta reset during EEPROM write.2.Verifying EEPROM in SystemEEPROM verify in In-System Programming mode cannot operate with maximum clock frequency. This is independent of the SPI clock frequency.Problem Fix/WorkaroundReduce the clock speed, or avoid using the EEPROM verify feature.1.Serial Programming at Voltages below 3.0 VoltsAt voltages below 3.0 Volts, serial programming might fail.Problem Fix/WorkaroundKeep V CC at 3.0 Volts or higher during In-System Programming.Microcontroller with 1K bytes In-System Programmable FlashAT90S1200/A Rev. FErrata SheetRev. 1190B–01/99© Atmel Corporation 1999.Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard war-ranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual prop-erty of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel HeadquartersAtmel OperationsCorporate Headquarters2325 Orchard Parkway San Jose, CA 95131TEL (408) 441-0311FAX (408) 487-2600EuropeAtmel U.K., Ltd.Coliseum Business Centre Riverside WayCamberley, Surrey GU15 3YL EnglandTEL (44) 1276-686677FAX (44) 1276-686697AsiaAtmel Asia, Ltd.Room 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon, Hong Kong TEL (852) 27219778FAX (852) 27221369JapanAtmel Japan K.K.Tonetsu Shinkawa Bldg., 9F 1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTEL (81) 3-3523-3551FAX (81) 3-3523-7581Atmel Colorado Springs1150 E. Cheyenne Mtn. Blvd.Colorado Springs, CO 80906TEL (719) 576-3300FAX (719) 540-1759Atmel RoussetZone Industrielle13106 Rousset Cedex, France TEL (33) 4 42 53 60 00FAX (33) 4 42 53 60 01Fax-on-DemandNorth America:1-(800) 292-8635International:1-(408) 441-0732e-mail********************Web Site BBS1-(408) 436-4309Features•Utilizes the AVR®RISC Architecture•AVR - High-performance and Low-power RISC Architecture –89 Powerful Instructions - Most Single Clock Cycle Execution –32 x 8 General Purpose Working Registers–Up to 12 MIPS Throughput at 12 MHz•Data and Nonvolatile Program Memory–1K Bytes of In-System Programmable FlashEndurance: 1,000 Write/Erase Cycles–64 Bytes of In-System Programmable EEPROMEndurance: 100,000 Write/Erase Cycles–Programming Lock for Flash Program and EEPROM Data Security•Peripheral Features–One 8-bit Timer/Counter with Separate Prescaler–On-chip Analog Comparator–Programmable Watchdog Timer with On-chip Oscillator–SPI Serial Interface for In System Programming•Special Microcontroller Features–Low-power Idle and Power Down Modes–External and Internal Interrupt Sources–Selectable On-chip RC Oscillator for Zero External Components •Specifications–Low-power, High-speed CMOS Process Technology–Fully Static Operation•Power Consumption at 4 MHz, 3V, 25°C–Active: 2.0 mA–Idle Mode: 0.4 mA–Power Down Mode: <1 µA•I/O and Packages–15 Programmable I/O Lines–20-pin PDIP and SOIC•Operating Voltages–2.7 - 6.0V (AT90S1200-4)–4.0 - 6.0V (AT90S1200-12)•Speed Grades–0 - 4 MHz, (AT90S1200-4)–0 - 12 MHz, (AT90S1200-12)DescriptionThe AT90S1200 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the Microcontroller with 1K bytesAT90S1200 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consump-tion versus processing speed.The AVR core combines a rich instruction set with the 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.Block DiagramFigure 1. The AT90S1200 Block DiagramAT90S1200The architecture supports high level languages efficiently as well as extremely dense assembler code programs. The AT90S1200 provides the following features: 1K bytes of In-System Programmable Flash, 64 bytes EEPROM, 15 general purpose I/O lines, 32 general purpose working registers, internal and external interrupts, programmable Watchdog Timer with internal oscillator, an SPI serial port for program downloading and two software selectable power saving modes. The Idle Mode stops the CPU while allowing the registers, timer/counter, watchdog and interrupt system to continue functioning. The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next external interrupt or hardware reset.The device is manufactured using Atmel’s high density non-volatile memory technology. The on-chip In-System Program-mable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an enhanced RISC 8-bit CPU with In-System Programmable Flash on a monolithic chip, the Atmel AT90S1200 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.The AT90S1200 AVR is supported with a full suite of program and system development tools including: macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.Pin DescriptionsVCCSupply voltage pin.GNDGround pin.Port B (PB7..PB0)Port B is an 8-bit bi-directional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). PB0 and PB1 also serve as the positive input (AIN0) and the negative input (AIN1), respectively, of the on-chip analog comparator. The Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not active.Port D (PD6..PD0)Port D has seven bi-directional I/O pins with internal pull-up resistors, PD6..PD0. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not active.RESETReset input. A low level on this pin for more than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.Architectural OverviewThe fast-access register file concept contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This means that during one single clock cycle, one ALU (Arithmetic Logic Unit) operation is executed. Two operands are output from the register file, the operation is executed, and the result is stored back in the register file - in one clock cycle.Figure 2. The AT90S1200 AVR Enhanced RISC ArchitectureThe ALU supports arithmetic and logic functions between registers or between a constant and a register. Single register operations are also executed in the ALU. Figure 2 shows the AT90S1200 AVR Enhanced RISC microcontroller architec-ture. The AVR uses a Harvard architecture concept - with separate memories and buses for program and data memories. The program memory is accessed with a two stage pipeline. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Programmable Flash memory.With the relative jump and relative call instructions, the whole 512 address space is directly accessed. All AVR instructions have a single 16-bit word format, meaning that every program memory address contains a single 16-bit instruction. During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is a 3level deep hardware stack dedicated for subroutines and interrupts.The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, Timer/Counters, A/D-converters, and other I/O functions. The memory spaces in the AVR architecture are all linear and regular memory maps.A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the p ro-gram memory. The different interrupts have priority in accordance with their interrupt vector position. The lower theAT90S1200AT90S1200 Register SummaryAddress Name Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0 $3F SREG I T H S V N Z C$3E Reserved$3D Reserved$3C Reserved$3B GIMSK-INT0------$3A Reserved$39TIMSK------TOIE0-$38TIFR------TOV0-$37Reserved$36Reserved$35MCUCR--SE SM--ISC01ISC00 $34Reserved$33TCCR0-----CS02CS01CS00 $32TCNT0 Timer/Counter0 (8 Bit)$31Reserved$30Reserved$2F Reserved$2E Reserved$2D Reserved$2C Reserved$2B Reserved$2A Reserved$29Reserved$28Reserved$27Reserved$26Reserved$25Reserved$24Reserved$23Reserved$22Reserved$21WDTCR----WDE WDP2WDP1WDP0 $20Reserved$1F Reserved$1E EEAR- EEPROM Address Register$1D EEDR EEPROM Data Register$1C EECR------EEWE EERE $1B Reserved$1A Reserved$19Reserved$18PORTB PORTB7PORTB6PORTB5PORTB4PORTB3PORTB2PORTB1PORTB0 $17DDRB DDB7DDB6DDB5DDB4DDB3DDB2DDB1DDB0 $16PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB0 $15Reserved$14Reserved$13Reserved$12PORTD-PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD0 $11DDRD-DDD6DDD5DDD4DDD3DDD2DDD1DDD0 $10PIND-PIND6PIND5PIND4PIND3PIND2PIND1PIND0 $0F Reserved...Reserved$09Reserved$08ACSR ACD-ACO ACI ACIE-ACIS1ACIS0…Reserved$00ReservedNotes: 1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.2.Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate onall bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructionswork with registers $00 to $1F only.Instruction Set SummaryMnemonics Operands Description Operation Flags#Clocks ARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two Registers Rd ← Rd + Rr Z,C,N,V,H1 ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H1 SUB Rd, Rr Subtract two Registers Rd ← Rd - Rr Z,C,N,V,H1 SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H1 SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H1 SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H1 AND Rd, Rr Logical AND Registers Rd ← Rd • Rr Z,N,V1 ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V1 OR Rd, Rr Logical OR Registers Rd ← Rd v Rr Z,N,V1 ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V1 EOR Rd, Rr Exclusive OR Registers Rd ← Rd⊕Rr Z,N,V1 COM Rd One’s Complement Rd ← $FF - Rd Z,C,N,V1 NEG Rd T wo’s Complement Rd ← $00 - Rd Z,C,N,V,H1 SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V1 CBR Rd,K Clear Bit(s) in Register Rd ← Rd • (FFh - K)Z,N,V1 INC Rd Increment Rd ← Rd + 1Z,N,V1 DEC Rd Decrement Rd ← Rd - 1 Z,N,V1 TST Rd T est for Zero or Minus Rd ← Rd • Rd Z,N,V1 CLR Rd Clear Register Rd ← Rd⊕Rd Z,N,V1 SER Rd Set Register Rd ← $FF None1 BRANCH INSTRUCTIONSRJMP k Relative Jump PC ← PC + k + 1 None2 RCALL k Relative Subroutine Call PC ← PC + k + 1None3 RET Subroutine Return PC ← ST ACK None4 RETI Interrupt Return PC ← ST ACK I4 CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1 / 2 CP Rd,Rr Compare Rd - Rr Z, N,V,C,H1 CPC Rd,Rr Compare with Carry Rd - Rr - C Z, N,V,C,H1 CPI Rd,K Compare Register with Immediate Rd - K Z, N,V,C,H1 SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1 / 2 SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None 1 / 2 SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1 / 2 SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None 1 / 2 BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC←PC + k + 1None 1 / 2 BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC←PC + k + 1None 1 / 2 BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1 / 2 BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1 / 2 BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1 / 2 BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1 / 2 BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1 / 2 BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1 / 2 BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1 / 2 BRPL k Branch if Plus if (N = 0) then PC ← PC + k + 1None 1 / 2 BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None 1 / 2 BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None 1 / 2 BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None 1 / 2 BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1 / 2 BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None 1 / 2 BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None 1 / 2 BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1 / 2 BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None 1 / 2 BRIE k Branch if Interrupt Enabled if (I = 1) then PC ← PC + k + 1None 1 / 2 BRID k Branch if Interrupt Disabled if (I = 0) then PC ← PC + k + 1None 1 / 2 DATA TRANSFER INSTRUCTIONSLD Rd,Z Load Register Indirect Rd ← (Z)None2 ST Z,Rr Store Register Indirect(Z) ← Rr None2 MOV Rd, Rr Move Between Registers Rd ← Rr None1 LDI Rd, K Load Immediate Rd ← K None1IN Rd, P In Port Rd ← P None1 OUT P, Rr Out Port P ← Rr None1AT90S1200Instruction Set Summary (Continued)Mnemonics Operands Description Operation Flags#Clocks BIT AND BIT-TEST INSTRUCTIONSSBI P,b Set Bit in I/O Register I/O(P,b) ← 1None2 CBI P,b Clear Bit in I/O Register I/O(P,b) ← 0None2 LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V1 LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V1 ROL Rd Rotate Left Through Carry Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7)Z,C,N,V1 ROR Rd Rotate Right Through Carry Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0)Z,C,N,V1 ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6Z,C,N,V1 SWAP Rd Swap Nibbles Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)None1 BSET s Flag Set SREG(s) ← 1SREG(s)1 BCLR s Flag Clear SREG(s) ← 0 SREG(s)1 BST Rr, b Bit Store from Register to T T ← Rr(b)T1 BLD Rd, b Bit load from T to Register Rd(b) ← T None1 SEC Set Carry C ←1C1 CLC Clear Carry C ← 0 C1 SEN Set Negative Flag N ← 1N1 CLN Clear Negative Flag N ← 0 N1 SEZ Set Zero Flag Z ←1Z1 CLZ Clear Zero Flag Z ← 0 Z1 SEI Global Interrupt Enable I ←1I1 CLI Global Interrupt Disable I ← 0 I1 SES Set Signed T est Flag S ←1S1 CLS Clear Signed T est Flag S ← 0 S1 SEV Set T wos Complement Overflow V ←1V1 CLV Clear T wos Complement Overflow V ← 0 V1 SET Set T in SREG T ←1T1 CLT Clear T in SREG T ← 0 T1 SEH Set Half Carry Flag in SREG H ←1H1 CLH Clear Half Carry Flag in SREG H ← 0 H1 NOP No Operation None1 SLEEP Sleep(see specific descr. for Sleep function)None3 WDR Watch Dog Reset(see specific descr. for WDR/timer)None1Note:1.Order A T90S1200A-XXX for devices with the RCEN fuse programmed.Ordering Information (1)Speed (MHz)Power Supply Ordering Code Package Operation Range 42.7 - 6.0VA T90S1200-4PC A T90S1200-4SC A T90S1200-4YC 20P320S 20Y Commercial (0°C to 70°C)A T90S1200-4PI A T90S1200-4SI A T90S1200-4YI20P320S 20Y Industrial (-40°C to 85°C)124.0 - 6.0VA T90S1200-12PC A T90S1200-12SC A T90S1200-12YC 20P320S 20Y Commercial (0°C to 70°C)A T90S1200-12PI A T90S1200-12SI A T90S1200-12YI20P320S 20YIndustrial (-40°C to 85°C)Package Type20P320-lead, 0.300" Wide Plastic Dual Inline Package (PDIP)20S 20-lead, 0.300" Wide, Plastic Gull-Wing Small Outline (SOIC)20Y20-lead, 5.3 mm Wide, Plastic Shrink Small Outline Package (SSOP)Packaging Information© Atmel Corporation 1999.Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard war-ranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual prop-erty of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel HeadquartersAtmel OperationsCorporate Headquarters2325 Orchard Parkway San Jose, CA 95131TEL (408) 441-0311FAX (408) 487-2600EuropeAtmel U.K., Ltd.Coliseum Business Centre Riverside WayCamberley, Surrey GU15 3YL EnglandTEL (44) 1276-686-677FAX (44) 1276-686-697AsiaAtmel Asia, Ltd.Room 1219Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong KongTEL (852) 2721-9778FAX (852) 2722-1369JapanAtmel Japan K.K.9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTEL (81) 3-3523-3551FAX (81) 3-3523-7581Atmel Colorado Springs1150 E. Cheyenne Mtn. Blvd.Colorado Springs, CO 80906TEL (719) 576-3300FAX (719) 540-1759Atmel RoussetZone Industrielle13106 Rousset Cedex FranceTEL (33) 4-4253-6000FAX (33) 4-4253-6001Fax-on-DemandNorth America:1-(800) 292-8635International:1-(408) 441-0732e-mail********************Web Site BBS1-(408) 436-4309Marks bearing ® and/or ™ are registered trademarks and trademarks of Atmel Corporation.。

Features•High Performance, Low Power AVR® 8-Bit Microcontroller •Advanced RISC Architecture–120 Powerful Instructions – Most Single Clock Cycle Execution –32 x 8 General Purpose Working Registers–Fully Static Operation•Non-volatile Program and Data Memories–2/4/8K Bytes of In-System Programmable Program Memory Flash•Endurance: 10,000 Write/Erase Cycles–128/256/512 Bytes In-System Programmable EEPROM•Endurance: 100,000 Write/Erase Cycles–128/256/512 Bytes Internal SRAM–Programming Lock for Self-Programming Flash Program and EEPROM Data Security•Peripheral Features–8-bit Timer/Counter with Prescaler and Two PWM Channels–8-bit High Speed Timer/Counter with Separate Prescaler•2 High Frequency PWM Outputs with Separate Output Compare Registers•Programmable Dead Time Generator–USI – Universal Serial Interface with Start Condition Detector–10-bit ADC•4 Single Ended Channels•2 Differential ADC Channel Pairs with Programmable Gain (1x, 20x)•Temperature Measurement–Programmable Watchdog Timer with Separate On-chip Oscillator–On-chip Analog Comparator•Special Microcontroller Features–debugWIRE On-chip Debug System–In-System Programmable via SPI Port–External and Internal Interrupt Sources–Low Power Idle, ADC Noise Reduction, and Power-down Modes–Enhanced Power-on Reset Circuit–Programmable Brown-out Detection Circuit–Internal Calibrated Oscillator•I/O and Packages–Six Programmable I/O Lines–8-pin PDIP, 8-pin SOIC, 20-pad QFN/MLF, and 8-pin TSSOP (only ATtiny45/V)•Operating Voltage–1.8 - 5.5V for ATtiny25V/45V/85V–2.7 - 5.5V for ATtiny25/45/85•Speed Grade–ATtiny25V/45V/85V: 0 – 4 MHz @ 1.8 - 5.5V, 0 - 10 MHz @ 2.7 - 5.5V–ATtiny25/45/85: 0 – 10 MHz @ 2.7 - 5.5V, 0 - 20 MHz @ 4.5 - 5.5V•Industrial Temperature Range•Low Power Consumption–Active Mode:•1 MHz, 1.8V: 300 µA–Power-down Mode:•0.1 µA at 1.8V 8-bit Microcontrollerwith 2/4/8KBytes In-System ProgrammableATtiny25/VATtiny45/VATtiny85/V22586N–AVR–04/11ATtiny25/45/851.Pin ConfigurationsFigure 1-1.Pinout ATtiny25/45/851.1Pin Descriptions1.1.1VCCSupply voltage.1.1.2GNDGround.1.1.3Port B (PB5:PB0)Port B is a 6-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up32586N–AVR–04/11ATtiny25/45/85resistors are activated. The Port B pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port B also serves the functions of various special features of the ATtiny25/45/85 as listed in “Alternate Functions of Port B” on page 62.On ATtiny25, the programmable I/O ports PB3 and PB4 (pins 2 and 3) are exchanged in ATtiny15 Compatibility Mode for supporting the backward compatibility with ATtiny15.1.1.4Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running and provided the reset pin has not been disabled. The min-imum pulse length is given in Table 21-4 on page 170. Shorter pulses are not guaranteed to generate a reset.The reset pin can also be used as a (weak) I/O pin.42586N–AVR–04/11ATtiny25/45/852.OverviewThe ATtiny25/45/85 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny25/45/85achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.2.1Block DiagramFigure 2-1.Block DiagramThe AVR core combines a rich instruction set with 32 general purpose working registers. All 32registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent52586N–AVR–04/11ATtiny25/45/85registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than con-ventional CISC microcontrollers.The ATtiny25/45/85 provides the following features: 2/4/8K bytes of In-System Programmable Flash, 128/256/512 bytes EEPROM, 128/256/256 bytes SRAM, 6 general purpose I/O lines, 32general purpose working registers, one 8-bit Timer/Counter with compare modes, one 8-bit high speed Timer/Counter, Universal Serial Interface, Internal and External Interrupts, a 4-channel,10-bit ADC, a programmable Watchdog Timer with internal Oscillator, and three software select-able power saving modes. Idle mode stops the CPU while allowing the SRAM, Timer/Counter,ADC, Analog Comparator, and Interrupt system to continue functioning. Power-down mode saves the register contents, disabling all chip functions until the next Interrupt or Hardware Reset. ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions.The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip ISP Flash allows the Program memory to be re-programmed In-System through an SPI serial interface, by a conventional non-volatile memory programmer or by an On-chip boot code running on the AVR core.The ATtiny25/45/85 AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators and Evaluation kits.62586N–AVR–04/11ATtiny25/45/853.About3.1ResourcesA comprehensive set of development tools, application notes and datasheets are available for download on /avr.3.2Code ExamplesThis documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documen-tation for more details.For I/O Registers located in the extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI”instructions must be replaced with instructions that allow access to extended I/O. Typically, this means “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. Note that not all AVR devices include an extended I/O map.3.3Capacitive Touch SensingAtmel QTouch Library provides a simple to use solution for touch sensitive interfaces on Atmel AVR microcontrollers. The QTouch Library includes support for QTouch ® and QMatrix ® acquisi-tion methods.Touch sensing is easily added to any application by linking the QTouch Library and using the Application Programming Interface (API) of the library to define the touch channels and sensors.The application then calls the API to retrieve channel information and determine the state of the touch sensor.The QTouch Library is free and can be downloaded from the Atmel website. For more informa-tion and details of implementation, refer to the QTouch Library User Guide – also available from the Atmel website.3.4Data RetentionReliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.72586N–AVR–04/11ATtiny25/45/854.AVR CPU Core4.1IntroductionThis section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories,perform calculations, control peripherals, and handle interrupts.4.2Architectural OverviewFigure 4-1.Block Diagram of the AVR ArchitectureIn order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the Program memory are executed with a single level pipelining. While one instruction is being executed, the next instruc-tion is pre-fetched from the Program memory. This concept enables instructions to be executed in every clock cycle. The Program memory is In-System Reprogrammable Flash memory.82586N–AVR–04/11ATtiny25/45/85The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typ-ical ALU operation, two operands are output from the Register File, the operation is executed,and the result is stored back in the Register File – in one clock cycle.Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash Program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic opera-tion, the Status Register is updated to reflect information about the result of the operation.Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word for-mat, but there are also 32-bit instructions.During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the Reset routine (before subroutines or interrupts are executed). The Stack Pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.The memory spaces in the AVR architecture are all linear and regular memory maps.A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector posi-tion. The lower the Interrupt Vector address, the higher the priority.The I/O memory space contains 64 addresses for CPU peripheral functions as Control Regis-ters, SPI, and other I/O functions. The I/O memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F.4.3ALU – Arithmetic Logic UnitThe high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the “Instruction Set” section for a detailed description.4.4Status RegisterThe Status Register contains information about the result of the most recently executed arithme-tic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.92586N–AVR–04/11ATtiny25/45/854.4.1SREG – AVR Status RegisterThe AVR Status Register – SREG – is defined as:•Bit 7 – I: Global Interrupt EnableThe Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual inter-rupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.•Bit 6 – T: Bit Copy StorageThe Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or desti-nation for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.•Bit 5 – H: Half Carry FlagThe Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry is useful in BCD arithmetic. See the “Instruction Set Description” for detailed information.•Bit 4 – S: Sign Bit, S = N ⊕ VThe S-bit is always an exclusive or between the Negative Flag N and the Two’s Complement Overflow Flag V. See the “Instruction Set Description” for detailed information.•Bit 3 – V: Two’s Complement Overflow FlagThe Two’s Complement Overflow Flag V supports two’s complement arithmetics. See the “Instruction Set Description” for detailed information.•Bit 2 – N: Negative FlagThe Negative Flag N indicates a negative result in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information.•Bit 1 – Z: Zero FlagThe Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information.•Bit 0 – C: Carry FlagThe Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information.Bit 765432100x3F I T H S V N Z C SREGRead/Write R/W R/W R/W R/W R/W R/W R/W R/W Initial Value102586N–AVR–04/11ATtiny25/45/854.5General Purpose Register FileThe Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are supported by the Register File:•One 8-bit output operand and one 8-bit result input •Two 8-bit output operands and one 8-bit result input •Two 8-bit output operands and one 16-bit result input •One 16-bit output operand and one 16-bit result inputFigure 4-2 shows the structure of the 32 general purpose working registers in the CPU.Figure 4-2.AVR CPU General Purpose Working RegistersMost of the instructions operating on the Register File have direct access to all registers, and most of them are single cycle instructions.As shown in Figure 4-2, each register is also assigned a Data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically imple-mented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-pointer registers can be set to index any register in the file.4.5.1The X-register, Y-register, and Z-registerThe registers R26..R31 have some added functions to their general purpose usage. These reg-isters are 16-bit address pointers for indirect addressing of the data space. The three indirect address registers X, Y, and Z are defined as described in Figure 4-3.7Addr.R0 0x00R10x01R20x02…R130x0D General R140x0E Purpose R150x0F Working R160x10RegistersR170x11…R260x1A X-register Low Byte R270x1B X-register High Byte R280x1C Y-register Low Byte R290x1D Y-register High Byte R300x1E Z-register Low Byte R310x1FZ-register High Byte分销商库存信息:ATMELATTINY85-20MUR ATTINY85V-10MUR ATTINY85-20SH ATTINY85V-10SH ATTINY85-20SUR ATTINY85-20MU ATTINY85V-10SUR ATTINY85V-10MU。

DATASHEETOverview IC Compiler™ II is the industry leading place and route solution that delivers best-in-class quality-of-results (QoR) for next-generation designs across all market verticals and process technologies while enabling unprecedented productivity. IC Compiler II includes innovative for flat and hierarchical design planning, early design exploration, congestion aware placement and optimization, clock tree synthesis, advanced node routing convergence, manufacturing compliance, and signoff closure.IC Compiler II is specifically architected to address aggressive performance, power, area (PPA), and time-to-market pressures of leading-edge designs. Key technologies include a pervasively parallel optimization framework, multi-objective global placement, routing driven placement optimization, full flow Arc based concurrent clock and data optimization, total power optimization, multi-pattern and FinFET aware flow and machine learning (ML) driven optimization for fast and predictive design closure. Advanced Fusion technologies offer signoff IR drop driven optimization, PrimeTime ® delay calculation within IC Compiler II, exhaustive path-based analysis (PBA) and signoff ECO within place and route for unmatched QoR and design convergence. F U S I O N D E S I G N P L A T F O R M PrimeTime, StarRC, PrimePower,IC Validator, RedHawk Analysis Fusion Fusion Compiler IC Compiler II Design Compiler NXT TestMAX F o r m a l i t y ECO Fusion S i g n o f f F u s i o n S i g n o f f F u s i o n Test Fusion Figure 1: IC Compiler II Anchor in Synopsys Design PlatformAccelerating DesignClosure on AdvancedDesignsIC Compiler II Industry Leading Place and Route SystemKey BenefitsProductivity• The highest capacity solution that supports 500M+ instances with a scalable and compact data model• A full suite of design planning features including transparent hierarchical optimization• Out-of-the-box simple reference methodology for easy setup• Multi-threaded and distributed computing for all major flow steps• Golden signoff accuracy with direct access to PrimeTime delay calculationPPA• Unified TNS driven optimization framework• Congestion, timing, and power-driven logic re-synthesis• IEEE 1801 UPF/multi-voltage support• Arc-based concurrent clock and data optimization• Global minima driven total power optimizationAdvanced Nodes• Multi-pattern and FinFET aware design flow• Next generation advanced 2D placement and legalization• Routing layer driven optimization, auto NDR, and via pillar optimization• Machine learning driven congestion prediction and DRC closure• Highest level of foundry support and certification for advanced process nodes• IC Validator in the loop signoff driven DRC validation and fixingAdvanced Fusion Technology• Physically aware logic re-synthesis• IR drop driven optimization during all major flow steps• PrimeTime delay calculation based routing optimization for golden accuracy• Integrated PrimeTime ECO flow during routing optimization for fastest turnaround timeEmpowering Design Across Diversified ApplicationsThe dizzying pace of innovation and highly diversified applications across the design spectrum is forcing a complete rethink of the place and route systems to design and implement differentiated designs in a highly competitive semiconductor market on schedule. Designers on emerging process nodes must meet aggressive PPA and productivity goals. It essentially means efficient and intelligent handling of 100s of millions of place-able instances, multiple levels of hierarchy, 1000s of hard macros, 100s of clocks, wide busses, and 10s of modes and corners power domains and complex design constraints and process technology mandates. Emphasis on Designer ProductivityIC Compiler II is architected from the ground up for speed and scalability. Its hierarchical data model consumes 2-3X less memory than conventional tools, boosting the limits of capacity to 500M placeable instances and beyond. Adaptive abstraction and on-the-fly data management minimize memory requirements and enable fast responsive data manipulation. Near-linear multi-core threading of key infrastructural components and core algorithms such as database access and timing analysis speed up optimization at all phases of design. Patented, lossless compact modeling and independent R and C extraction allow handling more modes and corners (MCMM scenarios) with minimal runtime impact.IC Compiler II has built-in Reference Methodology(RM) that ensures fast flow bring up. This RM Flow is Foundry Process/Design Type specific to ensure a robust starting point and seamless bring up. IC Compiler II has direct access to the Golden PrimeTime delay calculation engine to minimize ECO iterations.IC Compiler II’s new data model enables designers to perform fast exploration and floorplanning with complex layout requirements. IC Compiler II can create bus structures, handle designs with n-levels of physical hierarchy, and support Multiply Instantiated Blocks (MIBs) in addition to global route driven pin assignment/feedthrough flow, timing driven macro placement, MV area design planning.A design data mismatch inferencing engine analyzes the quality of inputs and drives construct creation on the fly, delivering design insights even with “incomplete” data early in the design cycle. Concurrent traversal of logical and physical data models enables hierarchical Data-Flow Analysis (DFA) and fast interactive analysis through multi-level design hierarchies and MIBs. Data flow and feedthrough paths highlighted in Figure 2 allow analysis and manipulation through n-levels of hierarchy to complete early design exploration and prototyping.Figure 2: Fast interactive analysis through multiple-levels of physical hierarchy and MIBPipeline-register-planning shown in Figure 3, provides guidance for optimal placement to meet the stringent timing requirementsof high-performance designs. Interactive route editor integrated which is advanced node aware shown in Figure 4, allows intricate editing and routing functions, including the creation of special signal routes, buses, etc.Figure 3: Pipeline register placement enables superior QoR for designs with complex busesAchieving Best Performance, Power, Area, and TATIC Compiler II features a new optimization framework built on global analytics. This Unified TNS Driven Optimization framework is shared with Design Compiler NXT synthesis to enable physically-aware synthesis, layer assignment, and route-based optimization for improved PPA and TAT. Multi-Corner Multi-Mode (MCMM) and Multi-Voltage (MV) aware, level-based analytical algorithms continuously optimize using parallel heuristic algorithms. Multi-factor costing functions deliver faster results on both broad and targeted design goals. Concurrent PPA driven logic remapping, rewiring, and legalization interleaved with placement minimizes congested logic, resulting in simple localized logic cones that maximize routability and QoR.IC Compiler II minimizes leakage with fast and efficient cell-by-cell power selection across HVT, SVT and LVT cells and varying channel lengths. Activity-driven power optimization uses VCD/ SAIF, net toggle rates, or probability functions to drive placement decisions and minimize pin capacitances. Multi-bit register banking optimizes clock tree structures, reduces area, and net length, while automatically managing clock, data, and scan chain connections.Advanced modeling of congestion across all layers highlighted in Figure 4 provides accurate feedback throughput the flow from design planning to post- route optimization.Figure 4: Intelligent and accurate analysis for congestion and powerIC Compiler II introduces a new Concurrent Clock and Data (CCD) analysis and optimization engine that is built-in to every flow step resulting in meeting both aggressive performance and minimizing total power footprint. ARC-based CCD optimization performs clock tree traversal across all modes/corners in path-based fashion to ensure optimal delay budgeting.Robust support for clock distribution enables virtually any clock style, including mesh, multi-source, or H-tree topologies. Advanced analysis and debugging features perform accurate clock QoR analysis and debugging as highlighted in Figure 5.Figure 5: Accurate clock QoR analysis and debugging (a & b) Abstracted clock graph and schematic.(c) Latency clock graph. (d) Colored clock tree in layout.IC Compiler II features many innovative technologies that make it the ideal choice for high-performance, energy-efficient Arm®processor core implementation, resulting in industry-best milliwatts/megahertz (mW/MHz) for mobile and other applications across the board. Synopsys and Arm work closely together to offer optimized implementation of popular Arm cores for IC Compiler II,with reference flows available for Arm Cortex®-A high-performance processors and Mali GPUs. In addition, Arm offers off-the-shelf Artisan® standard cell and memory models that have been optimally tuned and tested for fast deployment in an IC Compiler II environment. Continuous technology innovation and close collaboration makes IC Compiler II the leading choice for Arm-based high- performance design.Highest Level of Advanced Node Certification and SupportIC Compiler II provides advanced node design enablement across major foundries and technology nodes—including 16/14nm,12/10nm, 7/5nm, and sub-5nm geometries. Zroute digital router technology ensures early and full compliance with the latest design rules required for these advanced node technologies. Synopsys collaborates closely with all the leading foundries to ensure that IC Compiler II is the first to deliver support for early prototype design rules and support for the final production design rules. IC Compiler II design technologies maximize the benefits of new process technologies and offer optimal return on investment for cutting-edge silicon applications.IC Compiler II advanced node design support includes multi-pattern/FinFET aware placement and routing, Next-generation advanced 2D placement and legalization, routing layer driven optimization, auto NDR, and via pillar optimization. IC Validator in the loop provides signoff DRC feedback during Implementation.Foundry fill Track based fillFigure 6: IC Validator In-Design metal fill color aware metal fill, optimized for density and foundry requirementsMachine learning driven congestion prediction and DRC closure allow for fastest routing convergence with best PPA. Multiple sets of training data are used to extract key predictive elements that guide the pre-route flow.Advanced Fusion TechnologyThe Fusion Design Platform™ delivers unprecedented full-flow QoR and time-to-results (TTR) to accelerate the next wave of semiconductor industry innovation. The industry’s first AI-enhanced, cloud-ready Design Platform with Fusion Technology™ isbuilt from Synopsys’ market-leading, massively-parallel digital design tools, and augmented with innovative capabilities to tacklethe escalating challenges in cloud computing, automotive, mobile, and IoT market segments and accelerate the next wave of industry innovation.Fusion Technology redefines conventional EDA tool boundaries across synthesis, place-and-route, and signoff, sharing integrated engines across the industry’s premier digital design products. It enables designers to accelerate the delivery of their next-generation designs with the industry-best QoR and the TTR.©2019 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.。

英语演讲稿结束语(精选多篇)第一篇:英语口语结束语为了提高英语教师的口语交际能力,更好地开展英语教学工作,于11月3日下午,在李台镇中心小学综合楼多媒体教室,举行了“英语教师口语大赛”。

比赛内容由自己选材,题材不限。

来自我们学校的六名英语教师同台竞技,都展示出不俗的口语表达能力。

老师们的表演十分精彩:有引人入胜的英语故事,有鼓舞人心的奥运演讲、旋律优美的英语歌曲等。

经过紧张的角逐,最终xxx老师以标准、流畅的口语获得了第一名。

本次比赛为英语教师提供了一个展示英语口语的舞台。

通过比赛,老师们觉得受益匪浅,进一步提高了我校英语教师的口语水平。

第二篇:演讲稿结束语的技巧演讲结束语最常用的方式,就是用极其精练的语言,总结收拢全篇的主要内容,概括和强化主题思想。

这种结尾,扼要地总结演讲内容,能起到提醒、强调的作用,给听众留下完整的总体印象。

除非演讲非常简短,否则建议你在结尾中清晰陈述你的主题和主要思想。

演讲者在演讲中,为了阐述自己的观点和主张,往往利用一切手段,从正面、反面和侧面等各个方面来进行分析和论证。

到了结尾处,就应总结全篇,突出重点,深化主题。

这不仅能帮助健忘的听众回忆前面所讲的内容,而且也能画龙点睛,给听众留下完整而深刻的印象,使整个演讲显得结构严谨,首尾呼应,通篇浑然一体。

第三篇:英语演讲的秘诀:开场白、结束语以下是我收集到的关于英语演讲稿的开场白和介绍语:应对问题-iwillbepleasedtoansweranyquestionsyoumayhaveattheendofthepres entation.-pleasecanyousaveyourquestionstilltheend.-ifyouhaveanyquestions,iwillbepleasedtoanswerthemattheendofthe presentation.-therewillbetimeattheendofthepresentationtoansweryourquestions -sopleasefeelfreetoaskmeanythingthen.-don'thesitatetointerruptifyouhaveaquestion.-pleasefeelfreetointerruptmeatanytime.-pleasestopmeifyouhaveanyquestions.-ifyouneedclarificationonanypoint,you'rewelcometoaskquestionsa tanytime.-canicomebacktothatpointlater?-iwillbecomingtothatpointinaminute.-that'satrickyquestion.-wewillgointodetailslater.butjusttogiveyouanideaof...-iamafraidthere'snoeasyanswertothatone...-yes,that'saverygoodpoint.-perhapswecouldleavethatpointuntilthequestionsattheendofthepre sentation-ithinkisaidthatiwouldanswerquestionsattheendofthepresentation ---perhapsyouwouldn'tmindwaitinguntilthen.-ithinkwehavetimeforjustonemorequestion欢迎听众(正式)-welcometoourcompany-iampleasedtobeabletowelcomeyoutoourcompany...-i'dliketothankyouforcoming.-mayitakethisopportunityofthankingyouforcoming欢迎听众(非正式)-i'mgladyoucouldallgethere...-i'mgladtoseesomanypeoplehere.-it'sgreattobebackhere.-helloagaineverybody.thankyouforbeingontime/makingtheefforttoc ometoday.-welcometoxpartii.受邀请在会议上致词-iamdelighted/pleased/gladtohavetheopportunitytopresent/ofmaki ngthispresentation...-iamgratefulfortheopportunitytopresent...-i'dliketothankyouforinviting/askingme/givingmethechanceto...-goodmorning/afternoon/eveningladiesandgentleman-it'smypleasantdutytodayto...-i'vebeenaskedto...告知演讲的话题-thesubjectofmypresentationis...-ishallbespeakingtodayabout...-mypresentationconcerns...-today'stopicis...-todayweareheretogiveapresentationon...-todayweareheretotalkabout...beforewestart,i'dlikeyoumeetmytea mmembers...-abrieflookattoday'sagenda...(告诉听众所讲内容的先后顺序) -beforewestartourpresentation,let'stakeabrieflookattheagenda...-ishallbeofferingabriefanalysisof...-themainareathatiintendtocoverinthispresentationis...-takeamomentandthinkof...-thankyouforgivingmetheopportunitytotellyouabout...告诉听众发言的长度-duringthenexttenminutes,ishall...-ishallbespeakingforabouttenminutes...-mypresentationwilllastforabouttenminutes...-iwon'ttakeupmorethantenminutesofyourtime...-idon'tintendtospeakforlongerthantenminutes...-iknowthattimeisshort,soiintendtokeepthisbrief-ihavealottocramintothenexttenminutes,soi'dbettermakeastart...引起听众的兴趣-i'mgoingtobespeakingaboutsomethingthatisvitallyimportanttoall ofus.-mypresentationwillhelpsolveaproblemthathaspuzzledpeopleforyea rs...-attheendofthispresentationyouwillunderstandwhythiscompanyhasb eensosuccessfulforsolong...-iamgoingtobetalkingaboutaproductthatcoulddoubleyourprofitmarg ins...-thenexttenminuteswillchangeyourattitudetosalesandmarketing...-overthenexttenminutesyouaregoingtohearaboutsomethingthatwillc hangethewayyourcompaniesoperate...-bytheendofthispresentationyouwillknowallthereistoknowabout...告诉听众内容要点-therearefivemainaspectstothistopic(...thefirst,...thesecond,. ..athird,...another,...thefinal)-iamgoingtoexaminethesetopicsinthefollowingorder(...first,...n ext,...afterthat,...finally)-i'vedividedmytalkintofiveparts...-iwilldealwiththesetopicsinchronologicalorder...-i'mgoingtostartwithageneraloverviewandthenfocusonthisparticul arproblem(...ingeneral,...moreparticularly).-iwanttostartwiththisparticulartopic,andthendrawsomemoregenera lconclusionsfromit(...specifically,...inawidercontext).-thereare(anumberof)factorsthatmayaffect...-wehavetotakeintoaccountinanydiscussionofthissubject,thefollow ingconsiderations.-wealloughttobeawareofthefollowingpoints.结束语-inconclusion,i'dliketo...-i'dliketofinishby...-finally...-bywayofconclusion...-ihopeihavemademyselfunderstood-ihopeyouhavefoundthisuseful-ihopethishasgivenyousomeidea/clearidea/anoutlineof...-letmeendbysaying...-that,thenwasallihadtosayon...-thatconcludesourpresentation...-ihopei'vemanagedtogiveyouaclearerpictureof...-ifthereareanyquestions,i'dbedelightedto...-thankyouforyourattention...-let'sbreakforacoffeeatthispoint-iamafraidthattheclockisagainstus,sowehadbetterstophere -youhavebeenaveryattentiveaudience---thankyou希望对你有所帮助。

3HE 11984 AAAB TQZZA Edition 01July 2017Documentation Suite Overview7450 ESS, 7750 SR, and 7950 XRS Release 15.0IntroductionThis document provides information about the Service Router Operating System (SR OS) user guides that are available for the 7450 ESS, 7750 SR, 7950 XRS, and the VSR including information about: •Service Router portfolio platforms•Software documents in this documentation suite•Hardware and other documents in this documentation suite •Accessing and searching the Documentation Center•Searching for specific information in a document or in multiple documents •Contact informationService router platforms covered in this documentation suiteNo32237750 SR-a47750 SR-a87750 Service Router (SR)7450 Ethernet Service Switch (ESS)7750 SR-c47750 SR-77750 SR-127750 SR-12e 7750 SR-c127750 SR-1e 7750 SR-2e 7750 SR-3e7450 ESS-77450 ESS-12Software documents in this documentation suiteThe following table lists and describes the software documents in this documentation suite and the intended audience for each guide. The suite covers the SR OS software functionality for the 7450 ESS, 7750 SR, 7950 XRS, and VSR platforms.The guides are organized into functional chapters and provide concepts and descriptions of the implementation flow, as well as Command Line Interface (CLI) syntax and command usage.Intended audience legend:•A —Network architects and designers•B —Installers and hardware maintenance technicians•C —Network technicians, administrators, operators, and service providersSoftware Guides DocumentDescriptionIntended Audience AB C Acronym GuideThis guide provides expansions of acronyms found in the user guides.✓✓✓Advanced Configuration GuideThis guide provides advanced configuration solutions and is a supplement to the other guides in this suite.✓✓✓Basic SystemConfiguration GuideThis guide describes CLI usage, file system management, and boot option file (BOF)configuration, as well as how to configure basic system management, node timing, and synchronization functions.✓✓✓Gx AVPs Reference Guide (for 7750 SR)This guide describes Gx Attribute Value Pairs (AVPs).✓—✓Interface Configuration GuideThis guide describes how to provision Input/Output Modules (IOMs), XMA Control Modules (XCMs), Media Dependent Adapters (MDAs), XRS Media Adapters (XMAs), and ports.✓—✓7950 XRS-16c7950 XRS-207950 XRS-407950 eXtensible Routing System (XRS)Layer 2 Services and EVPN Guide: VLL, VPLS, PBB, and EVPNThis guide describes Layer 2 service and Ethernet Virtual Private Network (EVPN) functionality and provides examples to configure and implement Virtual Leased Lines (VLLs), Virtual Private LAN Service (VPLS), Provider Backbone Bridging (PBB), and EVPN.✓—✓Layer 3 Services Guide: Internet Enhanced Services and Virtual Private Routed Network Services This guide describes Layer 3 service functionality and provides examples to configure and implement Internet Enhanced Services (IES) and Virtual Private Routed Network (VPRN) services.✓—✓MPLS GuideThis guide describes how to configure Multiprotocol Label Switching (MPLS), Resource Reservation Protocol (RSVP), Generalized Multiprotocol Label Switching (GMPLS), and Label Distribution Protocol (LDP).✓—✓Multicast Routing Protocols GuideThis guide provides an overview of multicast routing concepts and provides configuration examples for Internet Group Management Protocol (IGMP), Multicast Listener Discovery (MLD), Protocol Independent Multicast (PIM), Multicast SourceDiscovery Protocol (MSDP), Multipoint LDP , multicast extensions to BGP , and Multicast Connection Admission Control (MCAC).✓—✓Multiservice Integrated Service Adapter Guide (for the 7450 ESS, 7750 SR and VSR)This guide describes services provided by integrated service adapters, such as Application Assurance, IPSec, ad insertion (ADI), and Network Address Translation (NAT).✓—✓OAM and Diagnostics GuideThis guide describes how to configure features such as service mirroring and Lawful Intercept (LI), and how to use the Operations, Administration and Management (OAM) and diagnostics tools.✓—✓Log Events Guide This guide provides general information about log events.✓✓✓Quality of Service Guide This guide describes how to configure Quality of Service (QoS) policy management.✓—✓RADIUS AttributesReference Guide (for the 7750 SR and VSR)This guide describes all supported RADIUS Authentication, Authorization, and Accounting attributes.✓—✓Router Configuration GuideThis guide describes logical IP routing interfaces and associated attributes such as IP addresses, as well as IP and MAC-based filtering, Virtual Router Redundancy Protocol (VRRP), and Cflowd.✓—✓Software Guides (Continued)DocumentDescriptionIntended Audience AB CHardware documents in this documentation suiteThe intended audience for the hardware documents in this documentation suite are network architects and designers, installers, and hardware maintenance technicians.7450 ESS guides•7450 ESS SONET/SDH OC-3C/STM-1C MDA Installation Guide•7450 ESS SONET/SDH OC-12C/STM-4C MDA Installation Guide•7450 ESS SONET/SDH OC-48C/STM-16C MDA Installation Guide7750 SR guides•7710 and 7750 SR Channelized DS1/E1 CMA Installation Guide•7750 SR-1e,-2e and -3e Chassis Installation Guide•7750 SR-12e Installation Guide•7750 SR-c4 Installation Guide•7750 SR-c12 Installation Guide•7750 SR-a4 and 7750 SR-a8 Installation Guide•7750 SR ATM MDA Installation Guide•7750 SR Channelized Any Service Any Port (ASAP) MDA Installation Guide•7750 SR Product Family Channelized OC3/OC12/STM-1 Circuit Emulation Services (CES) CMA/MDA Installation Guide•7750 SR SONET/SDH OC-3C/STM-1C MDA Installation Guide•7750 SR SONET/SDH OC-12C/STM-4C MDA Installation Guide•7750 SR SONET/SDH OC-48c/STM-16c MDA Installation Guide •Vertical Rack Mount Kit Installation Guide•Virtualized Service Router Installation and Setup Guide•7750 SR Channelized Any Service Any Port (ASAP) MDA Installation Guide7450 ESS and 7750 SR guides•7450 ESS and 7750 SR IOM4-e Installation Guide•7450 ESS and 7750 SR MDA-e Installation Guide•7450 ESS-7 and 7750 SR-7 Chassis Installation Guide•7450 ESS-12 and 7750 SR-12 Chassis Installation Guide•7750 SR and 7450 ESS HS-MDA2 Installation Guide•7750 SR and 7450 ESS Integrated Media Module Installation Guide•7750 SR and 7450 ESS Multiservice Integrated Service Adapter Installation Guide•7750 SR and 7450 ESS SF/CPM to SF/CPM5 Hardware Upgrade Guide•7x50 10 Gigabit Ethernet Tunable DWDM MDA Installation Guide•7x50 High Scale (HS) MDA Installation Guide•7x50 MDA-XP Installation Guide•7750 SR and 7450 ESS Integrated Service Adapter Video Installation Guide•7750 SR-7 and 7450 ESS-7 PEM-3 Upgrade Installation Note•7750 SR-12 and 7450 ESS-12 PEM-3 Upgrade Installation Note•7450 ESS and 7750 SR Troubleshooting Guide7950 XRS guides•7950 XRS-16c Chassis Installation Guide•7950 XRS-20 and 7950 XRS-40 Chassis Installation GuideOther documents in this documentation suite•Documentation Suite Overview Service Router Portfolio, Release 15.0 (this document)•SR OS AA Protocols and Applications (spreadsheet)•SR OS Software Release NotesUsing the Documentation CenterUse the following procedure to access any of the guides mentioned in this document or to access azipped file of the complete set of software guides:1.Open a browser and navigate to:Customer Documentation Welcome PageThe Documentation Center appears. By default, the products are listed by the most accessed.2.Click on 7750 SR, 7450 ESS, 7950 XRS, or VSR in the list. The documentation web page for thatproduct appears. The most recent documents are listed by default.3.The different search and sorting options on the documentation web page allow you to:•filter or sort the documents•search for documents by specific title words or document numbers•search for specific text in documents (Full Text search)Notes:• A Full Text search searches for text in PDF files only.•To search for phrases in a Full Text search, type the phrase within quotation marks; forexample, “synchronous Ethernet”.•To remove the search filter or sorting options, click Reset.4.Select a document by clicking the associated icon on the right:•PDF icon•HTML icon•Zip Collection iconNote: If the document is restricted, a key is displayed beside the document number, indicating thatyou must log in and enter your user name and password. If you cannot access the document afterlogging in, your account does not have permission to access the document. Contact your Nokiatechnical support representative.If you do not have a user name and password, you can request one from the Documentation Centerweb page. A link is also available to provide feedback about the web page.Searching for specific information in a document or in multiple documentsYou can use Adobe Reader, Release 6.0 or later, to search one or more PDF files for a term.Note: The PDF files that you search must be in the same folder or sub folder.1.From the Adobe Reader main menu, choose Edit > Search or Advanced Search. The Searchpanel opens.•To search for a term in the current document, click on the In the current document radiobutton.•To search for a term in multiple documents, click on the All PDF Documents in radio buttonand choose the folder in which to search using the drop-down menu.2.Enter the term to search for. Select one or more of the following search criteria, if required:•Whole words only•Case-Sensitive•Include Bookmarks•Include Comments3.Click on the Search button. Adobe Reader displays the search results.You can expand the entries for each file by clicking on the + symbol.Documentation supportIf you have questions or comments about this documentation suite, contact:Customer Documentation FeedbackTechnical supportCustomer support representatives are available to assist you 24 hours a day, 7 days a week. For a listof regional contact telephone and fax numbers, see:Product Support PortalNokia is a registered trademark of Nokia Corporation. Other products and company names mentionedherein may be trademarks or tradenames of their respective owners. The information presented issubject to change without notice. No responsibility is assumed for inaccuracies contained herein.Copyright © 2017 Nokia.Services Overview Guide This guide provides a general overview offunctionality provided by the routers and describeshow to configure service parameters such as ServiceAccess Points (SAPs), Service Distribution Points(SDPs), customer information, and user services.✓—✓System Management Guide This guide describes system security features,SNMP and NETCONF features, and event andaccounting logs. It covers basic tasks such asconfiguring management access filters, passwords,and user profiles.✓✓✓Triple Play Service Delivery Architecture Guide (for the 7450 ESS, 7750 SR, and VSR)This guide describes the Triple Play Service DeliveryArchitecture (TPSDA) support and providesexamples to configure and implement variousprotocols and services.✓—✓Unicast Routing Protocols Guide This guide provides an overview of unicast routingconcepts and provides configuration examples forRouting Information Protocol (RIP), Open ShortestPath First (OSPF), Intermediate-system-to-intermediate-system (IS-IS), and Border GatewayProtocol (BGP) routing protocols, and for routepolicies.✓—✓Software Guides (Continued)Document Description IntendedAudienceA B C。

1Which one is the correct procedure of price negotiation? (1.0分)0.0 分A、offer--inquiry--counter--offer--acceptanceB、offer--counter-offer--refuse--acceptanceC、inquiry--offer--counter-offer--acceptanceD、inquiry--offer--refuse--acceptance正确答案: C 我的答案:B2Please put your _____ in upright position.(1.0分)1.0 分A、seat backB、trayC、deskD、chair正确答案: A 我的答案:A3How much do you _____ per night?(1.0分)1.0 分A、costB、charge正确答案: B 我的答案:B4The sign above means__________?(1.0分)1.0 分A、liftB、escalatorC、elevator正确答案: B 我的答案:B5Go through Fifth Avenue.Then take ____turning on the left/right.(1.0分)1.0 分A、the fiveB、fiveC、fifthD、the fifth正确答案: D 我的答案:D6The sign above means__________?(1.0分)1.0 分A、baggageB、baggage carC、luggage carD、baggage cart正确答案: D 我的答案:D7Which one could be the best way to give directions?(1.0分)1.0 分A、Try to be complicated.B、Try to be simple.C、Give lots of details.D、Give lots of road names.正确答案: B 我的答案:B8Now we’ll be serving drinks. Please pull down your ______ table. (1.0分)1.0 分A、littleB、trayC、deskD、front正确答案: B 我的答案:B9I'm afraid that I have to __________ my appointment.(1.0分)1.0 分A、giveB、cancelC、presentD、delete正确答案: B 我的答案:B10I am afraid that your baggage is ______.(1.0分)1.0 分A、overweightB、overweighted正确答案: A 我的答案:A11____ the road you can see the hospital.(1.0分)1.0 分A、by the end ofB、at the end ofC、in the endD、be at the end正确答案: B 我的答案:B12Which one has the same meaning as the word "bedrock price"? (1.0分)1.0 分A、the highest priceB、the lowest priceC、the proper priceD、the reduced price正确答案: B 我的答案:B13Which of the following expressions are demanding favorable terms of payment? (1.0分)0.0 分A、L/C at sight is what we require for all our customers.B、Would you please tell us the terms of payment?C、Now let's discuss the question of payment terms.D、I don't think it is the proper time for us to accept payment by D/P.正确答案: A 我的答案:B14We’ll sign two ____, each in the Chinese and English language.(1.0分)1.0 分A、originalsB、partsC、sectionsD、aspects正确答案: A 我的答案:A15Please fasten your _______?(1.0分)1.0 分A、beltB、ropeC、stringD、seat belt正确答案: D 我的答案:D16As about the branch names of a company, which expression is not correct?(1.0分)0.0 分A、Human Resources DepartmentB、Sales Promotion DepartmentC、Personal DepartmentD、General Accounting Department正确答案: C 我的答案:B17以下表述正确的是(1.0分)0.0 分A、Can I upgrade my seat?B、All the flights have been cancelled because the weather conditions.C、What change would you like to make?D、Do you want to return your tickets?正确答案: C 我的答案:A答案解析:18A: How would you like us to pack your products?B: Since there are glasses and fragile items, I think you'd better use _______.(1.0分)1.0 分A、bagsB、drumsC、casksD、wooden boxes正确答案: D 我的答案:D19I’d like to _______ further explanations about exchanging business cards at the first meeting.(1.0分)1.0 分A、addB、offeringC、askD、post正确答案: D 我的答案:D20Choose the most suitable expression(1.0分)1.0 分A、vacant 未被占用的B、family room 家庭房C、shutter bus 接送大巴D、breakfast coupon 早餐券正确答案: A 我的答案:A21The flavor of Sichuan cuisine is_______.(1.0分)1.0 分A、spicy and hotB、sweet and lightC、fresh and saltyD、numbing and sour正确答案: A 我的答案:A22Please reorder the following dishes as a standard western dinner.1.Main course2.Soup3.Coffee4.Starter(1.0分)1.0 分A、3421B、3142C、4123D、4213正确答案: D 我的答案:D23Which sign blow has the same meaning as the sign above? (1.0分)1.0 分A、B、C、D、正确答案: C 我的答案:C24Which does not belong to the eight great regional cuisine in China? (1.0分)1.0 分A、Sichuan cuisineB、Hunan cuisineC、Jiangxi cuisineD、Zhejiang cuisine正确答案: C 我的答案:C25Which of the following is not an available foreign currency?(1.0分)1.0 分A、francB、wonC、european dollarD、pound正确答案: A 我的答案:A26What items should be included in the presentation?(1.0分)1.0 分A、Number of the customerB、Competitive RivalsC、Final RiskD、Outline and Objective正确答案: D 我的答案:D27You can________relevant situation on well known enterprises.(1.0分)1.0 分A、knowB、getC、learnD、study正确答案: C 我的答案:C28I'm glad to have the _______ of meeting you in my hometown.(1.0分)1.0 分A、pleasureB、chanceC、reputationD、time正确答案: A 我的答案:A29The woolen sweaters you delivered do not _____ the sample we provided. (1.0分)1.0 分A、likeB、asC、matchD、fit正确答案: C 我的答案:C30Which is not one of the main types of hotel room offered to the conference attendees?(1.0分)0.0 分A、twin roomB、double roomC、family suiteD、business suite正确答案: C 我的答案:D31Choose the most suitable expression(1.0分)0.0 分A、铺床服务 bed serviceB、洗衣服务 laundry serviceC、细目 detailed listD、急件 urgent pack正确答案: B 我的答案:A32以下翻译正确的是(1.0分)0.0 分A、e -ticket 经济票B、full fare 全价票C、infant fair 折扣票D、cancellation 退票正确答案: B 我的答案:A答案解析:33When will the conference_______?(1.0分)1.0 分A、heldB、holdC、be heldD、holding正确答案: C 我的答案:C34In the business letter of _______ ,give background information from your personal experience.(1.0分)1.0 分A、tradeB、introductionC、negotiationD、company正确答案: B 我的答案:B35I'm sorry to say the shipment didn't turn to _________ (1.0分)0.0 分A、be satisfied.B、be satisfying.C、be satisfactory.D、be satisfiction.正确答案: C 我的答案:B36The goods you sent us are _______ _________ to the original sample. (1.0分)1.0 分A、inferior; comparedB、inferior; comparingC、bad; comparedD、bad; comparing正确答案: A 我的答案:A37I was just _____ by the airlines that my flight has been rescheduled.(1.0分)1.0 分A、askedB、expectedC、toldD、informed正确答案: D 我的答案:D38As a Chinese, how many customs should we go through when we go to Paris for travelling?(1.0分)0.0 分A、onceB、twiceC、thriceD、none正确答案: B 我的答案:C39We have already_____ a leading market position.(1.0分)1.0 分A、acquiredB、gotC、achievedD、obtained正确答案: D 我的答案:D40Usually speaking, when should we get to the airport for the international flight?(1.0分)1.0 分A、3 hours before taking offB、2 hours before taking offC、1 hours before taking offD、40 mins before taking off正确答案: B 我的答案:B二、多选题(题数:15,共 30.0 分)1What can do to get the business concluded for both buyers and sellers? (2.0分)1.0 分A、lower the priceB、increase the quantityC、limit the time of shippmentD、limit the ways of payment正确答案: ABCD 我的答案:ABC2The packing is strong enough to stand __________.(2.0分)2.0 分A、long sea voyageB、rough handlingC、a lot of joltingD、shock正确答案: ABCD 我的答案:ABCD3Is there any standard room available on next Sunday ?(2.0分)0.0 分A、Sorry, we don't have any standard room. How about the room with king-size bed?B、I'm afraid, all the standard rooms are reserved. But we still have some double rooms.C、I'm afraid, no standard rooms at that time. But we still have some twin rooms.D、Sorry, all the standard rooms have been booked. How about the queen-bed room? 正确答案: ABD 我的答案:ABCD4Which of the following aspects need to be given in order to find the lost luggage?(2.0分)2.0 分A、your flight numberB、your ageC、description about your luggageD、your contact number or address正确答案: ACD 我的答案:ACD5what cannot be allowed for clearance?(2.0分)2.0 分A、Articles not for peosonal useB、Articles exceeding the reasonable amountC、Articles exceeding the limitation of the permitted value D、Articles without payment of required duties正确答案: ABCD 我的答案:ABCD6Shipment is to be ______ during October.(2.0分)2.0 分A、effectedB、forcedC、madeD、taken正确答案: AC 我的答案:AC7My name is Lucy Smith. And I’m____ Sales Department of Rainbow Company.(2.0分)2.0 分A、in charge ofB、major inC、responsible forD、master正确答案: AC 我的答案:ACWhat kind of element could be referred when we invite our guests to the conference?(2.0分)2.0 分A、HostB、Time & LocationC、Theme and PurposeD、Attendees and Note speakers正确答案: ABCD 我的答案:ABCD9What is the ways of promoting exhibitions?(2.0分)1.0 分A、TelemarketingB、PosterC、Radio BroadcastingFace to face talk正确答案: ABCD 我的答案:ABC10What information should we offer when we reserve an air ticket?(2.0分)2.0 分A、Personal nameB、Leaving dateC、DestinationD、Seat number正确答案: ABC 我的答案:ABC答案解析:11What background information could we prepare for presentation?(2.0分)2.0 分A、FounderB、Company CultureC、HistoryD、Potential Market正确答案: ABCD 我的答案:ABCD12What should be signed on the exchange form? (2.0分)2.0 分A、nameB、addressC、the amount of moneyD、nothing正确答案: ABC 我的答案:ABCWhat are those factors that may influence the final price of a product in the pricing negotiation?(2.0分)2.0 分A、Unit price.B、Quantity.C、Ways of payment.D、Discount.正确答案: ABCD 我的答案:ABCD14Which of the following is a foreign currency?(2.0分)2.0 分A、JPYB、USDC、EURCNY正确答案: ABC 我的答案:ABC15What should be included on the meeting agenda?(2.0分)2.0 分A、NameB、LocationC、TimeD、Topics正确答案: ABCD 我的答案:ABCD三、判断题(题数:30,共 30.0 分)1We should show our ID card when we are checking in at the departure lounge.(1.0分)1.0 分正确答案:×我的答案:×答案解析:2You should bring forward the appointment as soon as possible.(1.0分)1.0 分正确答案:×我的答案:×3Immigration officer will not check whether your passport and the visa are valid.(1.0分)1.0 分正确答案:×我的答案:×4It is not so necessary to exchange your name card with your customer when meeting him at the airport.(1.0分)1.0 分正确答案:×我的答案:×5At the formal dinner, you’d better not do anything until the host does it first.(1.0分)1.0 分正确答案:√我的答案:√6About two hours prior to takeoff, the gate attendant will announce the boarding time.(1.0分)1.0 分正确答案:×我的答案:×7It doesn’t matter to make jokes regarding aircraft hijacking or bombing.(1.0分)1.0 分正确答案:×我的答案:×8When receiving others’ business card, always look at it and acknowledge it.(1.0分)1.0 分正确答案:√我的答案:√9If you’d like to have a rest after the meal, you can press the button on your armrest and lean back at the same time.(1.0分)1.0 分正确答案:√我的答案:√10Most hallways are long.(1.0分)1.0 分正确答案:×我的答案:×11Which carousel is for the luggage from Shanghai? : 哪个行李传送带是负责运送来自上海的行李的?(1.0分)1.0 分正确答案:√我的答案:√12In China, it is polite to open gifts as soon as they are given to express appreciation.(1.0分)1.0 分正确答案:×我的答案:×13Is it in traveler's cheque?:能换旅行支票吗(1.0分)1.0 分正确答案:√我的答案:√14First class always boards the plane first.(1.0分)0.0 分正确答案:√我的答案:×15市场占有率 market share(1.0分)1.0 分正确答案:√我的答案:√16An offer is something given during the negotiation.(1.0分)0.0 分正确答案:×我的答案:√17You must not drink any alcohol on a plane according to the regulations . (1.0分)0.0 分正确答案:×我的答案:√18Battery and mobile pack charger are allowed in the checked luggage.(1.0分)0.0 分正确答案:×我的答案:√19The bedrock price is the lowest possible price you can get out of a negotiation.(1.0分)1.0 分正确答案:√我的答案:√20You should call the person you are scheduled earlier whenever possible.(1.0分)0.0 分正确答案:√我的答案:×21There are several ways for booking a hotel, such as online booking, telephone booking, etc..(1.0分)1.0 分正确答案:√我的答案:√22Place your napkin on the lap as soon as you are seated when you are having the western dinner.(1.0分)1.0 分正确答案:√我的答案:√答案解析:23The Chinese prefer to entertain in their homes rather than in the public places, especially when entertaining foreigners.(1.0分)1.0 分正确答案:×我的答案:×24You can talk with food in your mouth at the dinner.(1.0分)1.0 分正确答案:×我的答案:×答案解析:25Nothing should be crossed when you serve the customer at an exhibition (1.0分)0.0 分正确答案:√我的答案:×26The cellphone and laptop should be put in the basket for check.(1.0分)1.0 分正确答案:√我的答案:√27On the western dinner table, the bread and butter plate is on the center. (1.0分)1.0 分正确答案:×我的答案:×答案解析:28Providing the registration number can save our time for pulling up the information.(1.0分)1.0 分正确答案:√我的答案:√29You should introduce the old to the young.(1.0分)0.0 分正确答案:×我的答案:√30成品 Real prodcution(1.0分)1.0 分正确答案:×我的答案:×。

The World’s Only Complete L abor and Delivery Suite Introducing the first-ever, integrated solution for labor anddelivery training, featuring a complete suite of fully operable, hands-in-the-body simulators for delivery,C-Section and emergency obstetric procedures.C-SECTIONP PHCHYS TD E L I VERYAvailable Replacement Parts• U terine incision inserts for C-Section trainer 1021393• A bdominal inserts and repair inserts (each enables two incisions and two repairs) 1021394• E mergency hysterectomy replaceable uteri1021390• R eplaceable abdominal insert and pregnant uterus10213963B Scientific GmbH • Rudorffweg 8 • 21031 Hamburg • Germany • Phone: +49 40 73966-0 • Fax: +49 40 73966-100 • E-mail:*********************LABOR AND DELIVERY SUITE99834/218RealMom™C-Celia™Vaginal DeliveryThe world’s most natural and realistic vaginal delivery simulator.+Natural delivery with active, soft tissue birth canal+Realistic, soft tissue and accurate internal anatomy+Full-body female simulator and full-term baby with unsurpassed realism and lifelike appearance+Provides a full-range of delivery procedures including forceps and vacuum assist+Postpartum hemorrhage control+Instructor control of dilation and delivery progression +Physiological presentation and control of maternal andf etal heart rate, fetal heart tones and contractions,pulses, blood pressure and SPO2C-SectionA complete C-Section delivery training system availableas a full suite or in custom configurations designed tomeet your learning needs.+Fetal Extraction Simulator – open, post C-Sectionabdomen enabling difficult delivery maneuversincluding forceps and suction assist+C-Section Skills Trainer – abdominal and incisionrepair simulator with pregnant abdomen and uterusfor incision practice and tissue repair+Emergency C-Section Delivery Simulator – pregnantabdomen simulator enabling full transverse or verticalemergency C-Section through abdominal wall anduterus with baby, placenta, and pressurizedlubricationsystem with simulated amniotic fluidPostpartum HemorrhageOpen abdomen simulator for practicing hemorrhagecontrol techniques.+P ostpartum hemorrhage control trainer withintegrated pressurized bleeding and lubrication for re-pair of complex lacerations and uterine artery injuries+Open abdomen with empty, durable, multi-use uterusenables scores of procedures before uterus placement+Supports hemorrhage control techniques includingBakri Balloon, B-Lynch suture, Hayman suture andO’Leary StitchEmergency HysterectomyTraining for postpartum and caesarean hysterectomyprocedures including hemorrhage control andfully-operable removal of the uterus.+Open abdomen with bleeding and integratedlubrication includes durable, flaccid, abdominal wallinsert, attachable, partially contracted uterus+Model contains a uterus, bladder, ureters and detailedrepresentations of uterine arteriesFinally, a complete and integrated training solution f or the entire labor and delivery continuum of care.Say goodbye to the old, unreliable plastic manikin technology and discover what real, hands-in-the-body simulation looks like. OEI simulators are fully operable and feature incredibly accurate and tactile anatomy, realistic blood and fluids, and are uniquely designed to provide learners with a high-adrenaline, real-world operative experience.And, with OEI, there’s no complicated programming or setups and no simulator down time – because our products simply work.。