ASIC设计流程中的典型问题研究

- 格式:pdf

- 大小:245.48 KB

- 文档页数:5

基于FPGA的ASIC设计FPGA是一种可编程逻辑芯片,可以根据应用要求重新配置其内部连接结构和逻辑功能,实现不同的数字电路设计。

而ASIC(Application-Specific Integrated Circuit)则是专门为特定应用设计的定制化芯片,其具有更高的性能、更低的功耗和更小的尺寸。

ASIC设计流程包括以下几个主要步骤:1.设计规格和功能要求:根据应用的需求,明确芯片的规格和功能要求,包括输入输出接口、性能指标、功耗要求等。

2. RTL设计:在硬件描述语言(如VHDL或Verilog)中编写RTL (Register Transfer Level)代码,描述芯片的逻辑功能和数据流。

这些代码包括组合逻辑电路、时序逻辑电路和控制电路。

3.高级综合:对RTL代码进行综合,将其转化为逻辑综合器可以理解的结构,生成逻辑门级电路网表。

4.驱动树和时序约束:根据ASIC设计规范,为芯片设计驱动树和时序约束。

驱动树定义了输入引脚到逻辑元件的路径,时序约束定义了逻辑元件之间的时序关系。

5.逻辑布局和布线:根据门级电路网表和驱动树,进行逻辑布局和布线优化。

逻辑布局将逻辑元件放置在芯片的物理位置,布线则将逻辑元件按照要求进行连线。

这个过程通常使用专业的布局布线工具进行。

6.物理验证:进行物理验证,通过电磁兼容性(EMC)和电磁干扰(EMI)分析,确保设计符合电气规范和可靠性要求。

7.制造文件生成:生成用于制造ASIC芯片的制造文件,包括掩模数据、掩模层等。

8.芯片制造:根据制造文件,利用先进的制造工艺将ASIC芯片制造出来。

9.仿真和验证:对制造出的ASIC芯片进行功能仿真和验证,确保芯片的功能与设计要求一致。

相比于FPGA设计,基于FPGA的ASIC设计具有一些优势和挑战:优势:1.性能:ASIC设计可以在芯片层面进行优化,实现更高的性能和更低的功耗,而FPGA设计受到资源限制,无法实现如此高性能的设计。

ASIC设计流程项目策划形成项目任务(项目进度、周期管理等)。

流程:【市场需求--调研--可行性研究--论证--决策--任务书】。

系统描述和行为描述确定设计对象和目标,进一步明确芯片功能、内外部性能要求,参数指标,论证各种可行方案,选择最佳方式,加工厂家,工艺水准。

系统说明是芯片设计到逻辑和布局的第一步。

它是在设计付诸实践之前来进行的,抽象地描述了被设计的数字电路的功能、端口以及整体的结构。

然后根据系统说明进行行为描述来分析电路设计的功能、性能、服从的标准以及其它高级问题RTL描述首先,设计者需要制定待设计数字电路的工作流程或结构框图,然后将整个任务划分为几个模块,按模块建模,并用HDL语言设计结构。

工具:UltraEdit,VI代码调试对设计输入文件进行代码调试和语法检查。

工具:德彪西。

前端模拟功能模拟工具:mentor公司的modelsim、synopsys公司的vcs和vss、aldec公司的active、cadense公司的ncsim.逻辑综合逻辑综合是将逻辑级的行为描述转换成逻辑级的结构描述,即逻辑门级网表。

逻辑级的行为描述可以是状态转移图、有限状态机,也可以是布尔方程、真值表或硬件描述语言。

逻辑综合过程还包括一些优化步骤,如资源共享、连接优化和时钟分配等。

优化目标是面积最小,速度最快,功耗最低或他们之间的某种折衷。

工具:有mentor公司的leonardospectrum、synopsys公司的dc、synplicity公司的synplify。

前端的末端数据准备。

对于cdn的siliconensemble而言后端设计所需的数据主要有是foundry厂提供的标准单元、宏单元和i/opad的库文件,它包括物理库、时序库及网表库,分别以.lef、.tlf和.v的形式给出。

前端的芯片设计经过综合后生成的门级网表,具有时序约束和时钟定义的脚本文件和由此产生的.gcf约束文件以及定义电源pad的def (designexchangeformat)文件。

asic设计及验证流程Asic design and verification process is a crucial step in ensuring the functionality and quality of integrated circuits. This process involves the creation of custom hardware to perform specific functions, such as in microprocessors or memory chips. Asic design begins with defining the requirements and specifications of the chip, which includes determining the desired functionality, performance, and power consumption. This initial stage is critical in setting the foundation for the rest of the design process, as any errors or oversights here can lead to costly delays and rework later on.Asic设计和验证流程是确保集成电路功能和质量的关键步骤。

该过程涉及创建定制硬件以执行特定功能,例如微处理器或存储器芯片。

Asic设计始于定义芯片的需求和规格,包括确定所需的功能、性能和功耗。

这个初始阶段对于后续设计过程至关重要,因为这里的任何错误或疏忽都可能导致昂贵的延迟和重新工作。

Once the requirements and specifications are established, the next step in the asic design process is architectural design. This phase involves creating a high-level design of the chip, including blockdiagrams and key components. Architectural design is crucial for determining the overall structure and organization of the chip, as well as defining the interfaces between different modules. This stage also includes making decisions on technology choices, such as the use of specific components or design methodologies.一旦建立了需求和规格,Asic设计流程的下一步是架构设计。

16位冯·诺依曼结构RISC-CPU设计ASIC设计技术课程报告注:程序请联系本人索要水平有限,请海涵16位冯•诺依曼结构RISC-CPU设计摘要:探讨了一种基于SystemC的RISC-CPU建模方法,设计利用SystemC作为开发语言,Visual Stdio 6.0作为开发平台。

该模型基本达到了RISC-CPU的初步功能要求,为程序提供了一个简易的CPU模拟平台,减少了软硬件协同设计的周期,这对片上系统SOC的实现具有重要的意义关键词:SystemC、精简指令集、软硬件协同设计目录一、SystemC和RISC简介 .............................................................................. - 2 -二、系统设计思路............................................................................................. - 3 -三、模块设计..................................................................................................... - 5 -四、不足及改进................................................................................................. - 7 -五、心得体会..................................................................................................... - 7 -一、SystemC和RISC简介1.SystemCSystemC是一种软/硬件协同设计语言,一种新的系统级建模语言。

ASIC课程设计——MOS输出级电路设计与Hspice仿真————————————————————————————————作者:————————————————————————————————日期:目录一.背景介绍 (1)二.设计要求与任务 (2)三.电路原理及设计方法 (2)1.电阻负载共源级放大器电路原理分析 (3)2.有源负载共源放大器设计方法 (5)四.HSpice软件环境概述 (7)1.简介 (7)2.特点 (8)3.界面预览 (8)五.设计过程 (10)六.结果和讨论 (11)七.设计心得 (12)八.库文件程序附录 (13)一.背景介绍ASIC是Application Specific Integrated Circuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路。

ASIC的设计方法和手段经历了几十年的发展演变,从最初的全手工设计已经发展到现在先进的可以全自动实现的过程。

在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。

是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

ASIC 设计中的同步复位与异步复位Synchronous Reset and Asynchronous Reset in ASIC Design盛 娜3 刘志军SHENG Na LIU Zhi 2jun摘 要 复位问题是ASIC 设计中的一个关键问题,其处理得当与否将直接影响整个电路的性能,在此本文从多个角度对同步复位和异步复位进行了讨论和分析,并且比较了各自的优缺点,重点针对异步复位过程中存在的亚稳态问题采用两级复位同步和复位分配缓冲树的方法进行了相应的解决。

关键词 同步复位 异步复位 亚稳态 ASIC Abstract Reset is one of the key problems in ASIC design ,it will directly in fluence the performance of the whole design if it is done properly or not.This paper discussed and analyzed the synchronous reset and the asynchronous reset from several different perspectives.A C omparis on between them in the advantages and the disadvantages was conducted.The metastability problem ,exiting in the process of asynchronous reset ,was res olved by adding the tw o 2level reset syn 2chronizer logic and using reset distribution bu ffer tree.K eyw ords Synchronous reset Asynchronous reset Metastability ASIC3山东大学信息科学与工程学院 济南 2501001 引言复位问题是ASIC 设计中一个基本而又重要的问题。

基于mems+asic的功能模块异构集成设计方法标题:基于mems+asic的功能模块异构集成设计方法探讨一、引言在当今科技发展迅猛的时代,功能模块的异构集成设计方法成为了研究的热点之一,其中基于mems+asic的设计方法尤为引人关注。

本文将从深度和广度的角度对该设计方法进行全面评估,并撰写一篇有价值的文章,以帮助读者更深入地理解这一话题。

二、mems+asic技术概述1. 什么是mems?Mems(Micro-Electro-Mechanical Systems,微机电系统)是一种能够感知周围环境并能够进行相关控制的微米级、纳米级尺度的设备。

它们通常包括微型机械元件、传感器、执行器和微处理器,可在集成电路芯片上制造出来。

2. 什么是asic?Asic(Application-Specific Integrated Circuit,专用集成电路)是一种专门定制的集成电路,被用于特定的应用领域。

ASIC芯片中的电路和电子元件特别适用于某一特定应用而进行了设计与优化。

三、基于mems+asic的功能模块异构集成设计方法1. 设计思路基于mems+asic的功能模块异构集成设计方法,旨在将mems和asic两种技术进行结合,以实现更复杂的功能模块设计。

通过将mems技术的微型机械元件和传感器与asic技术的电子元件结合,可以实现更高效、更精准的功能模块。

2. 设计流程针对该设计方法,设计流程需要考虑mems和asic的集成,包括传感器和执行器的设计、模拟电路设计、数字电路设计、系统级集成等方面。

这种异构集成设计方法需要在不同领域的专业知识上取得平衡,确保各个功能模块的协同工作。

3. 设计挑战与传统单一技术设计相比,mems+asic的设计方法面临着更大的挑战。

不同技术之间的兼容性、集成电路设计的复杂性、功耗与性能的权衡等问题都需要得到有效的解决。

四、个人观点和理解基于mems+asic的功能模块异构集成设计方法,是当前微电子领域的前沿研究方向之一。

ASIC设计流程(精选5篇)第一篇:ASIC设计流程1.使用语言:VHDL/verilog HDL2.各阶段典型软件介绍:输入工具:Summit ,ultraeditSummit公司,ultraedit仿真工具:VCS, VSSSynopsys 公司综合器:DesignCompile, BC CompileSynopsys 公司布局布线工具:Preview 和Silicon EnsembleCadence公司版图验证工具:Dracula, DivaCadence公司静态时序分析: Prime TimeSynopsys 公司测试:DFTCompileSynopsys 公司3.流程第一阶段:项目策划形成项目任务书(项目进度,周期管理等)。

流程:【市场需求--调研--可行性研究--论证--决策--任务书】。

第二阶段:总体设计确定设计对象和目标,进一步明确芯片功能、内外部性能要求,参数指标,论证各种可行方案,选择最佳方式,加工厂家,工艺水准。

流程:【需求分析--系统方案--系统设计--系统仿真】。

第三阶段:详细设计和可测性设计分功能确定各个模块算法的实现结构,确定设计所需的资源按芯片的要求,速度,功耗,带宽,增益,噪声,负载能力,工作温度等和时间,成本,效益要求选择加工厂家,实现方式,(全定制,半定制,ASIC,FPGA等);可测性设计与时序分析可在详细设计中一次综合获得,可测性设计常依据需要采用FullScan,PartScan等方式,可测性设计包括带扫描链的逻辑单元,ATPG,以及边界扫描电路BoundScan,测试Memory的BIST。

流程:【逻辑设计--子功能分解--详细时序框图--分块逻辑仿真--电路设计(算法的行为级,RTL级描述)--功能仿真--综合(加时序约束和设计库)--电路网表--网表仿真】。

第四阶段:时序验证与版图设计静态时序分析从整个电路中提取出所有时序路径,然后通过计算信号沿在路径上的延迟传播,找出违背时序约束的错误(主要是SetupTime 和HoldTime),与激励无关。

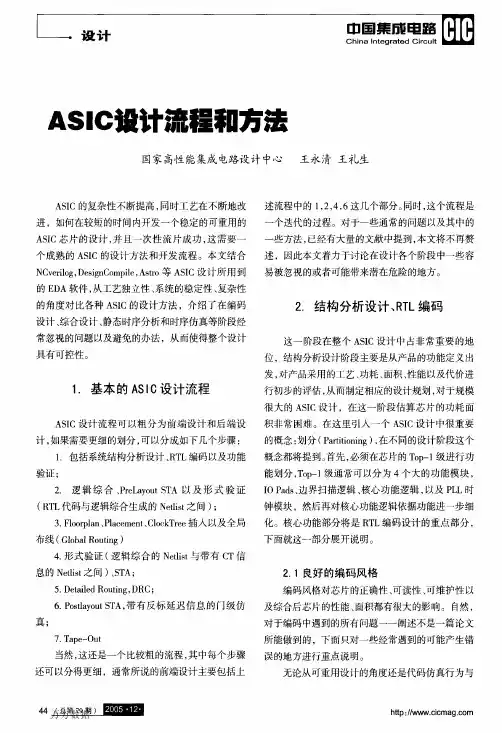

第35卷第2期2007年4月浙江工业大学学报J OURNAL OF ZH E J IAN G UN IV ERSIT Y OF TECHNOLO GYVol.35No.2Apr.2007收稿日期:2006209210基金项目:浙江省教育厅资助科研项目(20051399)作者简介:章旌红(1964—),女,浙江绍兴人,副教授,主要从事运动生物力学、电路与系统研究.A SIC 设计流程中的典型问题研究章旌红,何剑春,陶东娅(浙江工业大学信息工程学院,浙江杭州310032)摘要:随着集成电路制造工艺的快速发展,系统芯片(SOC )及其功能ASIC 模块的研究越来越引起关注.基于ASIC 设计流程,讨论了当前ASIC 设计中逻辑综合、易测性、低功耗等一些典型问题,并以工艺独立阶段和工艺映射阶段中ASIC 综合需要解决的问题为研究重点,结合实例分析了其中的关键环节,以期作为高性能ASIC 设计优化、可测性设计、设计验证等方向分析研究的前期工作.关键词:ASIC ;逻辑综合;可测性设计;低功耗中图分类号:TN402 文献标识码:A 文章编号:100624303(2007)022*******R esearch on some typical problems in the ASIC design flowZHAN G Jiang 2ho ng ,H E Jian 2chun ,Tao Dong 2ya(College of Information Engineering ,Zhejiang University of Technology ,Hangzhou 310032,China )Abstract :Wit h t he fast develop ment of IC fabricating technology ,research on SOC and ASIC modules cause more attention.According to t he design flow ,some typical p roblems ,such as log 2ic synt hesis ,testability and low power dissipation ,was discussed in t he paper.And most atten 2tion was paid on t he ASIC synt hesis in t he technology independency and technology mapping p ro 2cedure separately.We hope t hat t he research is a good guide for t he st udy on design optimization ,design for test and verification.K ey w ords :ASIC ;logic synt hesis ;design for test ;low power dissipation0 引 言随着集成电路设计制造技术的进步,系统芯片(SOC )得到快速发展.对SOC 中完成特定功能的专用集成电路(ASIC )的研究显得越来越重要.通常,ASIC 芯片在尺寸、耗电量、发热量和成本方面比一般的IC 部件要求更高.近年来,由于鲁棒性设计方法和自动电路综合工具在芯片设计过程中的普遍应用,从高层次的设计描述到最后的芯片布图和掩模阶段的工作难度明显降低,导致ASIC 芯片和集成了ASIC 模块的芯片的需求迅速上升.目前,从消费电子到空间技术领域,ASIC 和具有ASIC 模块的半导体芯片都得到了广泛应用.笔者研究了ASIC 设计流程中逻辑综合、易测性、功耗优化等关键问题,着重讨论设计流程、设计方法、综合和物理设计方面的问题.1 ASIC 设计流程ASIC 的设计制造工序繁多.产品的性能要求一旦确定下来,就需要完成从高层次设计、电路综合到低层次详细设计的一系列工作.ASIC 设计的整个流程及各层次细节如图1所示.图1 ASIC 设计典型流程Fig.1 Typical ASIC design flow设计要求首先被表示成可执行的行为级模型.行为级模型包含了在满足时序、面积、功耗、测试等约束条件下实现的设计功能.行为级模型需要经过大量的输入条件验证,使所有的要求和功能都得到满足.行为级模型通过行为级综合工具转化成R TL 级模型.R TL 级模型使用加法器、乘法器、寄存器、多路选择器之类的寄存器级元件,通过元件互联构成设计的结构模型.R TL 级模型通过逻辑综合工具转化成逻辑门级.逻辑门级设计由门或者门的组合组成,逻辑综合通常都使用基于单元库的设计方法.门级网表需要进行最广泛的仿真,除了功能外,其他诸如时序和功耗等约束条件也需要在此分析.门级网表通过芯片区域布图、单元布局和互联布线转化成物理级设计版图(Layout ),该版图将用来产生制造芯片用的掩模组.2 ASIC 设计中的逻辑综合问题2.1 逻辑综合问题逻辑综合包括一系列的优化和技术,比如状态机优化、多级逻辑优化、重定时(Re 2Timing )、再综合(Re 2Synt hesis )、工艺映射(Technical Mapping )、版图生成后的晶体管尺寸调节等.优化目标可以是面积、速度、功耗或者多个标准,优化的具体步骤和目标有关,可大致分为两个阶段:工艺独立阶段和工艺映射阶段.工艺独立阶段优化进行操作,最小化状态;工艺映射阶段,逻辑网络被映射到某单元库,然后进行晶体管级的优化.2.2 逻辑综合的工艺独立阶段2.2.1 组合逻辑优化组合电路可以用乘积-和二级表达式表示.这类表达式可以用优化工具Esp resso ,Mini 或Presto 优化.为描述组合独立于工艺的逻辑优化步骤,以下述布尔函数为例演示逻辑网络的优化过程:F (A ,B ,C,D )=∑m (0,2,4,5,6,7,12)+∑d (8,10)其卡诺图如图2所示.根据卡诺图可得到简化的布尔函数为:F (A ,B ,C ,D )=C D +AB +B D图2 组合逻辑电路逻辑简化实例Fig.2 Simplification example for combinational logic circuit图2的卡诺图在概念上示范了组合逻辑的优化过程.该过程利用二级优化器Espresso 来优化逻辑.首先扩张包含每个on 集(函数值为1的点集)中点的卡诺圈使之尽可能大,可以覆盖无关集,不能覆盖off 集(函数值为0的点集).去冗余步骤中,对同样的点,去除中间较小的卡诺圈.最后,将剩余的卡诺圈化简,以减少相关变量数.代工厂提供的单元库常包含复杂门电路,如AND 2OR ,OR 2AND 或NOR 2AND 等.为充分利用单元库,要使用多级逻辑优化技术处理多级逻辑电路,使用厂家提供的复杂门以优化芯片的面积和延迟.当然,多级优化技术并不精确,多级网络的建模和优化只有启发式方法.2.2.2 时序逻辑优化2.2.2.1 时序电路模型时序电路通常可以通过一个有限状态机模型来表示.完整的有限状态机(FSM )描述表示为〈S ,I ,O ,f ,h 〉,其中S ,I ,O 分别指现态、输入和输出,f 为次态,h 为输出计算函数.次态函数f 可以被说明为f :S ×I →S.输出函数h 则可表示为h :S ×I →O(Mealy 机)或h :S →O (Moore 机).在Mealy 机中,・821・浙江工业大学学报第35卷输出随输入和状态而定;Moore 机中输出则只由状态决定.以一个实现“011”序列检测的Mealy 机为例讨论时序电路的设计.图3(a )为序列检测器的状态转换图,其中X 为串行数据输入端,Y 为检测结果输出端,其工作规律为:若从输入端X 检测到“011”序列,则从Y 端输出一个正脉冲;否则Y 端保持低电平.序列检测器有四个状态A ,B ,C ,D ,等价状态A 和D 合并后简化为三个状态,编码为00,01,10.图3(b )为计数器的状态转换表.对应于次态和输出向量的卡诺图示于图3(c ),从中可得简化的激励方程和输出方程:J 1=X Q 0K 1=1J 0=X K 0=X Z =X Q 0Q 1(3)图3(d )为根据上述等式得到的电路图.该电路有两个J K 触发器,对应状态的二位变量;组合逻辑部分通过简单门电路来实现.图3 时序电路实例———模4计数器Fig.3 4bit counter example of sequential circuit2.2.2.2 状态最小化状态最小化的目的是减小FSM 的状态的数量,减少状态的数量不仅可以减少编码位数,还可减少信号切换次数、逻辑门数.状态最小化不仅可降低电路面积,而且可加快电路速度、降低电路功耗.状态最小化通过寻找等价状态减少状态数量.上述序列检测器例子的状态转移图中,由于状态A和D 为等价状态,因此可化简为图4(a )所示最小化状态转移图.其相应的状态转换表见图4(b ).2.3 逻辑综合的工艺映射阶段2.3.1 技术映射将基于通用单元的逻辑网表转化为厂家网表的过程称作技术映射(Technology Mapping ).技术映射的目的是建立逻辑综合和物理设计之间的联系.技术映射允许我们将某设计在不同的技术和方式下实现.一般,单元库供应商可提供不同类型的库,每个类型的库可能在面积、性能、功耗和可靠性方面进行了特别的优化.技术库中的每个单元包括物理版图、时间模型、线负载(Wire 2Load )模型、行为模型(V HDL/Veril 2og 模型)、电路原理图和单元图标.对更大的单元,还包括它的布线和测试策略.CAD 工具使用库中的延时特性来分析电路和确定网表中每个节点上的电容,再使用库中每个单元的延时特性和库中的延时计算公式,计算出每个节点上的延时.连线的电容通过线负载模型初始估计,以后则使用布图规划、布局和布线工具返回的反注释信息计算得到.2.3.2 单元库绑定单元库绑定是将布尔等式或布尔网络转换成由单元库中逻辑门构成的网络的过程.单元库绑定方・921・第2期章旌红,等:ASIC 设计流程中的典型问题研究法被分成两种:基于规则的方法和基于树的方法.基于规则的库绑定技术利用简单的规则来认定电路模式,并将该模式替换为库中的等价模式.绑定规则来自库中单元的特性.基于规则的方法是启发性的,因为优化结果受到使用不同规则的次序的很大影响.基于规则的方法允许渐进式精练,允许重新绑定单元来查找全局最优结果.基于树的方法有“结构覆盖/匹配”和“布尔覆盖/匹配”两种.在结构方法中,逻辑网络被表示为一个以图表示的代数表达式.基于树的匹配类似于模式匹配.库中的单元被表示为模式图,匹配目的是找到一个对逻辑网络节点的覆盖,使得某些代价(可以是面积,功耗等)得到优化.3 静态时序分析时序分析的目的是保证时序约束(如触发器的建立/保持时序关系等)能够满足要求,保证电路的关键路径能满足所设定的时间预算.静态时序分析利用单元库中所提供的门延迟、上升时间、下降时间、电容、负载等内容来决定每个门的延迟和连线的延迟.静态时序分析必须遍历电路网表中所有路径来检测它们是否满足时序要求,它沿着不同的路径计算延时,并辨别其中的关键路径(Critical Pat h).深亚微米级设计中,连线延时的影响超过了门延时.为了在静态时序分析时计算路径延时,对互连电容和芯片线负载模型的准确估计非常重要,必须在布图规划的早期使用参数提取技术来获得准确估计值.经过对所有电路路径的测试,时序分析器可以决定电路中所有的关键路径.然而,电路中可能存在伪路径(False Pat h),即在任何输入下,电路正常运作时都不会形成的工作路径.静态时序分析工具可以认出简单的伪路径,但不能认出所有的.对于难于辨明的伪路径,设计者必须在运行静态时序分析工具以前明确地标明它们.4 结构式设计中的可测试设计可测试性是指在一个已制成的芯片中发现制造性错误的能力.目前,DF T(Design For Testability)方法被越来越多地使用,以确保电路的可测试性.使芯片具有可测试性的方法之一是将附加的测试硬件插入芯片中并加入附加的测试引脚,如边界扫描法(Boundary Scan).边界扫描法针对芯片功能引入测试向量,测试向量和测试结果通过在附加引脚上的数据移入移出来设置和得到.而芯片内部元件的可测试性主要由两种技术来增强:串行扫描和内建自测(BIST,Built2In Self Test).4.1 串行扫描测试串行扫描技术使用扫描寄存器改善电路的可观性和可控性.一个扫描寄存器具有串行移动及并行存储能力,它在一个标准寄存器外加上了额外的串行输入输出引脚.电路中所有的扫描寄存器被连接在一个链上,连接方式是上一个寄存器的串行输出引脚和下一个寄存器的串行输入引脚相连.在正常的电路操作模式下,扫描寄存器工作状态类似于并行的存储寄存器.而在测试模式下,一个测试模式被串行扫描送入所有的电路寄存器中,然后加载时钟,再将寄存器中的结果值串行输出.输出的每一位(Bit)值将和期望的结果相比较来验证电路功能是否正确.这种方法额外开销相对较低,芯片上仅需加入一个额外输入引脚和一个额外输出引脚.但由于串行性,这种方法速度缓慢.4.2 BIST在存储器设计,比如RAM模块,一般总是通过在存储器设计中插入的嵌入式自检逻辑电路被检测.这些B IST电路使用伪随机向量,并以在一些地址区域写进数据并重新读出进行比较的方法来完成检测工作.数据路径单元也可以用B IST技术测试.B IST 电路首先由伪随机模式发生器(PRP G,Pseudo2 Random Pattern Generator)产生输入测试向量,并将这组测试向量输入待测单元,然后由特征分析器(SA,Signat ure Analyzer)进行输出位流的特征分析,确保此单元没有错误.为减少芯片的测试时间,只要不同功能单元的输入PRP G寄存器和输出SA寄存器之间没有重叠,多个功能单元就可以被同时测试.为了在尽可能少的测试时间内测试不同的单元,设计者会优化生成一个测试调度计划.在用于测试数据路径单元的BIST法中,主要的挑战有:确保每个功能单元是一个嵌入的一部分;使尽量少的寄存器成为B ILBO;能生成一个有效的测试调度表以使缩短测试时间.・31・浙江工业大学学报第35卷5 低功耗问题目前,电源管理和节省功耗已成为集成电路设计中的重要课题.有些综合工具已经把功耗估计作为优化中代价函数的一部分CMOS电路功率消耗表现在以下几方面:(1)开关电流的动态消耗.(2)切换时,N通道和P通道晶体管同时瞬时导通的短路电流引起的功耗.(3)在静态工作下的漏电流功耗.当然,CMOS门电路中主要的消耗为开关时电流的动态功耗.CMOS门电路的平均开关功耗由下式给出P=α×C L×V DD×f(4)其中:f是系统时钟频率;V DD是供电电压;C L是负载电容;α是开关的活动率.从该公式可推断出降低功耗的高层策略包括: ●基于活动状态判断的部件关闭:在元件的非活动状态,关闭时钟或停止电源供给来关闭这些部件.实现的手段是实现判断某个部件在某个时钟周期里不活动,然后用门控时钟(Clock Gating)或在使能端加上Disable控制信号来关闭. ●降低供电电压:在尽可能低的电压下运行.嵌入在便携式设备中的许多芯片都采用这种方案.当然,要考虑其它影响因素,如速度、噪声裕量等. ●降低开关活动率:改变设计的结构,比如重新构造其计算、通讯和存储,目的是降低开关活动的频繁程度,即减小α.到目前为止,该领域的研究集中在减少信号跳变的方法上,特别是连线和存储器的信号跳变.6 结 论半导体技术不断进步,电路的密度和功能不断增加,ASIC设计方法提升到了更高的系统规格说明级别,同时要使用越来越多的CAD工具使设计过程自动化.对半导体设备的需求持续增长,加快了设计工具和设计方法的研发.对便携式设备的需求促进了高功率效率的设计和功耗估计技术的发展.物理设计和高层设计之间的联系越来越复杂,从高级综合到逻辑设计,再到物理设计的各个阶段成为更紧密的整体.以工艺独立阶段和工艺映射阶段中ASIC综合需要解决的问题为重点,讨论了当前ASIC设计中逻辑综合、易测性和低功耗等一些典型问题,作为进一步分析研究的先导工作.参考文献:[1] BIERRE A.Bounded model checking[M].Acadmic Press:Advances in Computers,2003.[2] 李光辉,邵明,李晓维.验证包含黑盒的电路设计的有效方法[J].计算机学报.2004,27(6):7962802.[3] 李光辉,邵明,李晓维.一个适于形式验证的A TP G引擎[J].计算机研究与发展.2004,41(5):8862893.[4] ASAAD H,HA YES J.Design verification via simulation andAutomatic test pattern generation[J].IEEE ICCAD,1995, 1742180.(责任编辑:翁爱湘)・131・第2期章旌红,等:ASIC设计流程中的典型问题研究。