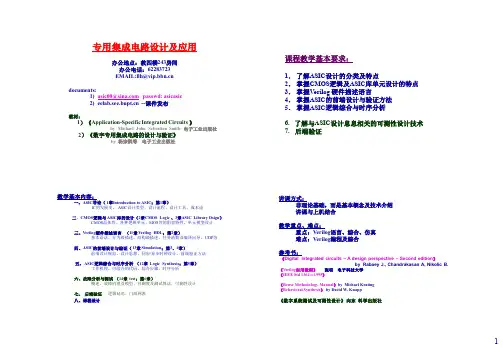

ASIC设计概论

- 格式:ppt

- 大小:132.50 KB

- 文档页数:26

asic电路设计-回复ASIC电路设计是现代集成电路设计的一种重要领域,它指的是专门为特定应用定制的集成电路设计。

本文将从什么是ASIC电路设计、ASIC电路设计的流程以及ASIC电路设计的应用领域三个方面进行详细的阐述。

首先,我们来了解什么是ASIC电路设计。

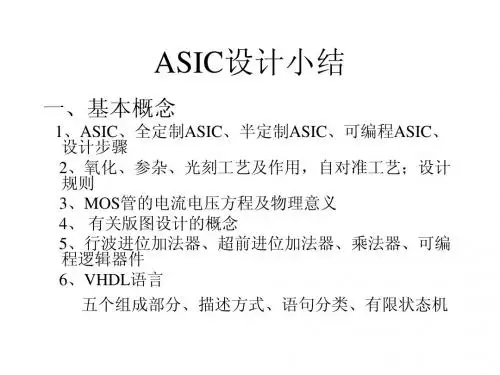

ASIC是Application Specific Integrated Circuit的缩写,翻译过来就是“特定应用的集成电路”。

与通用的微处理器或FPGA不同,ASIC电路是根据特定的应用要求进行设计与制造的。

它的主要特点是定制性强、功耗低、成本相对较高以及性能稳定。

ASIC电路设计分为前段设计和后段设计两个阶段,前段设计负责功耗估算、逻辑分组、布局等工作,后段设计则负责物理实现、时序分析、验证等工作。

接下来,我们来介绍ASIC电路设计的流程。

ASIC设计流程包含多个阶段,其中主要包括需求分析、架构设计、逻辑设计、物理设计以及验证等环节。

首先,需求分析阶段是指对于要设计的ASIC电路进行需求的梳理、分析和整理。

这一阶段可以通过市场调研、行业需求分析等方式来完成,从而明确ASIC电路的功能要求、性能指标、接口标准等。

接下来,架构设计阶段是指根据需求分析得出的要求,对整个电路进行总体的设计规划。

在这一阶段,设计师需要考虑到有效的电路结构、适配周边系统、最小化功耗、统一管理等因素。

然后,逻辑设计阶段是将架构设计得到的电路特性转化为逻辑元件的网络连接。

这一阶段的主要工作是基于功能需求,将模拟电路中的逻辑、时序和控制要素转化为由逻辑门和寄存器组成的逻辑结构。

随后,物理设计阶段是将逻辑设计翻译为几何结构,并通过全局布局、详细布局和布线等过程来生成最终的物理设计图。

这一过程涉及到算法、工具和约束的选择,以及布局和布线的优化。

最后,验证阶段是对设计的ASIC电路进行功能验证和时序验证。

这个阶段通常有两个层次的验证,分别为门级验证和模块级验证。

在验证过程中,设计师需要通过仿真、测试和调试来确保ASIC电路的正确性和稳定性。

专用集成电路设计引言专用集成电路(ASIC)是根据特定应用的需求进行定制设计的集成电路。

相比通用集成电路,ASIC更加高效、快速和可靠。

本文将详细讨论ASIC设计的原理、流程和应用。

ASIC设计原理ASIC设计的原理基于数字电子学和半导体技术。

在ASIC中,数字信号通过逻辑门的组合和时钟信号的控制来实现数据处理和控制功能。

ASIC设计流程ASIC设计流程可以分为以下几个步骤:需求分析在需求分析阶段,设计团队与客户紧密合作,明确设计目标和要求。

包括功能需求、性能指标、功耗要求等。

架构设计在架构设计阶段,设计团队根据需求分析的结果,确定ASIC的整体架构。

包括电路的模块划分、模块功能和接口定义等。

功能设计在功能设计阶段,设计团队根据架构设计的指导,对ASIC的功能电路进行详细设计。

包括逻辑电路设计、时序设计和电路优化等。

物理设计在物理设计阶段,设计团队对功能设计的结果进行布局和布线。

包括布局规划、金属层分配和信号线的布线等。

验证与测试在验证与测试阶段,设计团队对ASIC进行功能验证和性能测试。

包括电路仿真、时序分析和功能验证等。

产线生产在产线生产阶段,设计团队将验证通过的ASIC设计文件发送给芯片厂商进行生产。

包括掩膜制作、晶圆加工和封装测试等。

ASIC设计应用ASIC设计广泛应用于各个领域,如通信、计算机、汽车、工业控制等。

以下是一些常见的ASIC应用场景:通信领域在通信领域,ASIC被广泛用于数字信号处理、调制解调器、网络协议处理等功能。

ASIC可以提高通信设备的性能和稳定性。

计算机领域在计算机领域,ASIC用于处理器、内存控制器、图形处理器等重要组件。

ASIC可以提高计算机的处理能力和效率。

汽车领域在汽车领域,ASIC用于安全控制、驾驶辅助和车载娱乐等系统。

ASIC可以提高汽车的安全性和性能。

工业控制领域在工业控制领域,ASIC用于工业自动化、机器人控制和传感器接口等应用。

ASIC 可以提高工业生产的效率和稳定性。

数字逻辑电路asic设计数字逻辑电路ASIC设计是一个复杂的过程,涉及多个阶段。

以下是设计的基本步骤:1. 功能指标:明确设计的目的和功能需求,这通常涉及到详细的功能描述和接口定义。

2. 系统级设计:使用高级语言(如Matlab、C等)对各个模块进行描述,并进行方案的可行性验证。

3. 前端流程:RTL寄存器传输级设计:使用硬件描述语言(如Verilog)对电路进行描述,重点是寄存器之间的传输。

功能验证(动态验证):对设计的功能进行仿真验证,需要激励驱动,是动态仿真。

常用的仿真验证工具包括Mentor公司的Modelsim、Synopsys的VCS和Cadence的NC-Verilog。

逻辑综合(Design Compile):指定特定的综合库,添加约束文件。

逻辑综合得到门级网表(Netlist)。

4. 后端流程:物理设计(Layout):基于逻辑综合后的网表进行物理设计,包括布局、布线和时钟树综合等。

DRC/LVS 检查:进行设计规则检查和布局与电路图一致性检查,确保设计的正确性和工艺的可行性。

5. 形式验证(静态验证):对综合后的网表进行功能上的验证。

6. 版图生成:根据设计要求和工艺参数,生成用于制造的版图。

7. 投片制造:将生成的版图送至半导体制造工厂进行制造。

8. 测试与验证:制造完成后,对芯片进行测试和验证,确保其功能和性能满足设计要求。

9. 封装与上市:如果芯片通过所有测试和验证,则进行封装,并推向市场。

在进行ASIC设计时,需要权衡多个因素,如速度、面积、功耗和上市时间等。

另外,ASIC设计是一项复杂且技术性很强的工作,通常需要由经验丰富的工程师团队来完成。

半导体设计中的ASIC技术半导体设计是电子工业中非常重要的一个领域。

随着智能化时代的到来和传感器技术的广泛应用,半导体的应用领域也越来越广泛。

ASIC技术是半导体设计中的核心技术之一,它具有设计自由度高、集成度高、适应性强等优点。

本文将从ASIC技术的定义、应用、设计流程等方面进行探讨。

一、什么是ASIC技术ASIC技术全称Application Specific Integrated Circuit,中文翻译为特定应用集成电路。

它是在适当的目的下,以满足特定应用需求的要求为前提,利用现有器件或设计出新器件,规划电路结构等多种方法,使用半导体技术生产出的一种特定用途的集成电路。

ASIC技术的特点是功能集成度高、速度快、性能稳定、体积小、功耗低、价格昂贵。

ASIC技术通常分为两种类型:全定制ASIC和标准单元ASIC。

前者是根据客户特定的需求,设计出专用的电路结构,从而满足客户特定的功能需求;后者是使用现有的基本模块,通过连接和调整的方式组成电路,达到特定的功能。

二、ASIC技术的应用领域ASIC技术的应用非常广泛,一般来说,ASIC可以被应用于需要高性能计算和处理的系统中。

例如:工业自动化、汽车电子、医疗、生物、通信、音视频、安防等领域。

下面以智能家居领域为例进行介绍:在智能家居系统中,各种传感器、执行机构等设备需要集成起来,由一个中央控制器进行控制。

这样可以实现智能家居的自动化控制,包括温度、湿度、光照度等环境因素控制,还可以实现家电的遥控、智能化的场景控制以及对家庭安防进行控制。

ASIC技术的应用可以帮助智能家居系统实现高度集成、高准确性和低功耗目标的同时,通过针对特定的应用领域的性能优化提供更强的支撑。

三、ASIC技术的设计流程ASIC技术的设计主要包括前端设计和后端设计两部分。

前端设计主要包括需求分析、电路设计、逻辑验证和电路仿真等流程。

ASIC的电路设计分为数字电路设计和模拟电路设计两个部分,其中模拟电路的设计比数字电路更为复杂。