数字ASIC设计流程

- 格式:pdf

- 大小:1019.11 KB

- 文档页数:3

asic 工程师手册

ASIC(Application-Specific Integrated Circuit)工程师手册是一个非常专业的技术指南,用于指导ASIC工程师进行集成电路设计、验证、测试和实现。

以下是一个可能的ASIC工程师手册的内容大纲:

第一章:概述

ASIC简介

ASIC的应用领域

ASIC的设计流程

第二章:集成电路设计基础

集成电路的基本构成

集成电路设计工具简介

集成电路设计语言(如Verilog和VHDL)

第三章:ASIC设计流程

需求分析

规格说明

架构设计

逻辑设计

物理设计

布线与布局

测试与验证

第四章:ASIC验证方法

仿真验证

形式验证

静态时序分析(STA)

物理验证(DRC/LVS)

第五章:ASIC测试技术

测试策略与测试计划

测试向量生成

内建自测试(BIST)

故障模拟与故障覆盖率分析

第六章:ASIC实现与版图绘制

工艺选择与参数提取

设计版图生成与后端物理合成

DFM(可制造性设计)考虑因素

最终版图检查与验证

第七章:ASIC制程与封装

制程技术简介

封装技术与材料选择

制程与封装测试方法

第八章:ASIC可靠性与可靠性分析

ASIC可靠性概述

环境应力对ASIC的影响

ASIC可靠性分析方法与工具介绍(如加速寿命测试、失效模式和效应分析)第九章:ASIC设计案例研究

案例一:数字信号处理(DSP)ASIC设计实例案例二:通信系统ASIC设计实例

案例三:高性能计算(HPC)ASIC设计实例。

IC设计流程(转自USTC )IC从生产目的上可以分成为通用IC (如CPU,DRAM,接口芯片等)和ASIC(Application Specific Integreted Circuit)两种,ASIC是因应专门用途而生产的IC。

从结构可以分成数字IC,模拟IC,数模混合IC三种,而SOC (system on chip)则成为发展的方向。

从实现方式上讲可以分为三种。

基于晶体管级,所有器件和互连版图都采用人工的称为全定制(full-custom)设计,这种方法比较适合于大批量生产的,要求集成度高、速度快、面积小、功耗低的通用型IC或是ASIC。

基于门阵(Gate-Array)和标准单元(Standard-Cell)的半定制设计(Semi-custom)由于其成本低、周期短、芯片利用率低而适合于批量小、要求推出速度快的芯片。

基于IC生产厂家已经封装好的PLD(Programmable Logical Design)芯片的设计,因为其易用性、“可重写性”受到对集成电路工艺不太了解的系统集成用户的欢迎。

他的最大特点就是只须懂得硬件描述语言就可以使用特殊EDA工具“写入”芯片功能。

但PLD集成度低、速度慢、芯片利用率低的缺点使他只适合新产品的试制和小批量生产。

近年来PLD中发展最活跃的当属FPGA(Field Programmable GateArray)器件.从采用的工艺可以分成双极型(bipolar),MOS和其他的特殊工艺。

硅(Si)基半导体工艺中的双极型器件由于功耗大、集成度相对低,在近年随亚微米深亚微米工艺的的迅速发展,在速度上对MOS管已不具优势,因而很快被集成度高,功耗低、抗干扰能力强的MOS管所替代。

MOS又可分为NMOS、PMOS和CMOS三种;其中CMOS工艺发展已经十分成熟,占据IC市场的绝大部分份额。

AsGa器件因为其在高频领域(可以在0.35um下很轻松作到10GHz)如微波IC中的广泛应用,其特殊的工艺也得到了深入研究。

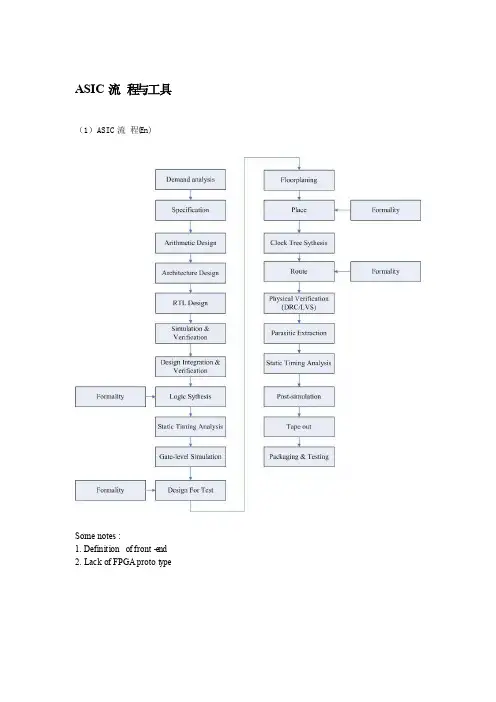

ASIC流程与工具(1)ASIC流程(En)Some notes:1. Defini tionof front-end2. Lack of FPGA protot ype(3)简化流程(4)流程所对应的工具黑体字是实验室用的工具Questi ons:Before tape-out,whichroutin e checkshould be perfor med for your layout databa se in 0.18 um proces s?a.drcb.lvsc.drc&antenn ad.simula tion(Answer:post-simula tion)What is the purpos e and genera l flow of design verifi catio n? What techni quesin your knowle dge are used in design verfic ation?验证技术:V era, SystemV erilogDC里lin k library, target library, symbol library:1.目标库(targe_libra ry):是DC在ma pping时将设计映射到特定工艺所使用的库,就是使用目标库中的元件综合成设计的门级网表2.连接库(link_l ibrar y):是提供门级网表实例化的基本单元,也就是门级网表实例化的元件或单元都来自该库。

连接库定义为标准单元的db格式的库文件加上pad db格式的库文件,加上ROM,RAM等宏单元库文件”3.符号库(symbol librar y):指定的库用来将库中的器件用图形表示出来。

whichone is worse-case in 0.18um proces s?1.1.8v,25c2.1.98v,125c3.1.62v,-40c4.1.62v,125c5.1.98v,-40c增加最大工作频率?a.lowertemper ature;b.loweroperat ing voltag e;c.lowersubstr ate doping;d.none of the above.。

基于FPGA的ASIC设计FPGA是一种可编程逻辑芯片,可以根据应用要求重新配置其内部连接结构和逻辑功能,实现不同的数字电路设计。

而ASIC(Application-Specific Integrated Circuit)则是专门为特定应用设计的定制化芯片,其具有更高的性能、更低的功耗和更小的尺寸。

ASIC设计流程包括以下几个主要步骤:1.设计规格和功能要求:根据应用的需求,明确芯片的规格和功能要求,包括输入输出接口、性能指标、功耗要求等。

2. RTL设计:在硬件描述语言(如VHDL或Verilog)中编写RTL (Register Transfer Level)代码,描述芯片的逻辑功能和数据流。

这些代码包括组合逻辑电路、时序逻辑电路和控制电路。

3.高级综合:对RTL代码进行综合,将其转化为逻辑综合器可以理解的结构,生成逻辑门级电路网表。

4.驱动树和时序约束:根据ASIC设计规范,为芯片设计驱动树和时序约束。

驱动树定义了输入引脚到逻辑元件的路径,时序约束定义了逻辑元件之间的时序关系。

5.逻辑布局和布线:根据门级电路网表和驱动树,进行逻辑布局和布线优化。

逻辑布局将逻辑元件放置在芯片的物理位置,布线则将逻辑元件按照要求进行连线。

这个过程通常使用专业的布局布线工具进行。

6.物理验证:进行物理验证,通过电磁兼容性(EMC)和电磁干扰(EMI)分析,确保设计符合电气规范和可靠性要求。

7.制造文件生成:生成用于制造ASIC芯片的制造文件,包括掩模数据、掩模层等。

8.芯片制造:根据制造文件,利用先进的制造工艺将ASIC芯片制造出来。

9.仿真和验证:对制造出的ASIC芯片进行功能仿真和验证,确保芯片的功能与设计要求一致。

相比于FPGA设计,基于FPGA的ASIC设计具有一些优势和挑战:优势:1.性能:ASIC设计可以在芯片层面进行优化,实现更高的性能和更低的功耗,而FPGA设计受到资源限制,无法实现如此高性能的设计。

数字逻辑电路asic设计数字逻辑电路ASIC设计是一个复杂的过程,涉及多个阶段。

以下是设计的基本步骤:1. 功能指标:明确设计的目的和功能需求,这通常涉及到详细的功能描述和接口定义。

2. 系统级设计:使用高级语言(如Matlab、C等)对各个模块进行描述,并进行方案的可行性验证。

3. 前端流程:RTL寄存器传输级设计:使用硬件描述语言(如Verilog)对电路进行描述,重点是寄存器之间的传输。

功能验证(动态验证):对设计的功能进行仿真验证,需要激励驱动,是动态仿真。

常用的仿真验证工具包括Mentor公司的Modelsim、Synopsys的VCS和Cadence的NC-Verilog。

逻辑综合(Design Compile):指定特定的综合库,添加约束文件。

逻辑综合得到门级网表(Netlist)。

4. 后端流程:物理设计(Layout):基于逻辑综合后的网表进行物理设计,包括布局、布线和时钟树综合等。

DRC/LVS 检查:进行设计规则检查和布局与电路图一致性检查,确保设计的正确性和工艺的可行性。

5. 形式验证(静态验证):对综合后的网表进行功能上的验证。

6. 版图生成:根据设计要求和工艺参数,生成用于制造的版图。

7. 投片制造:将生成的版图送至半导体制造工厂进行制造。

8. 测试与验证:制造完成后,对芯片进行测试和验证,确保其功能和性能满足设计要求。

9. 封装与上市:如果芯片通过所有测试和验证,则进行封装,并推向市场。

在进行ASIC设计时,需要权衡多个因素,如速度、面积、功耗和上市时间等。

另外,ASIC设计是一项复杂且技术性很强的工作,通常需要由经验丰富的工程师团队来完成。

ASIC课程设计——MOS输出级电路设计与Hspice仿真————————————————————————————————作者:————————————————————————————————日期:目录一.背景介绍 (1)二.设计要求与任务 (2)三.电路原理及设计方法 (2)1.电阻负载共源级放大器电路原理分析 (3)2.有源负载共源放大器设计方法 (5)四.HSpice软件环境概述 (7)1.简介 (7)2.特点 (8)3.界面预览 (8)五.设计过程 (10)六.结果和讨论 (11)七.设计心得 (12)八.库文件程序附录 (13)一.背景介绍ASIC是Application Specific Integrated Circuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路。

ASIC的设计方法和手段经历了几十年的发展演变,从最初的全手工设计已经发展到现在先进的可以全自动实现的过程。

在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。

是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

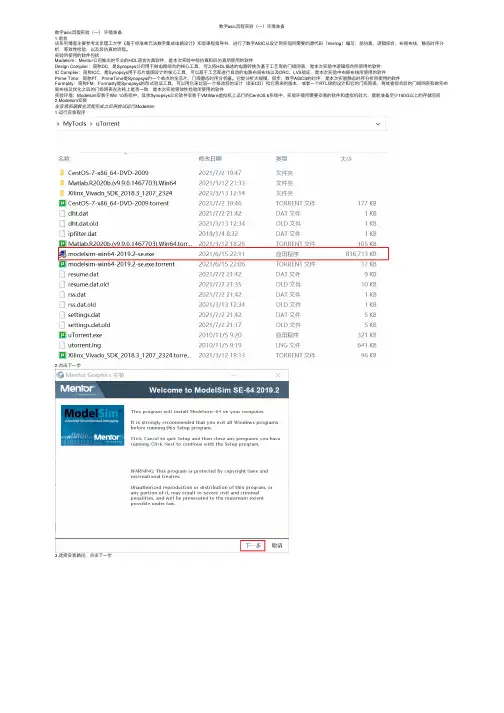

数字asic流程实验(⼀)环境准备数字asic流程实验(⼀)环境准备1.前⾔该系列博客主要参考北京理⼯⼤学《基于标准单元法数字集成电路设计》实验课程指导书,进⾏了数字ASIC从设计到实现所需要的源代码(Verilog)编写,前仿真,逻辑综合,布局布线,静态时序分析,等效性检验,以及后仿真的流程。

实验所使⽤的软件包括:Modelsim:Mentor公司推出的专业的HDL语⾔仿真软件,是本次实验中前仿真和后仿真所使⽤的软件Design Compiler:简称DC,是Synopsys公司⽤于做电路综合的核⼼⼯具,可以将HDL描述的电路转换为基于⼯艺库的门级⽹表,是本次实验中逻辑综合所使⽤的软件IC Compiler:简称ICC,是Synopsys⽤于芯⽚版图设计的核⼼⼯具,可以基于⼯艺库进⾏⾃动的电路布局布线以及DRC、LVS验证,是本次实验中布局布线所使⽤的软件Prime Time:简称PT,PrimeTime是Synopsys的⼀个单点的全芯⽚、门级静态时序分析器。

它能分析⼤规模、同步、数字ASICS的时序,是本次实验静态时序分析所使⽤的软件Formality:简称FM,Formality是Synopsys的形式验证⼯具,可以⽤它来⽐较⼀个修改后的设计(如ECO)和它原来的版本,或者⼀个RTL级的设计和它的门级⽹表,再或者综合后的门级⽹表和做完布局布线及优化之后的门级⽹表在功耗上是否⼀致,是本次实验等效性检验所使⽤的软件实验环境:Modelsim安装于Win 10系统中,其余Synopsys公司软件安装于VMWare虚拟机上运⾏的CentOS 6系统中,实验环境所需要安装的软件和虚拟机较⼤,提前准备⾄少150G以上的存储空间2.Modelsim安装在安装和破解全流程完成之后再尝试运⾏Modelsim1.运⾏安装程序2.点击下⼀步3.选择安装路径,点击下⼀步4.点击同意5.等待安装6.提⽰安装快捷⽅式7.添加路径8.不安装Hardware Security Key Driver,该步骤⼀定选否,不然会导致安装失败9.安装完成10.取消⽂件 mgls64.dll 的只读属性把MentorKG.exe和patch_dll.bat⼀起拷贝到modelsim安装⽬录的win32或win64下(modelsim⼀定要在这个⽬录下)运⾏patch_dll.bat,产⽣license设置环境变量MGLS_LICENSE_FILE,变量值为license放置的⽬录。

asic设计方法知识点ASIC(Application Specific Integrated Circuit,专用集成电路)是根据特定应用需求进行设计的芯片。

它经过专门的设计和验证,以实现特定功能或任务。

本文将介绍ASIC设计方法的相关知识点,包括设计流程、设计方法和验证技术。

一、设计流程ASIC设计流程是按照一定的步骤进行的,主要包括需求分析、体系结构设计、逻辑设计、物理设计和验证。

下面将对这些步骤进行详细介绍。

1. 需求分析在需求分析阶段,设计人员需要明确ASIC的功能需求和性能指标。

他们与客户进行沟通,并根据客户所述需求进行详细分析。

在这个阶段,定义ASIC的输入输出接口和芯片的整体功能。

2. 体系结构设计体系结构设计是确定ASIC内部模块之间的关系和功能分配。

在这个阶段,设计人员将高层次的功能分解为多个模块,并定义它们之间的通信方式和数据交换。

还可以选择合适的处理器和外围设备。

3. 逻辑设计逻辑设计将体系结构设计的模块进行电路层次的设计。

在这个阶段,设计人员采用HDL(Hardware Description Language)编写硬件描述语言代码,然后进行逻辑综合和布局布线。

逻辑综合将HDL代码转化为逻辑网表,布局布线则将逻辑网表转化为物理布局。

4. 物理设计物理设计主要包括布局、布线和时序优化。

在设计布局时,需要确定各模块的相对位置和布局规则,以满足尺寸和性能要求。

布线阶段用于确定模块之间的互连路径,以及时序优化以确保设计的正确性和性能。

5. 验证验证是整个设计流程中非常重要的一步,确保ASIC设计满足规格要求。

验证可以包括功能仿真、时序仿真、形式验证和硬件验证等。

在验证阶段,设计人员需要使用专业的仿真和验证工具对设计进行验证,并解决可能出现的问题。

二、设计方法ASIC设计方法包括全定制设计、半定制设计和可编程逻辑设计。

下面将分别介绍这三种方法。

1. 全定制设计全定制设计是一种从零开始的设计方法,它提供了最大的灵活性和性能优化。