ppt26 三态输出CMOS门

- 格式:ppt

- 大小:186.50 KB

- 文档页数:3

集成电路课程设计前言集成电路在当今社会中发挥着越来越重要的作用。

也越来越成为衡量一个国家高科技技术水平的重要指标。

作为一门重要的课程,集成电路课程设计是电子科学与技术专业要求的实践课程,主要目的是使学生熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础。

提高学生综合运用已掌握的知识,利用相关软件,进行集成电路芯片的能力。

集成电路设计主要包括以下几个方面。

系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

1.设计需求分析1.1设计内容及其性能指标要求器件名称:CMOS三态门器件要求电路性能指标:(1)输出高电平时,|IOH |≤20μA,VOH,min=5V;(2)输出底电平时,|IOL |≤4mA,VOL,man=0V;(3)输出级充放电时间tr =tf,tpd<25ns;(4)工作电源5V,常温工作,工作频率fwork =100HZ,最大功耗Pmax=150mW。

1.2设计指标1.独立完成设计三态门芯片的全过程;2.设计时使用的工艺及设计规则: MOSIS:mhp_n12;3.根据所用的工艺,选取合理的模型库;4.选用以lambda(λ)为单位的设计规则;5.全手工、层次化设计版图;6.达到设计要各项指标要求。

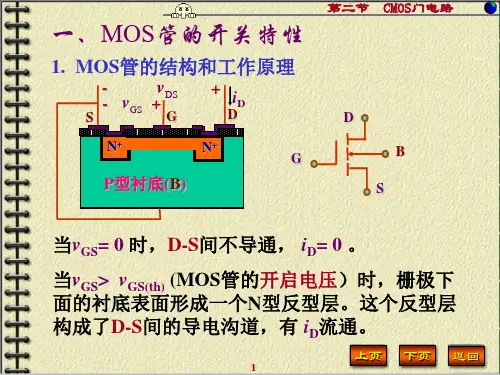

2.设计实现2.1三态门芯片简介所谓三态门(TG)就是一种传输模拟信号的模拟开关。

CMOS三态门门由一个P沟道和一个N沟道增强型MOSFET并联而成,如下图所示。

它的管脚图如图1所示,其逻辑真值表如表1所示:三态门原理图图1 三态门芯片管脚图表1 三态门真值表从图1可以看出三态门芯片是一个反相器与一组互补的增强型场效应管组成,而反相器也可以由一组互补的增强型场效应管构成。

因此,本电路的重点是增强型场效应管的使用。

从真值表我们可以看出EN为使能端。

当其为1时,输出等于输入,当其为0时,输出为高阻态。

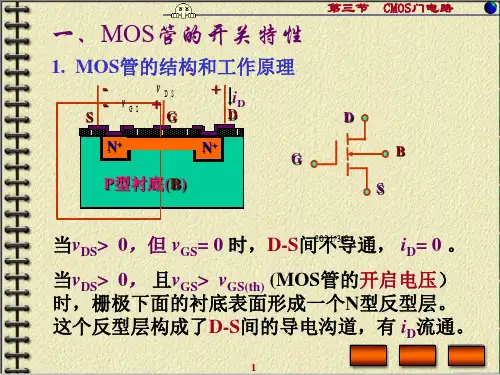

2.2电路工作原理TP和TN是结构对称的器件,它们的漏极和源极是可互换的。

三态输出门电路及应用史明科所谓三态门,就是具有高电平、低电平和高阻抗三种输出状态的门电路。

我们以前国产发射机控制电路中,尤其逻辑控制电路中,像“或(66‘与”“非”及它们组合的门电路常常使用,但却没有三态门电路的应用。

在固态机互联板电路,“I/O”板电路中,除了以上几种组合门电路,三态门电路也是必不可少的。

一、电路组成三态门电路主要有TIL三态门电路和 CMOS三态门电路,其电路结构及逻辑符号分别如下:不难看出,二种输出三态门电路都是在普通门电路的基础上附加控制电路而构成。

二、工作原理(1)TTL三态门电路工作原理图1给出了三态门的电路结构图及图形符号。

其中控制端·EN为低电平时(面=口/,P点为高电平,二极管D截止,电路工作状态和普通的与非门没有区别。

这时Y=·A’B,可能是高电子也可能是低电平,视A、B的状态而定。

而当控制端EN为高电平时(EN=1),P点为低电平,它控制T1发射极,把VBl钳位在1V,使T,、T5载止。

同时二极管D导通,T4的基极电位被钳在1V,使T4载止。

由于T4、T5同时载止,所以输出端呈高阻状态o(2)图2中是将CMOS反相器的输出端同一个模拟开关相串联,即可组成三态门。

图中T,、T2组成反相器,TG和反相器3组成模拟开关,其工作原理是:当控制端电压Ve =1时,由于模拟开关断开,输出端与电源 Vm,输出端与地都相当于开路,故呈现高阻抗状态。

当Ve=OV时,模拟开关闭合,输出电压VY 取决于反相器的输入电压。

若V4= OV,则T1截止,T2导通,VY=VDD,输出高电平;若Va=1,则Tl导通,T2载止,VY=OV,输出低电平。

上述电路中,控制端EN为低电平时与非门处于工作状态,所以该电路为低电平有效同样还有高电平有效控制电路。

三、三态门电路的应用(1)多路信号分时传递在一些复杂的数字系统(象固态机的互联板,U0板等)中,为了减少各个单元电路之间连线的数目,希望能在同一条导线上分时传递若干个门电路的输出信号。