实验四 OC门与三态门

- 格式:ppt

- 大小:1.24 MB

- 文档页数:20

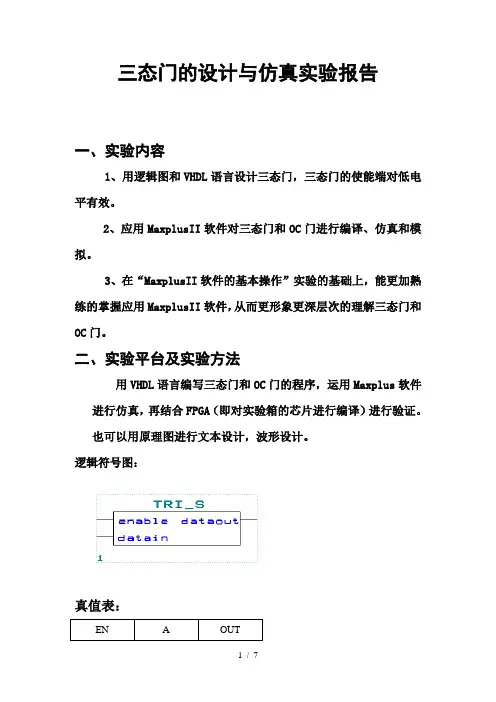

三态门的设计与仿真实验报告一、实验内容1、用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2、应用MaxplusII软件对三态门和OC门进行编译、仿真和模拟。

3、在“MaxplusII软件的基本操作”实验的基础上,能更加熟练的掌握应用MaxplusII软件,从而更形象更深层次的理解三态门和OC门。

二、实验平台及实验方法用VHDL语言编写三态门和OC门的程序,运用Maxplus软件进行仿真,再结合FPGA(即对实验箱的芯片进行编译)进行验证。

也可以用原理图进行文本设计,波形设计。

逻辑符号图:真值表:EN A OUT0 0 HI-Z0 1 HI-Z1 0 01 1 0电路图:三、实验过程1.启动MaxplusII软件;2.新建一个文本编辑文件,输入三态门的VHDL语言;3.编译。

点击file→save as,保存文件名为tri-s名称,扩展名为vhd,选择芯片类型为EPF10K20TI144-4,保存并进行编译,若编译结果出现0 error,0 warnings则说明编译通过。

4.仿真波形。

点Max+plus II→Waveform editor,出现波形图的设置界面,然后点Node→Enter Nodes from SNF→list,将输入输出端添加到界面,并设置其周期和输入波形,保存后,点Max+plus II→Simulator,即可仿真出输出的波形。

5.设计芯片。

点Max+plus II→Floorplan editor,将Unassigned Nodes & 栏中,电路的输入输出节点标号直接用鼠标“拖到” 想分配的引脚上(enabel:88,datain:89,dataout:12),点Max+plus II→programmer→configuer,然后就可以操作试验箱,观察三态门的工作情况。

四、实验结果实验步骤:1、用VHDL语言来编写程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tri_s ISPORT(enable,datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END tri_s;ARCHITECTURE bhv OF tri_s ISBEGINPROCESS (enable,datain)BEGINIF enable='1' THEN dataout<=datain;ELSE dataout<='Z';END IF;END PROCESS;END bhv;2、将上述程序保存为文件名为tri_s.vhd的文件,点击Maxplus里的compiler进行编译,出现如下图,编译成功。

集电极开路门与三态门输出的应用一.实验内容与目的实验目的:进一步了解逻辑门的结构,熟悉OC 门和三态门的逻辑功能和用途,特别是集电极负载电阻R L 对OC 门的影响。

实验内容:1.用OC门74LS03验证OC门的“线与”功能。

2.测试输出电平的转换得出结论3.验证三态门74LS125的逻辑功能。

当E拔无效为高电平,三态门输出为高阻态时,输出Y对应开关K的状态(接+5V或地)为高电平或低电平;当E 拔有效为低电平时,Y=A。

4.测试上拉电阻的取值范围。

实验仪器:HBE硬件基础电路实验箱,数字万用表元器件:74LS00,74LS03,74LS06,74LS125二.实验过程与数据分析1.用OC门74LS03验证OC门的“线与”功能步骤:了解74LS03的引脚排列图:定位标志下的引脚1,然后逆时针开始引脚2,3…13,14共十四的引脚,其中下行为引脚1到引脚7,上行为引脚8到引脚14,引脚7接地,引脚14接点语言正极,引脚1引脚2为逻辑与非门的输入端,引脚3为其逻辑输出端,依次引脚4,5,6,引脚13,12,11,引脚10,9,8为一个独立的逻辑与非门,其中引脚6,11,8为各自的输出端。

然后按照引脚内部排列的各自功能接线:打开实验箱电源,找到实验箱上已经固定好的74LS03(这里在实验箱的IC15 DIP14),用导线把引脚7 接实验箱的接地插孔,引脚14用导线接实验箱的直流5V电源插孔。

然后在实验箱的十六位逻辑电平输出中选择两位用导线各自连接74LS03的引脚1,引脚2作为与非门的输入端,把74LS03的引脚3输出端用导线连接到十六位逻辑电平显示中的一个插孔中。

然后按下5V直流电源的开关。

开始测试。

实验连接的电路图如下:OC门74LS03的测量结果如下:分析:2.输出电平的转换测试OC门74LS03的输出电压,参考下图,输入A、B接逻辑电平输出信号,输出端Y接直流电压表。

VL接+5V,电阻RL为4.7千欧,观测输出与输入信号的逻辑关系,如果去掉RL,观测输出信号的变化。

实验四 TTL 集电极开路门和三态输出门测试一、实验目的1、掌握TTL 集电极开路门(OC 门)的逻辑功能及应用。

2、了解集电极负载电阻L R 对集电极开路门的影响。

3、掌握TTL 三态输出门(3S 门)的逻辑功能及应用。

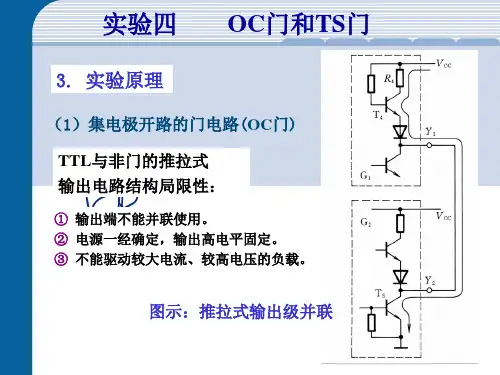

二、实验原理数字系统中有时需要把两个或两个以上集成逻辑门的输出端直接并接在一起完成一定的逻辑功能。

对于普通的TTL 电路,由于输出级采用了推拉式输出电路,无论输出是高电平还是低电平,输出阻抗都很低。

因此,通常不允许将它们的输出端并接在一起使用,而集电极开路门和三态输出门是两种特殊的TTL 门电路,它们允许把输出端直接并接在一起使用,也就是说,它们都具有“线与”的功能。

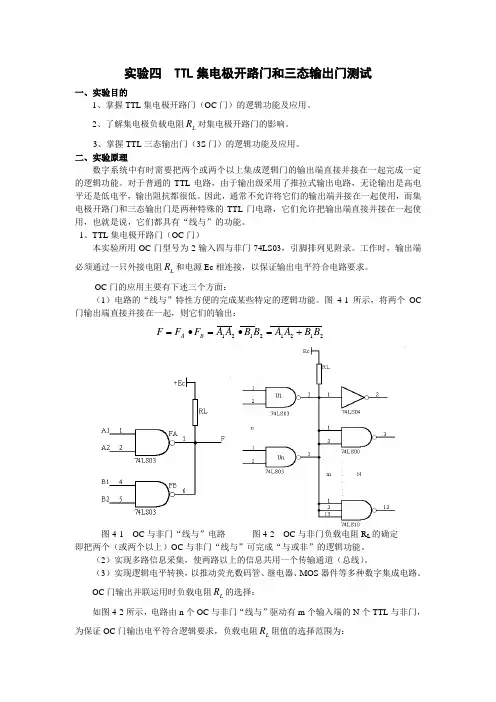

1、TTL 集电极开路门(OC 门)本实验所用OC 门型号为2输入四与非门74LS03,引脚排列见附录。

工作时,输出端必须通过一只外接电阻L R 和电源Ec 相连接,以保证输出电平符合电路要求。

OC 门的应用主要有下述三个方面:(1)电路的“线与”特性方便的完成某些特定的逻辑功能。

图4-1所示,将两个OC 门输出端直接并接在一起,则它们的输出:21212121B B A A B B A A F F F B A +=•=•=图4-1 OC 与非门“线与”电路 图4-2 OC 与非门负载电阻R L 的确定 即把两个(或两个以上)OC 与非门“线与”可完成“与或非”的逻辑功能。

(2)实现多路信息采集,使两路以上的信息共用一个传输通道(总线)。

(3)实现逻辑电平转换,以推动荧光数码管、继电器、MOS 器件等多种数字集成电路。

OC 门输出并联运用时负载电阻L R 的选择:如图4-2所示,电路由n 个OC 与非门“线与”驱动有m 个输入端的N 个TTL 与非门,为保证OC 门输出电平符合逻辑要求,负载电阻L R 阻值的选择范围为:iHOH OH C L mI nI V E R +-=max iL LM OL C L NI I V E R +-=min 式中:OH I ——OC 门输出管截止时(输出高电平V OH )的漏电流(约为50uA ) LM I ——OC 门输出低电平V OL 时允许最大灌入负载电流(约为20mA )iH I ——负载门高电平输入电流(<50uA )iL I ——负载门低电平输入电流(<1.6mA )c E ——L R 外接电源电压n —— OC 门个数N ——负载门个数M ——接入电路的负载门输入端总个数L R 值须小于m ax L R ,否则V OH 将下降,L R 值须大于min L R ,否则V OL 将上升,又L R 的大小会影响输出波形的边沿时间,在工作速度较高时,L R 应尽量选取接近min L R 。

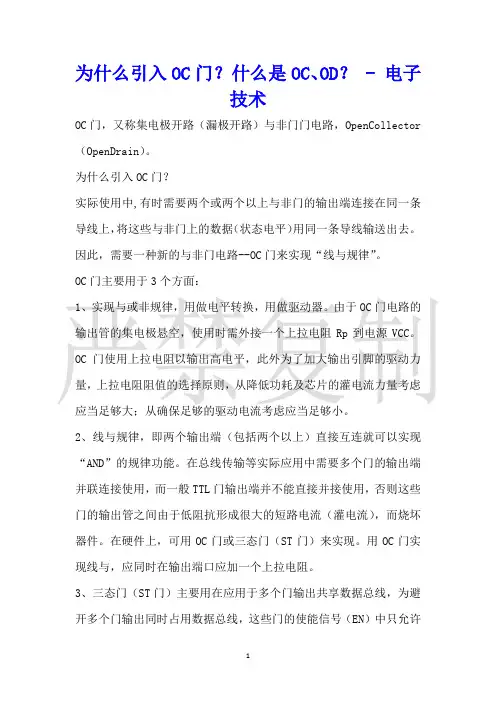

为什么引入OC门?什么是OC、OD? - 电子技术OC门,又称集电极开路(漏极开路)与非门门电路,OpenCollector (OpenDrain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与规律”。

OC门主要用于3个方面:1、实现与或非规律,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动力量,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流力量考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与规律,即两个输出端(包括两个以上)直接互连就可以实现“AND”的规律功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避开多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

什么是OC、OD?集电极开路门(集电极开路OC或漏极开路OD)Open-Drain是漏极开路输出的意思,相当于集电极开路(Open-Collector)输出,即TTL中的集电极开路(OC)输出。

一般用于线或、线与,也有的用于电流驱动。

Open-Drain是对MOS管而言,Open-Collector是对双极型管而言,在用法上没啥区分。

开漏形式的电路有以下几个特点:a.利用外部电路的驱动力量,削减IC内部的驱动。

实验3.4 三态门和OC门的应用一、实验目的1.掌握TTL三态门的逻辑应用;2.掌握TTL OC门的逻辑应用;3.熟悉TTL三态门、OC门电路应用的测试方法。

二、知识点三态门和OC门输出端可并接。

三态门有低电平、高电平和高阻三种状态;OC门可实现“线与”功能。

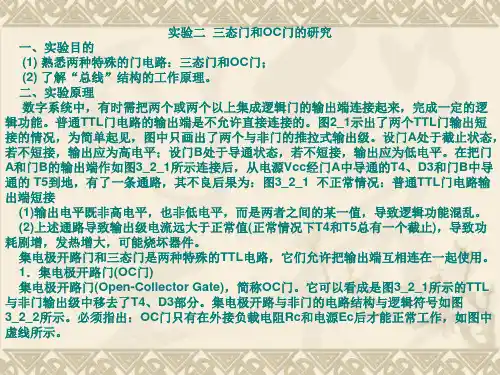

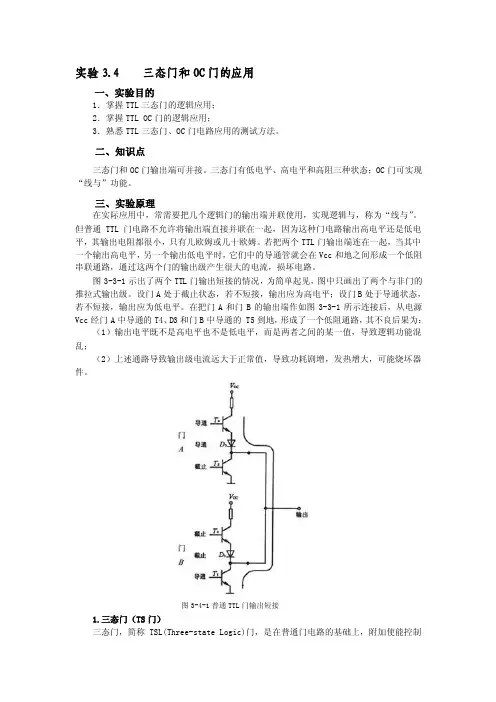

三、实验原理在实际应用中,常需要把几个逻辑门的输出端并联使用,实现逻辑与,称为“线与”。

但普通TTL门电路不允许将输出端直接并联在一起,因为这种门电路输出高电平还是低电平,其输出电阻都很小,只有几欧姆或几十欧姆。

若把两个TTL门输出端连在一起,当其中一个输出高电平,另一个输出低电平时,它们中的导通管就会在Vcc和地之间形成一个低阻串联通路,通过这两个门的输出级产生很大的电流,损坏电路。

图3-3-1示出了两个TTL门输出短接的情况,为简单起见,图中只画出了两个与非门的推拉式输出级。

设门A处于截止状态,若不短接,输出应为高电平;设门B处于导通状态,若不短接,输出应为低电平。

在把门A和门B的输出端作如图3-3-1所示连接后,从电源Vcc经门A中导通的T4、D3和门B中导通的 T5到地,形成了一个低阻通路,其不良后果为:(1)输出电平既不是高电平也不是低电平,而是两者之间的某一值,导致逻辑功能混乱;(2)上述通路导致输出级电流远大于正常值,导致功耗剧增,发热增大,可能烧坏器件。

图3-4-1普通TTL门输出短接1.三态门(TS门)三态门,简称TSL(Three-state Logic)门,是在普通门电路的基础上,附加使能控制端和控制电路构成的。

三态门除了通常的高电平和低电平两种输出状态外,还有第三种输出状态——高阻态。

处于高阻态时,电路与负载之间相当于开路。

(a )使能端高电平有效 (b )使能端低电平有效 图3-4-2三态门的结构和逻辑符号图3-4-2所示为三态门的结构和逻辑符号,图(a)是使能端高电平有效的三态与非门,当使能端EN = 1时,电路为正常的工作状态,与普通的与非门一样,实现Y = ;当EN = 0时,为禁止工作状态,Y 输出呈高阻状态。

OC门和三态门集电极开路门电路(OC门)在TTL与非门电路中将T4解掉换成电阻R c(如下图):其逻辑功能并没有改变,仍有A=B=1, T5导通,输出端为低电平Y=0。

A、B中只要有一个0, T5截止,输出端为高电平5V(TTL与非门输出高电平Yv OH=3.6V),Y=1。

由R4取代T4,显然逻辑功能未变,但速度大为降低。

把R4不做在集成电路的内部(T5的集电极处于开路状态),使用OC门集成块时,用户必须选定合适的阻值,将R c接到门的输出端与电源之间,该OC门才能具有稳定的逻辑功能(如不把R c接进去,任其集电极开路,该电路不具备正常的逻辑功能)。

这种电路称为集电极开路门电路——简称OC门。

用如下符号表示:OC门的最大特点是具有线与功能。

几个OC门共用一个R c(输出端并接在一起),其输出为单个OC门输出之积(与)。

可以等于也可以大于v cc。

三态输出门电路(TS(Three-state output Gate)门)上图为三态门输出门电路的原理图。

在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。

普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。

T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。

三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。

因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(v cc)阻抗无穷大。

因此这第三种状态也称高阻状态。

现对三种状态进行分析:控制信号可在E N处加入,也可在处加入:E N=0,=1,则C=0,v B1=0.9V,v c2=0.9Vv B4=v c2=0.9V,T4截止(T4导通的电位v B4>1.4V)v B1=0.9V,T5截止,输出端Y为高阻状态。

E N=1,=0,C=1,对与非门另两个A、B输入端无影响,为正常的与非门电路。

实验二三态门,OC门的设计与仿真

一、实验目的

熟悉三态门、OC门的原理,用逻辑图和VHDL语言设计三态门、OC门,并仿真。

二、实验内容

1.用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2.用逻辑图和VHDL语言设计一个OC门(集电极开路门)。

三、实验原理

1.三态门,又名三态缓冲器(Tri-State Buffer)

用途:用在总线传输上,有效而又灵活地控制多组数据在总线上通行,起着交通信号灯的作用。

功能:三态逻辑输出三种不同的状态,其中两种状态常见的逻辑1和逻辑0,第三个状态高阻值,称为高阻态,用Hi-Z或者Z或z表示三态缓冲器比普通缓冲器多了一个使能输入EN,即连接到缓冲器符号底部的信号。

从真值表可以看出,如果是EN=1.则OUT等于IN,就像普通缓冲器一样。

但是当EN=0时,无论输入的值什么,输出结果为高阻态(Hi-Z)。

逻辑图

真值表

EN A OUT

0 0 Hi-Z

0 1 Hi-Z

1 0 0

1 1 1

波形图

2.OC门,又名集电极开路门(opndrn)

用途:集电极开路门(OC门)是一种用途广泛的门电路。

典型应用是可以实现线与的功能。

逻辑图

真值表

A B

0 0

1 Hi-Z

波形图。

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector (Open Drain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:1、实现与或非逻辑,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC 门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。

因此,需要一种新的与非门电路来实现线与逻辑,这种门电路就是集电极开路与非门电路,简称OC 门(open collector)。

OC门电路及逻辑符号见图T1119,该电路的特点是输出管T5的集电极悬空,使用时需外接一个负载电阻R和电源Ec。

POC门的主要用途有以下3个方面:(1)实现与或非逻辑用n个OC门实现与或非逻辑的电路如图T1120所示.因为任何一个门输入全为1时,其输出为零,而n个门的输出端又并接在一起(线与),故输出Y=0,即Y=A1B1+A2B2+……+A nB n,是与或非的逻辑功能。

oc门和三态门实验

TTL三态门和OC门(也可以称为集电极开路门或漏极开路门)都是集成电路门电路的输出类型,它们之间的主要区别在于输出电压的处理方式和用途。

TTL三态门:

TTL三态门是一种具有三个工作状态的门电路,即高电平、低电平和高阻态。

在高阻态时,输出晶体管是断开的,因此输出端对地和电源电压来说都是高阻抗的,即相当于输出端与输入端完全断开。

这种门电路通常用于多路复用和双向总线应用,以及需要避免线与(线路上的电位冲突)的应用。

OC门:

OC门是一种具有推挽输出的门电路,其输出晶体管在饱和时具有较低的电阻,使得输出电压可以接近电源电压。

与TTL三态门不同的是,OC门的输出端在饱和时是低阻抗的。

因此,OC门通常用于需要高电流输出的应用,如驱动LED、电机等。

此外,OC门还可以通过将多个门的输出并联起来,实现“线与”逻辑。

在这种配置下,当所有门的输出都为高电平时,输出为低电平;而当至少一个门的输出为低电平时,输出也为低电平。

这种特性在实现多路复用、解码器等功能时非常有用。

总结来说,TTL三态门和OC门的主要区别在于输出电路的处理方式和用途。

TTL三态门适用于需要高阻态的三态输出的应用,如多路复用和双向总线;而OC门适用于需要高电流输出的应用,如驱

动LED、电机等,并可以通过并联实现“线与”逻辑。