三态门电路实验报告

- 格式:docx

- 大小:117.04 KB

- 文档页数:7

三态门的设计与仿真实验报告一、实验内容1、用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2、应用MaxplusII软件对三态门和OC门进行编译、仿真和模拟。

3、在“MaxplusII软件的基本操作”实验的基础上,能更加熟练的掌握应用MaxplusII软件,从而更形象更深层次的理解三态门和OC门。

二、实验平台及实验方法用VHDL语言编写三态门和OC门的程序,运用Maxplus软件进行仿真,再结合FPGA(即对实验箱的芯片进行编译)进行验证。

也可以用原理图进行文本设计,波形设计。

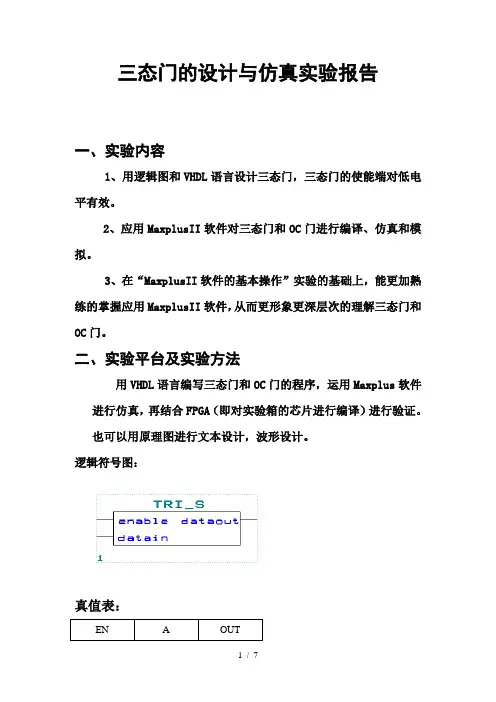

逻辑符号图:真值表:EN A OUT0 0 HI-Z0 1 HI-Z1 0 01 1 0电路图:三、实验过程1.启动MaxplusII软件;2.新建一个文本编辑文件,输入三态门的VHDL语言;3.编译。

点击file→save as,保存文件名为tri-s名称,扩展名为vhd,选择芯片类型为EPF10K20TI144-4,保存并进行编译,若编译结果出现0 error,0 warnings则说明编译通过。

4.仿真波形。

点Max+plus II→Waveform editor,出现波形图的设置界面,然后点Node→Enter Nodes from SNF→list,将输入输出端添加到界面,并设置其周期和输入波形,保存后,点Max+plus II→Simulator,即可仿真出输出的波形。

5.设计芯片。

点Max+plus II→Floorplan editor,将Unassigned Nodes & 栏中,电路的输入输出节点标号直接用鼠标“拖到” 想分配的引脚上(enabel:88,datain:89,dataout:12),点Max+plus II→programmer→configuer,然后就可以操作试验箱,观察三态门的工作情况。

四、实验结果实验步骤:1、用VHDL语言来编写程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tri_s ISPORT(enable,datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END tri_s;ARCHITECTURE bhv OF tri_s ISBEGINPROCESS (enable,datain)BEGINIF enable='1' THEN dataout<=datain;ELSE dataout<='Z';END IF;END PROCESS;END bhv;2、将上述程序保存为文件名为tri_s.vhd的文件,点击Maxplus里的compiler进行编译,出现如下图,编译成功。

实验二三态门,OC门的设计与仿真一、实验目的熟悉三态门、OC门的原理,用逻辑图和VHDL语言设计三态门、OC门,并仿真。

二、实验内容1.用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2.用逻辑图和VHDL语言设计一个OC门(集电极开路门)。

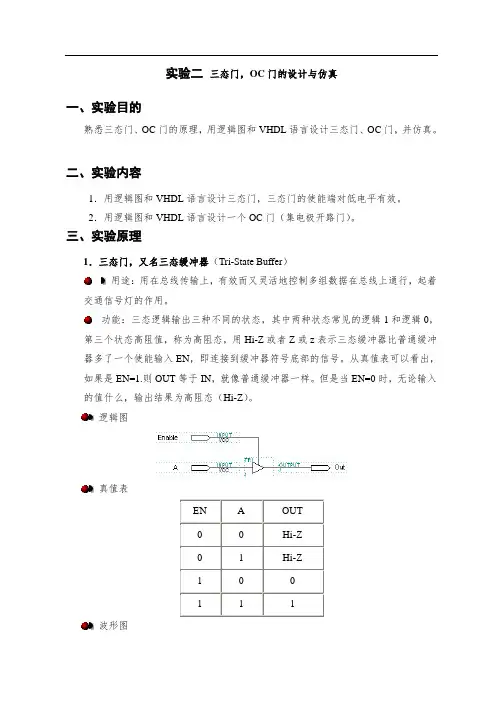

三、实验原理1.三态门,又名三态缓冲器(Tri-State Buffer)用途:用在总线传输上,有效而又灵活地控制多组数据在总线上通行,起着交通信号灯的作用。

功能:三态逻辑输出三种不同的状态,其中两种状态常见的逻辑1和逻辑0,第三个状态高阻值,称为高阻态,用Hi-Z或者Z或z表示三态缓冲器比普通缓冲器多了一个使能输入EN,即连接到缓冲器符号底部的信号。

从真值表可以看出,如果是EN=1.则OUT等于IN,就像普通缓冲器一样。

但是当EN=0时,无论输入的值什么,输出结果为高阻态(Hi-Z)。

逻辑图真值表EN A OUT0 0 Hi-Z0 1 Hi-Z1 0 01 1 1波形图2.OC门,又名集电极开路门(opndrn)用途:集电极开路门(OC门)是一种用途广泛的门电路。

典型应用是可以实现线与的功能。

逻辑图真值表A B0 01 Hi-Z波形图四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:1、编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

VHDL 设计源代码如下:三态门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tri_s ISPORT (enable,datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END tri_s;ARCHITECTURE bhv OF tri_s ISBEGINPROCESS (enable,datain)BEGINIF enable='1' THEN dataout<=datain;ELSE dataout<='Z';END IF;END PROCESS;END bhv;OC门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY oc ISPORT(datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END oc;ARCHITECTURE bhv OF oc ISBEGINPROCESS (datain)BEGINIF (datain='0') THEN dataout<='0';ELSE dataout<='Z';END IF;END PROCESS;END bhv;2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

集成门电路功能测试实验报告一实验内容1 三态门的静态逻辑功能测试。

2 动态测试三台门。

并画出三态门的输出特性曲线。

输入为CP矩形波。

3 测试三态门的传输延迟时间。

4 动态测试三态门的电压传输特性曲线。

输入为三角波。

二实验条件硬件基础实验箱,函数信号发生器,双踪示波器,数字万用表,74LS125。

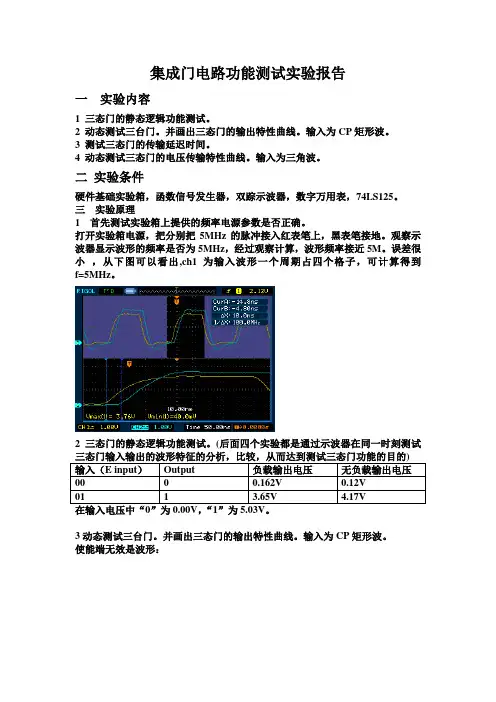

三实验原理1 首先测试实验箱上提供的频率电源参数是否正确。

打开实验箱电源,把分别把5MHz的脉冲接入红表笔上,黑表笔接地。

观察示波器显示波形的频率是否为5MHz,经过观察计算,波形频率接近5M。

误差很小,从下图可以看出,ch1为输入波形一个周期占四个格子,可计算得到f=5MHz。

2 三态门的静态逻辑功能测试。

(后面四个实验都是通过示波器在同一时刻测试3动态测试三台门。

并画出三态门的输出特性曲线。

输入为CP矩形波。

使能端无效是波形:使能端有效时输出波形4 测试三态门的传输延迟时间。

通过测量同一时刻的输入输出波形,可以观察到三态门的输出延迟。

得到波形图为CH1,CH2分别为输入输出波形,可以看出在上升沿的输出延迟为10ns然而下降沿的时候的截图已经丢失了,依稀记得在实验时候,测得是数据下降沿的输出延迟与上升沿的不一致,并且比上升沿的短。

为9.6ns,其传输延迟为两个延迟的平均值9.8ns。

5 测试三态门的电压传输特性曲线。

输入为三角波。

得到输入输出波形为:CH1为输入,CH2为输出。

得到阀值电压为0.92V。

四总结这次实验基本上和上次实验的方法一样,没遇到什么大的问题。

就是还是粗心。

五评价实验效果挺好。

巩固了对逻辑器件的功能测试的方法和操作。

三态门实验报告三态门实验报告引言:在科学研究中,实验是获取真实数据和验证理论的重要方法之一。

本次实验旨在研究三态门的工作原理和应用。

通过实验,我们能够深入了解三态门的特性,并进一步探究其在现实生活中的应用。

一、实验目的本次实验的目的是通过搭建三态门电路,观察和分析三态门的工作原理,探究其在数字电路中的应用。

二、实验材料和仪器本次实验所需材料和仪器如下:1. 电路板2. 三态门芯片3. 连接线4. 电源5. 开关6. LED灯三、实验步骤1. 将三态门芯片插入电路板中,并用连接线连接芯片和其他元件。

2. 将电源接入电路板,确保电路板正常供电。

3. 通过开关控制输入信号,观察LED灯的亮灭情况。

四、实验结果和分析通过实验观察和数据记录,我们得出以下实验结果和分析:1. 当输入信号为低电平时,LED灯熄灭。

2. 当输入信号为高电平时,LED灯点亮。

3. 当输入信号为无效电平时,LED灯保持上一状态。

根据实验结果,我们可以得出以下结论:三态门是一种数字逻辑门,具有三个输入端和一个输出端。

它的工作原理是根据输入信号的不同状态,输出相应的电平。

当输入信号为低电平时,输出为低电平;当输入信号为高电平时,输出为高电平;当输入信号为无效电平时,输出保持上一状态。

五、三态门的应用三态门在数字电路中有广泛的应用。

以下是一些常见的应用场景:1. 数据总线控制:在计算机系统中,三态门常用于数据总线的控制,实现数据的传输和共享。

2. 内存芯片:三态门可以用于内存芯片的控制线路,实现数据的读取和写入。

3. 多路选择器:三态门可以用于多路选择器的实现,根据输入信号的不同状态,选择不同的输入通路。

4. 缓冲器:三态门可以用作缓冲器,将信号从一个电路传递到另一个电路,保持信号的强度和波形。

六、实验总结通过本次实验,我们深入了解了三态门的工作原理和应用。

三态门作为一种重要的数字逻辑门,在现代电子技术中起着重要的作用。

通过进一步研究和实践,我们可以更好地应用三态门,推动数字电路技术的发展。

《数字电路与逻辑设计》仿真实验报告仿真实验1 三态输出门实现总线传输1. 仿真实验内容试用74LS125三态输出门和3-8译码器74LS138(或其它门电路),实现4路十进制数(BCD 码)的循环显示,4路显示数字可自行设定,显示效果如图1所示。

图1 仿真实验效果图总线传输4路十进制(BCD 码)信号示意图如图2所示。

总线输出图2 总线传输多路信号示意图2. 仿真实验电路设计(1)设计原理十进制数以二进制码表示需要4位,所以需要4根总线。

以四路1位数据总线为例,其原理电路如图3所示。

74LS125三态输出门的控制端为低电平有效,如EN 1’=0,EN 2’ =EN 3’ =EN 4’=1,则数据A 12传到总线上,而其余的3个三态门处于高阻状态;以此类推,若各门的控制端轮流处于低电平,其余3个控制端处于高电平,则可实现4路数据的总线传输。

可以用3-8译码器74LS138的四个输出信号Y 0’~ Y 3’作为控制信号,仿真时可以用仿真软件的字发生器从00~11循环产生,从而实现4个控制信号的自动循环有效。

总线输出图3 四路1位数据总线原理电路D 41D 31D 21D 11EN 4'EN 3'EN 2'1+VccA 1A 0 (2)仿真实验电路根据以上设计原理,设计的仿真实验电路如图4所示。

图4 仿真实验电路4. 仿真实验结果及分析(1)当字发生器输出为00时,总线数据为A12 A13A14 A15 =0010,数码管显示2,和设置的传输数据1一致,仿真实验结果如图5所示。

图5 仿真实验结果(2)当字发生器输出为01时,总线数据为A12 A13A14 A15 =0101,数码管显示5,与设置的传输数据一致,仿真实验结果如图6所示。

图6 仿真实验结果(3)当字发生器输出为10时,总线数据为A12 A13A14 A15 =0110,数码管显示6,与设置的传输数据一致,仿真实验结果如图7所示。

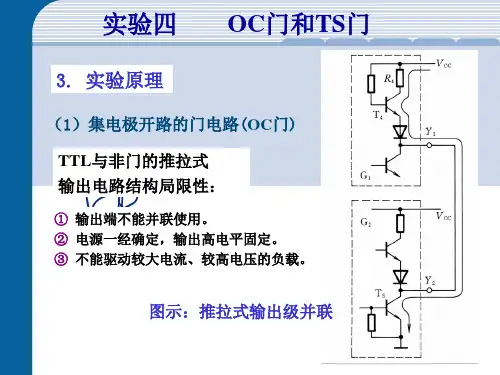

第四次实验报告实验内容:1、TTL三态门的逻辑功能2、TTL三态门的电压输出时间3、74LS125的电压传输特性曲线实验仪器与元器件:自制硬件基础电路实验箱、双踪示波器、数字万用表、74LS125实验预习:1、三态门(TS)所谓三态是指输出端而言,普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。

T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。

三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。

因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(v cc)阻抗无穷大。

因此这第三种状态也称高阻状态。

三态门有三种输出状态:高电平输出、低电平输出和高阻输出状态。

常见的三态门有控制端高电平有效和低电平有效两种类型。

三态输出门除了有多输入三态与非门,还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。

三态门主要用途之一是实现总线传输,各三态门输出端可以并联使用一个传输通道,以选通的方式传送多路信息。

使用时注意输出端并接的三态门只能有一个处于工作状态(E=0)。

其余必须处于高阻状态(E=1)。

三态门驱动能力强,开关速度快,在中大规模集成电路中广泛采用三态门输出电路,作为计算机和外围电路的接口电路。

如图为三态门的电路图:2、74LS125就是单输入、单输出的控制端低电平有效的同相三态输出门。

即E=0时,Y=A;E=1时为高阻态。

控制信号可在E N处加入,也可在处加入:E N=0,=1,则C=0,v B1=0.9V,v c2=0.9Vv B4=v c2=0.9V,T4截止(T4导通的电位v B4>1.4V)v B1=0.9V,T5截止,输出端Y为高阻状态。

E N=1,=0,C=1,对与非门另两个A、B输入端无影响,为正常的与非门电路。

当A=B=1,则T2、T5导通,v c2=1.0V(前已分析)。

实验三三态门实验三三态门一、实验目的1.熟悉计三态输出门的逻辑功能和使用方法。

2.掌握用三态门构成公共总线的特点和方法。

二、实验器材1.数字逻辑实验箱2.双踪示波器3.与非门74LS00(1片)、三态门74LS125(1片)三、预习要求1.复习三态门有关知识,了解其逻辑功能及管脚。

2.复习三态门实现总线传输的方法。

四、实验原理1.三态门(TS)三态门有三种输出状态:高电平输出、低电平输出和高阻输出状态。

常见的三态门有控制端高电平有效和低电平有效两种类型。

三态输出门除了有多输入三态与非门,还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。

例如:74LS125就是单输入、单输出的控制端低电平有效的同相三态输出门。

即E=0时,Y=A;E=1时为高阻态。

三态门主要用途之一是实现总线传输,各三态门输出端可以并联使用一个传输通道,以选通的方式传送多路信息。

使用时注意输出端并接的三态门只能有一个处于工作状态(E=0)。

其余必须处于高阻状态(E=1)。

三态门驱动能力强,开关速度快,在中大规模集成电路中广泛采用三态门输出电路,作为计算机和外围电路的接口电路。

如图2-1为三态门逻辑符号。

AB图2-1三态门逻辑符号五、实验内容1.三态门逻辑功能测试:查出三态门74LS125的引脚图,验证各三态门逻辑功能。

按图2-1(A)在实验箱上连线,先接上电源和地线,然后用逻辑电平控制输入端A和使能端E,用L显示输出Y的状态,实验结果填入下表:表2-174LS125逻辑功能表:使能输入端E0011数据输入A0101输出Y2.用三态门74LS125构成公共总线:要求:用三个三态门构成一条公共总线,参考图21(B)。

使三个输入端状态分别为“0”、“1”、CP,观测公共总线输出状态。

(1)按上述要求画出公共总线的逻辑图。

(2)在实验箱上连线:A1、0(GND),A2、1(Vcc),A3、CP(1KHz或100KHz信号源输出),三个使能端E1??E3分别由三个逻辑开关控制其电平的高低。

实验三三态门一、实验目的1.熟悉计三态输出门的逻辑功能和使用方法。

2.掌握用三态门构成公共总线的特点和方法。

二、实验器材1.数字逻辑实验箱2.双踪示波器3.与非门74LS00(1片)、三态门74LS125(1片)三、预习要求1.复习三态门有关知识,了解其逻辑功能及管脚。

2.复习三态门实现总线传输的方法。

四、实验原理1.三态门(TS)三态门有三种输出状态:高电平输出、低电平输出和高阻输出状态。

常见的三态门有控制端高电平有效和低电平有效两种类型。

三态输出门除了有多输入三态与非门,还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。

例如:74LS125就是单输入、单输出的控制端低电平有效的同相三态输出门。

即E=0时,Y=A;E=1时为高阻态。

三态门主要用途之一是实现总线传输,各三态门输出端可以并联使用一个传输通道,以选通的方式传送多路信息。

使用时注意输出端并接的三态门只能有一个处于工作状态(E=0)。

其余必须处于高阻状态(E=1)。

三态门驱动能力强,开关速度快,在中大规模集成电路中广泛采用三态门输出电路,作为计算机和外围电路的接口电路。

如图2-1为三态门逻辑符号。

A B图2-1 三态门逻辑符号五、实验内容1.三态门逻辑功能测试:查出三态门74LS125的引脚图,验证各三态门逻辑功能。

按图2-1(A)在实验箱上连线,先接上电源和地线,然后用逻辑电平控制输入端A和使能端E,用L显示输出Y的状态,实验结果填入下表:表2-1 74LS125逻辑功能表:2.用三态门74LS125构成公共总线:要求:用三个三态门构成一条公共总线,参考图21(B)。

使三个输入端状态分别为“0”、“1”、CP,观测公共总线输出状态。

(1)按上述要求画出公共总线的逻辑图。

(2)在实验箱上连线:A1、0(GND),A2、1(Vcc),A3、CP(1KHz或100KHz信号源输出),三个使能端E1……E3分别由三个逻辑开关控制其电平的高低。

实验报告四20100810410 计科四班阚琛琛【实验内容】1.测试三态门的静态逻辑功能,比较有无负载时候的区别;2.观察三态门在使能端有、无效时输入输出波形的变化;3.测量三态门传输时的延迟时间;4.测试三态门的电压传输特性曲线。

【实验环境】74LS125;示波器;信号发生器;实验箱;万用表;若干导线。

【实验电路】电路说明:如图所示,引脚14接VCC,7接GND,使能端接十六位逻辑电平之一1.在测试芯片静态逻辑功能时,输入分别接5V直流电压及地,在加上使能端时输出接一个发光二级管;2.在测试动态逻辑功能时,输入接实验箱上的CP连续脉冲,并将输入输出都连接在示波器上;3.在测试延迟时间时,输入接实验箱上的5MHZ的方波,再将输入输出接在示波器上;4.在测试传输特性曲线时,输入接信号发生器产生的三角波,再将输入输出都连在示波器上显示。

【实验过程】1.安插上74LS125芯片,按照上图说明连接电路,控制使能端有效与否,测得能端输入有效时,为禁止状态,输出高阻态,接二极管时不发光。

2.调整使能端,分别产生波形如下:使能无效:使能有效:则在使能无效时,输入出波形大致一致,当使能有效时,输出为一直线,即为高阻态。

3.调整电路,则输入输出波形为:则在图上读出延迟时间为63.2us.4.由信号发生器产生一个0-4.68V、1600HZ左右的三角波,调节示波器,显示电压传输特性曲线如图:则测得阀值电压为1.12V.【实验总结】1.在测三态门的静态逻辑功能时,要注意无负载时的连接方式,此时不能用导线接上二极管,否则跟有负载时的结果是一样的;2.在最后测动态传输特性曲线时,要注意三角波的大小和频率,并要保证一定是直流耦合,否则实验结果出不来;3.要注意用到实验前找到的资料,大致了解芯片的特性,及如何连接,并在实验中运用。

【实验评价】在实验中,由于输入输出有与信号发生器、示波器、直流电源及地相接,接头很多接在一起,所以信号会有一些干扰,导致波形会有一些误差。

实验三三态门实验报告实验三三态门实验报告引言:在数字电路中,门电路是最基本的组成单元之一。

而三态门是一种特殊的门电路,它具有三种输出状态:高电平、低电平和高阻态。

本实验旨在通过实际搭建和测试三态门电路,深入了解其工作原理和应用。

一、实验目的本实验的主要目的是通过搭建和测试三态门电路,掌握其工作原理和特性。

具体目标如下:1. 理解三态门的概念和功能;2. 学会使用逻辑门芯片搭建三态门电路;3. 掌握三态门的输出状态和切换条件。

二、实验器材和仪器1. 逻辑门芯片:74LS125或74HC125;2. 面包板、导线等实验器材;3. 示波器、数字万用表等测量仪器。

三、实验原理三态门是一种具有三种输出状态的门电路,其输出可以是高电平、低电平或高阻态。

它通过控制输入端的使能信号来切换输出状态。

当使能信号为高电平时,三态门处于开启状态,输出与输入信号一致;当使能信号为低电平时,三态门处于关闭状态,输出为高阻态,即不对外输出信号。

四、实验步骤1. 将74LS125或74HC125逻辑门芯片插入面包板中,注意引脚与连接线的对应关系;2. 连接电源和地线,确保电路正常供电;3. 将输入信号接入逻辑门芯片的输入端,同时连接使能信号;4. 使用示波器或数字万用表等测量仪器,测试逻辑门芯片的输出信号;5. 调节输入信号和使能信号,观察三态门的输出状态变化。

五、实验结果与分析通过实验,我们得到了三态门的输出状态和切换条件。

当使能信号为高电平时,三态门处于开启状态,输出与输入信号一致;当使能信号为低电平时,三态门处于关闭状态,输出为高阻态。

这种特性使得三态门在数字电路设计中具有广泛的应用。

六、实验应用三态门在数字电路设计中有着重要的应用。

首先,它可以用于数据总线的连接和控制,实现多个设备之间的数据传输和共享。

其次,三态门还可以用于电路的隔离与保护,防止信号干扰和短路等问题。

此外,三态门还可以用于多路选择器和数据缓存等电路的设计与实现。

实验二(1)三态门电路设计

班级姓名学号

一、实验目的

熟悉QuartusII仿真软件的基本操作,并用VHDL/Verilog语言设计一个三态门。

二、实验内容

1、熟悉QuartusII软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)

2、用VHDL语言设计一个三态门,最终在FPGA芯片上编程指令译码器,并验证逻辑实现。

三、实验方法

1、实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

2、实验步骤:

1、新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设

置project name为stm)-【next】(设置文件名zlym.vhd—在【add】)-【properties】

(type=AHDL)-【next】(family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】

(2).新建:【file】-【new】(第二个AHDL File)-【OK】

2、写好源代码,保存文件(stm.vhd)。

3、编译与调试。

确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译。

编译结果有一个警告,文件编译成功。

4、波形仿真及验证。

新建一个vector waveform file。

按照程序所述插入EN,A以及dataout)四个节点(EN,A为输入节点,dataout为输出节点)。

(操作为:右击-【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】)。

任意设置EN,A的输入波形…点击保存按钮保存。

然后【start simulation】,出name dataout的输出图。

5、时序仿真。

暂时不知道什么是时序仿真

6、FPGA芯片编程及验证

选择pins,连接计算机到实验箱,操作。

四、实验过程

3、编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译。

编译结果有四个警告,文件编译成功。

c)结果分析及结论

结果正确,

4、波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

c)结果分析及结论

0-10ns:EN=0 A=0 dataout=z

10-20ns: EN=0 A=1 dataout=z

20-30ns: EN=1 A=1 dataout=1

30-40ns: EN=1 A=0 dataout=0

通过波形图可以得出实验结果正确

5、时序仿真

a)时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

b)时序仿真图

b)结果分析及结论

A引脚到dataout引脚的实际p2p时间为6.568ns,二EN引脚到dataout引脚的实际p2p时间为6,542ns。

A比EN慢0.026ns,可由于结果是由时间长的那个决定,故整体为6.568ns。

tpd (引脚到引脚的延时)

6、Programming芯片编程

a)芯片编程过程

写好代码和得到波形图后,【Assignments】-【Pins】-连接端口。

设置好两入一出(如Input: pin_87 Input: pin_88, Output: pin_06),从计算机连接数据线到EPF10K20TI144_4的FPGA 试验箱。

连接电源,开始按开关。

找到pin 87,88,06的位置,改变87,88的开关状态(开,开)、(关,开)、(开,关)、(关,关)。

看06灯的亮熄情况并记录。

b)编程芯片验证结果

0代表不灯亮,1代表灯亮。

c)结果分析与结论

由逻辑关系得的上述结果。

结果正确。

五、实验结论(实验总结与实验心得)

第二次实验使用这个软件明显熟练了,而且对时序仿真与波形仿真有了初步认识。

实验二(2)2选1多路复用器

班级计科1504 姓名张洁学号201508010402

一、实验目的

熟悉QuartusII仿真软件的基本操作,并用VHDL/Verilog语言设计一个三态门。

二、实验内容

1、熟悉QuartusII软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)

2、用VHDL语言设计一个2选1多路复用器,最终在FPGA芯片上编程指令译码器,并验证逻辑实现。

三、实验方法

7、实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

8、实验步骤:

2、新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设

置project name为exy)-【next】(设置文件名zlym.vhd—在【add】)-【properties】

(type=AHDL)-【next】(family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】

(2).新建:【file】-【new】(第二个AHDL File)-【OK】

2、写好源代码,保存文件(exy.vhd)。

3、编译与调试。

确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译。

编译结果有一个警告,文件编译成功。

4、波形仿真及验证。

新建一个vector waveform file。

按照程序所述插入EN,A[7].B[7]以及dataout[7])四个节点(EN,A[7],B[7]为输入节点,dataout为输出节点)。

(操作为:右击-【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】)。

任意设置EN,A的输入波形…点击保存按钮保存。

然后【start simulation】,出name dataout的输出图。

5、时序仿真。

暂时不知道什么是时序仿真

6、FPGA芯片编程及验证

选择pins,连接计算机到实验箱,操作。

四、实验过程

9、编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译。

编译结果有四个警告,文件编译成功。

c)结果分析及结论

结果正确,

10、波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

c)结果分析及结论

0-10ns:EN=0 dataout=B

10-20ns: EN=0 dataout=B

20-30ns: EN=1 dataout=A

30-40ns: EN=1 dataout=A

通过波形图可以得出实验结果正确

10、时序仿真

c)时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

b)时序仿真图

d)结果分析及结论

EN引脚到dataout引脚的实际p2p时间比A,B引脚到dataout引脚的实际p2p时间长。

由于结果是由时间长的那个决定,故整体为9.726ns。

tpd (引脚到引脚的延时)

11、Programming芯片编程

b)芯片编程过程

写好代码和得到波形图后,【Assignments】-【Pins】-连接端口。

设置好三入一出(如Input:

pin_87 Input: pin_88,Input: pin_89 Output: pin_06),从计算机连接数据线到EPF10K20TI144_4的FPGA试验箱。

连接电源,开始按开关。

找到pin 87,88,06的位置,改变87,88,89的开关状态。

看06灯的亮熄情况并记录。

b)编程芯片验证结果

0代表不灯亮,1代表灯亮。

c)结果分析与结论

由逻辑关系得的上述结果。

结果正确。

五、实验结论(实验总结与实验心得)

这一次的实验题目相比较来说比较简单易懂,而且在前面实验做铺垫的情况下,做起来比较顺手。

感觉自己有了一点进步。