基于FPGA的高速图像采集/处理卡

- 格式:pdf

- 大小:138.29 KB

- 文档页数:2

刘斌兵刘云海汪燮彬中国船级社规定从2004年开始,在国内和国际航行的船舶中都必须安装船载航行数据记录仪,其中船载雷达图像记录仪是很重要的一部分。

船载雷达图像按VGA图像标准输出,其分辨率在640×480~1280×1024之间,刷新率在60~85Hz之间。

目前常见的图像采集系统多是针对复合视频信号的采集,或者是针对CCD图像信号的采集。

这些图像采集系统并不能满足雷达图像采集的要求。

即使少数针对高分辨率高刷新率图像的采集系统也是以计算机板卡的形式出现,运行时需要一台计算机。

目前一些速度高达1GSPS的基于VME总线的数据采集系统,通过4路,每路采集速度高达250MHz的系统实现1GSPS速度的数据采集。

但由于该类系统中没有大容量的数据缓存,因此并不能实现高速长时间的数据采集。

另外一些系统采用一种基于FPGA,使用多SDRAM作为数据缓存的采集系统。

该类系统解决了长时间高速采集的问题,可以对频率为100MHz,16bit位宽的数据进行采集。

但是由于它采用了多个FIFO来降低SDRAM的工作频率,使得该类系统应用在需要严格的数据同步的高速图像采集系统中会出现一些数据难以同步的问题。

还有一种PC板卡形式的高分辨率图像采集卡,该系统直接对图像进行压缩后存储,并通过PCI接口提供给PC,但这种形式既不适合船舶上狭小的空间,也不能满足船舶失事时对数据的保护要求。

本文提出一种高分辨率高刷新率图像采集系统。

该系统使用于嵌入式系统中,不仅体积小,还解决了数据保护的问题,可用于船载雷达图像记录系统。

该系统可支持对多达4路8bit位宽最高采样率达120MHz的数据通道,或者一路VGA图像信号,可对采集数据进行长时间采集存储。

具体的连续采集时间根据系统所采用的SDRAM容量大小有所变化。

该系统还为数据的后续处理提供了ASRAM接口,使得用于缓存数据的SDRAM也可作为后续处理CPU的系统内存。

这样既可以提高速据的处理速度,方便后续针对雷达图像的压缩或者识别处理,也节省了资源。

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

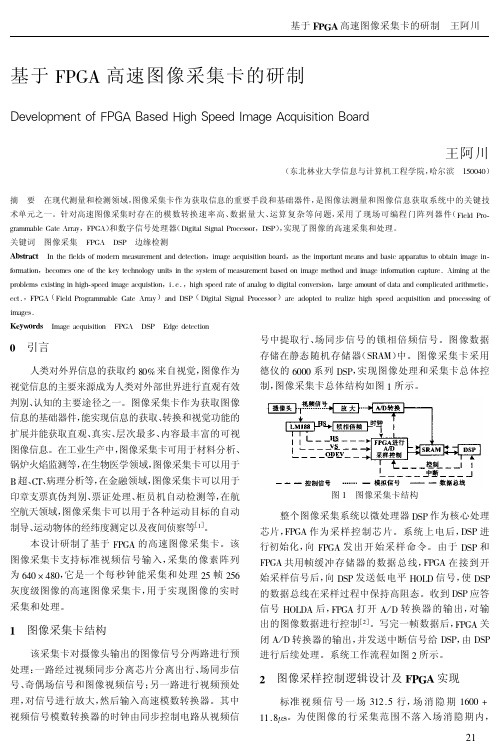

基于FPGA高速图像采集卡的研制Development of FPGA Ba ed High Speed lmage Acqui ition Board王阿川(东北林业大学信息与计算机工程学院,哈尔滨150040)摘要在现代测量和检测领域,图像采集卡作为获取信息的重要手段和基础器件,是图像法测量和图像信息获取系统中的关键技术单元之一。

针对高速图像采集时存在的模数转换速率高、数据量大、运算复杂等问题,采用了现场可编程门阵列器件(Field Pro-grammable Gate Array,FPGA)和数字信号处理器(Digital Signal Processor,DSP),实现了图像的高速采集和处理。

关键词图像采集FPGA DSP边缘检测Abstract In the fields of modern measurement and detection,image acquisition board,as the important means and basic apparatus to obtain image in-formation,becomes one of the key technology units in the system of measurement based on image method and image information capture.Aiming at the problems existing in high-speed image acquistion,i.e.,high speed rate of analog to digital conversion,large amount of data and complicated arithmetic,ect.,FPGA(Field Programmable Gate Array)and DSP(Digital Signal Processor)are adopted to realize high speed acquisition and processing of images.Keywords Image acquisition FPGA DSP Edge detection0引言人类对外界信息的获取约80%来自视觉,图像作为视觉信息的主要来源成为人类对外部世界进行直观有效判别、认知的主要途径之一。

基于FPGA的高速视频图像处理技术第一章:引言在当前日益发展的信息时代,视频图像处理技术越来越受到人们的关注。

这种技术能够对图像进行基本的处理和分析,通过深度学习,可以实现人脸识别、物体识别、场景分析等应用。

为了实现高速、高效的视频图像处理,FPGA(现场可编程门阵列)是一个很好的选择。

本文介绍基于FPGA的高速视频图像处理技术。

第二章:视频图像处理技术视频图像处理技术是一种将数字信号处理技术应用于图像处理的方法。

该技术主要包括数字图像处理、数字视频处理和图像传感。

其中,数字图像处理是指将数字信号的理论、原则和方法应用于图像分析、处理和识别;数字视频处理是指将数字信号处理技术应用于视频信息处理等;图像传感是指利用传感器的多个元素来采集图像,并将其转换为数字信息。

第三章:FPGA技术的优势FPGA是一种硬件可编程的数字电路系统,它的内部结构由一些可编程逻辑器件、内部存储器和I/O接口等组成。

有以下几个优势:1. 可编程性:FPGA可以按照用户的需求进行编程,可以用来实现不同种类的电路设计。

2. 灵活性:FPGA可以根据用户的需求进行实现,能够灵活地进行硬件资源配置,可以快速响应市场变化。

3. 高性能:FPGA能够实现基于硬件的图像处理算法,具有高速、高性能和低功耗等优点。

第四章:利用FPGA进行视频图像处理的原理FPGA可以实现以定制的方式设计和实现特定任务的图像处理算法。

视频图像处理的主要任务之一是图像的滤波,可以利用FPGA的低延迟和高性能来实现。

滤波算法通常使用块匹配和运动估计技术,以实现减少噪声和增强图像的目的。

另外,FPGA还可以用于实现数字信号处理(DSP)。

DSP是一种数字信号处理技术,可以在数字信号处理链的某个位置,以实现滤波、FFT、卷积、乘法、除法等功能。

DSP通常具有高精度、低功耗、高速率等特点。

利用FPGA进行视频图像处理的原理主要在于,将DSP应用于视频图像处理领域,以实现减少噪声和增强图像的目的。

基于FPGA的增强型图像采集处理系统的设计与实现基于FPGA的增强型图像采集处理系统的设计与实现摘要:本文基于FPGA技术,设计并实现了一种增强型图像采集处理系统。

该系统采用了Xilinx公司的FPGA芯片作为主控芯片,并根据图像采集处理的需求设计了相应的硬件电路。

通过该系统,能够对图像进行高效、准确的采集和处理,提高了图像处理的实时性和稳定性,具有较高的应用价值。

关键词:FPGA;图像采集处理;实时性;稳定性一、引言图像采集和处理是计算机视觉领域的重要研究方向之一。

在很多应用中,如医学影像分析、机器视觉、安防监控等,需要对图像进行实时采集和处理,以提取图像的有效信息。

然而,传统的图像采集与处理系统存在一些缺陷,如处理速度慢、实时性差、稳定性差等。

因此,设计一种基于FPGA的增强型图像采集处理系统具有重要的研究价值。

二、系统设计1. 系统架构本文设计的增强型图像采集处理系统主要包括两个模块:图像采集模块和图像处理模块。

其中,图像采集模块用于获取外部图像信号,并将其转换为数字信号输入到FPGA芯片中。

图像处理模块负责对采集到的图像进行处理,并输出处理结果。

2. 图像采集模块设计图像采集模块的设计基于FPGA芯片集成的高速ADC模块。

该模块能够将外部模拟信号转换为数字信号,并通过FPGA芯片的接口输入到系统中。

为保证采集的图像数据质量,我们选择了高分辨率、低噪声的ADC芯片,并根据系统需求进行了适当的配置。

3. 图像处理模块设计图像处理模块的设计主要包括图像预处理和图像算法两个部分。

图像预处理主要包括图像去噪、图像增强、图像滤波等处理方法,用于提取图像的有效信息。

图像算法部分根据具体应用需求设计,如图像分割、边缘检测、目标识别等。

为了提高系统的实时性,我们采用了流水线处理的方式,将多个处理步骤并行进行,减少了处理时间。

三、系统实现1. FPGA芯片编程本文选择了Xilinx公司的FPGA芯片作为主控芯片。

基于FPGA的图像采集处理系统在现代科技领域,特别是计算机视觉和机器学习领域,图像采集和处理已经成为一项至关重要的任务。

在许多应用中,需要快速、准确地对图像进行处理,这推动了图像采集和处理系统的研究和发展。

现场可编程门阵列(FPGA)作为一种可编程逻辑器件,具有并行处理能力强、功耗低、可重构等优点,使其成为构建高性能图像采集处理系统的理想选择。

FPGA是一种可通过编程来配置其硬件资源的集成电路,它由大量的可配置逻辑块、内存块和输入/输出块组成。

这些逻辑块和内存块可以在FPGA上被重新配置,以实现不同的逻辑功能和算法。

输入/输出块可以用于与外部设备进行通信。

基于FPGA的图像采集处理系统通常包括图像采集、预处理、传输、主处理和输出等几个主要环节。

这个阶段主要通过相机等设备获取图像数据。

相机与FPGA之间的接口可以是并行的,也可以是串行的。

并行接口通常传输速度更快,但需要更多的线缆;串行接口则使用更少的线缆,但传输速度可能较慢。

这个阶段主要是对采集到的原始图像数据进行初步处理,如去噪、灰度化、彩色化等。

这些处理任务可以在FPGA上并行进行,以提高处理速度。

经过预处理的图像数据需要通过接口或总线传输到主处理单元(通常是CPU或GPU)进行处理。

在传输过程中,可以使用DMA(直接内存访问)技术,以减少CPU的负载。

在这个阶段,主处理单元(通常是CPU或GPU)会对传输过来的图像数据进行复杂处理,如特征提取、目标检测、图像识别等。

这些处理任务需要大量的计算资源和算法支持。

处理后的图像数据可以通过接口或总线传输到显示设备或用于进一步的处理。

基于FPGA的图像采集处理系统具有处理速度快、可重构性强、功耗低等优点,使其在许多领域都有广泛的应用前景。

特别是在需要实时图像处理的场景中,如无人驾驶、机器视觉等,基于FPGA的图像采集处理系统将具有更高的性能和效率。

随着FPGA技术和相关算法的发展,我们可以预见,基于FPGA的图像采集处理系统将在未来得到更广泛的应用和推广。

基于FPGA的高速图像采集处理系统设计与实现近年来,随着科技的不断进步,数字图像采集技术也迎来了一次腾飞。

作为一种高效、稳定的图像采集技术,基于FPGA的高速图像采集处理系统被广泛应用于视频监控、医学影像、工业检测等领域。

本文将详细介绍基于FPGA的高速图像采集处理系统的设计与实现过程,包括硬件平台的搭建、图像采集核心模块的设计与实现,以及数据传输与存储等相关内容。

一、硬件平台搭建硬件平台是基于FPGA进行设计的核心环节,同时也是决定整个系统性能的重要因素。

我们选用了Xilinx公司的Zynq系列SoC(System on Chip)作为硬件平台,该芯片结合了高性能的ARM Cortex-A9处理器和可编程逻辑门阵列(FPGA),能够提供很高的计算性能。

同时,该系列SoC还具备高速串行接口和DMA控制器,能够实现高速数据传输与存储。

在硬件平台搭建过程中,我们需要先将SoC与外部存储芯片、高速采集器等外设连接。

为了保证系统的稳定性和可靠性,我们还需要添加适当的电源管理模块、时钟管理模块和温度控制模块。

最后,我们将通过Vivado软件对硬件平台进行初始化和配置,以保证系统的正常运行。

二、图像采集核心模块的设计与实现图像采集核心模块是基于FPGA进行设计的重要模块,主要用于快速采集输入信号,并将其转换为数字信号进行后续的图像处理。

该模块的性能直接影响到整个系统的速度和稳定性,因此需要在设计时充分考虑系统需求和硬件资源。

我们选用了LVDS差分信号传输技术作为图像采集的接口方式,该技术具有低噪声、抗干扰性强等优点,可以保证高质量的图像采集。

同时,我们还采用了FPGA内部的片上ADC(Analog to Digital Converter)模块,能够实现快速、高精度的信号采集。

为了保证信号的稳定性和减小信号处理延迟,我们还采用了FPGA内部的DMA(Direct Memory Access)控制器,实现高速数据传输和转换。

Xilinx Kintex-7系列FPGA高速采集卡中文资料基于Xilinx Kintex-7 FPGA,XC7K160/325/410T FBV676可选,DDR3 256MB/512MB可选。

NOR FLASH 256Mb,可根据开发需求自搭配,成本可控;工业级FMC连接器,支持高速ADC和DAC等FMC标准模块;PCI Express 标准,提供PCIe x2高速数据传输接口,单通道通信速率可高达5GBaud; Serial Rapid I/O,提供SRIO x2高速数据传输接口,单通道通信速率可高达5GBaud;SFP+光纤接口,传输速率可高达10Gbit/s;集成千兆网及I2C等常见接口,拓展能力强;提供板卡原理图和丰富的开发例程,入门简单。

图 1 Xilinx Kintex-7 FPGA基本参数图 2 TL-K7FMC采集卡正面图图 3 TL-K7FMC采集卡侧视图1图 4 TL-K7FMC采集卡侧视图2图 5 TL-K7FMC采集卡侧视图3图 6 TL-K7FMC采集卡侧视图4TL-K7FMC采集卡是一款广州创龙基于Xilinx Kintex-7系列FPGA自主研发的FMC数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。

TL-K7FMC采集卡完全支持PCI Express 标准,串行高速输入输出SRIO总线通过HDMI接口提供稳定、可靠的高速传输能力,为产品的快速成型提供极大的便利。

TL-K7FMC采集卡的FMC接口不仅简化了I/O接口模块设计,提供高速的接口通信能力,而且提高了模块的利用率,标准化设计使产品有更好的通用性。

1 典型运用领域高速数据采集系统音视频数据处理系统图像处理设备软件无线电设备通信系统高精度仪器仪表高端数控系统 2 软硬件参数硬件参数ASP-134488-01400PINArrayEEPROMAT24C02SPIFLASHCDCM61002RESETDDR3Kintex-7Xilinx 7 seriesSerial Rapid IO x2PCIE GEN2 x4Kintex-XADCSFP+28nm Technology Low Cost FPGAOSC25MHzUART图 7 TL-K7FMC采集卡硬件框图JTAGPHYLED710-1100-304848PIN图 8 TL-K7FMC硬件资源图解1图 9 TL-K7FMC硬件资源图解2表1CPU RAM ROM EEPROM 网络 Xilinx Kintex-7 FPGA,XC7K160/325/410T FBV676 256MByte/512MByte DDR3 256MBit NOR FLASH 2KBit 10/100/1000M ETHERNET光纤接口 LED 3x 可编程指示灯 1x 复位按键按键 2x 用户可编程按键 1x SRIO TX,1x SRIO RX,2通道,单通道最高速率5GBaud,HDMI座 1x PCIe 4x(Gen2),2通道,单通道最高通信速率5GBaud 2x 48pin欧式连接器,GPIO拓展拓展IO 1x I2C,HDMI座 1x PMOD 1x XADC 1x FMC,400pin 仿真器接口启动方式串口电源开关电源接口 1x 14pin JTAG接口,间距 1x 2bit启动方式选择拨码开关 1x UART,Micro USB接口,提供4针TTL电平测试端口 1x 电源拨码开关 1x 12V 2A直流输入DC005电源接口,外径,内径 1x SFP+ 1x 供电指示灯软件参数表 2 Vivado版本号 3 开发资料提供采集卡原理图、入门教程、丰富的Demo程序;提供与DSP通信教程,完美解决DSP+FPGA异构平台通信开发瓶颈;提供完整的软件开发包,以及配套的开发文档。

基于FPGA器件EP2C5F256C6芯片实现图像采集系统的应用方案引言在低速的数据采集系统中,往往采用单片机或者 DSP进行控制;而对于图像采集这种高速数据采集的场合,这种方案就不能满足需要。

因此这种方案极大浪费了单片机或DSP的端口资源且灵活性差;若改用串口方式收集数据,则一方面降低了数据采集的速度,另一方面极大地耗费CPU的资源。

本系统采用FPGA作为数据采集的主控单元,全部控制逻辑由硬件完成,速度快、成本低、灵活性强。

为了增加缓冲功能,系统在FPGA外扩展了256Mb的RAM,不仅增大了缓冲区容量,而且极大地降低了读写频率,有效地减轻了上位机CPU的负担。

在图像数据接口中,比较常见的是VGA、PCI—Express,而这些接口扩展性差、成本高。

本系统采用高速的USB接口作为与上位机通信的端口,速度快、易安装、灵活性强。

1 系统框图系统框图如图1所示。

FPGA控制单元采用 A1tera公司Cyclone II系列的EP2C5F256C6,主要由4个部分组成——主控模块、CMOS传感器接口、RAM控制器以及EZ—USB接口控制器。

传感器接口负责完成 SCCB时序控制,RAM控制器用于实现RAM读写与刷新操作的时序,USB接口模块完成主控模块与EZ—USB之间的数据读写;而主控模块负责对从EZ —USB部分接收过来的上位机命令进行解析,解析完命令后产生相应的信号控制各个对应模块,如CMOS传感器传输的图像格式、RAM的读写方式、突发长度等。

2 OV7620模块设计图像传感器采用OV7620,接口图如图2所示。

该传感器功能强大,提供多种数据格式的输出,自动消除白噪声,白平衡、色彩饱和度、色调控制、窗口大小等均可通过内部的SCCB控制线进行设置。

OV7620属于CMOS彩色图像传感器。

它支持连续和隔行两种扫描方式,VGA与QVGA两种图像格式;最高像素为664×492,帧速率为30fps;数据格式包括YUV、YCrCb、RGB三种。