AMD_NV芯片组上电时序详细解说

- 格式:pdf

- 大小:1.46 MB

- 文档页数:15

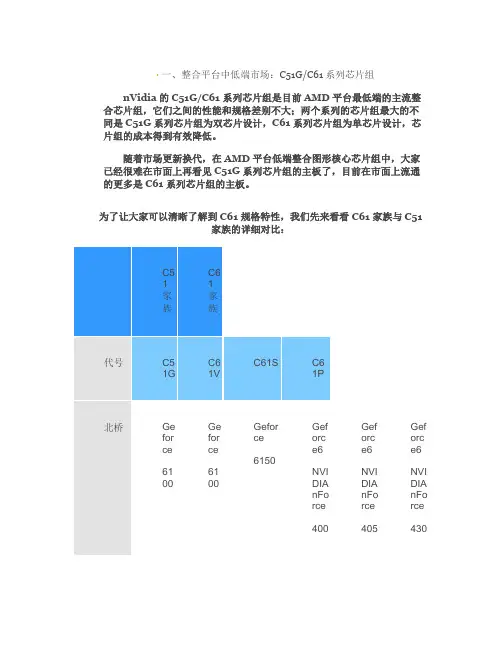

∙一、整合平台中低端市场:C51G/C61系列芯片组nVidia的C51G/C61系列芯片组是目前AMD平台最低端的主流整合芯片组,它们之间的性能和规格差别不大;两个系列的芯片组最大的不同是C51G系列芯片组为双芯片设计,C61系列芯片组为单芯片设计,芯片组的成本得到有效降低。

随着市场更新换代,在AMD平台低端整合图形核心芯片组中,大家已经很难在市面上再看见C51G系列芯片组的主板了,目前在市面上流通的更多是C61系列芯片组的主板。

为了让大家可以清晰了解到C61规格特性,我们先来看看C61家族与C51家族的详细对比:Gef orc e6NVI DIA nFo rce405Gef orc e6NVI DIA nFo rce430nF orc e 41 0nForce43nForce430---42 5425475425425475支持支持支持支持支持支持否否是否否否否否是否否是1x16X 1x1X 1x16X1x1X1x16X2x1X-2x1X1x8X2x1X1x16X2x1X标清标清高清1080p/1080i标清标清标清标准2x 2 标准2x2高品质5x4标准2x2标准2x2标准2x22/44/44/42/22/24/23.0GB/s0、10、1、0+1、50、1、0+1、50、10、10、1、0+1、5百兆千兆千兆百兆百兆千兆支持支持根据NVIDIA官方说明,C61将分成P、S、V三个型号,分别是Premium(加强型、Standard(标准型和Value(经济型的简写,同时可针对不同用户的使用需求。

其中C61的图形核心将继续沿用Geforce6100,规格特性当然也没有变动:90nm制程、支持DirectX 9.0c和Shader Model 3.0,拥有两条像素渲染管线、1个定点处理器,最大可共享256M系统内存,植入南桥后的Geforce6100性能可能有所削弱。

(其中C61系列的图形核心频率一直存在争议,较早前我们收到相关信息C61V/61S的默认频率是375MHz而C61P的频率是425MHz,但经NVIDIA官方证实后C61V/S频率为425MHz而C61P频率为475MHz,不过目前市面上产品并非完全按照这个标准,有些偏高有些偏低,所幸的是,作为低端整合图形核心的芯片组,其图形核心的频率高低对游戏性能无关痛痒,因此我们也无需对其追究太多。

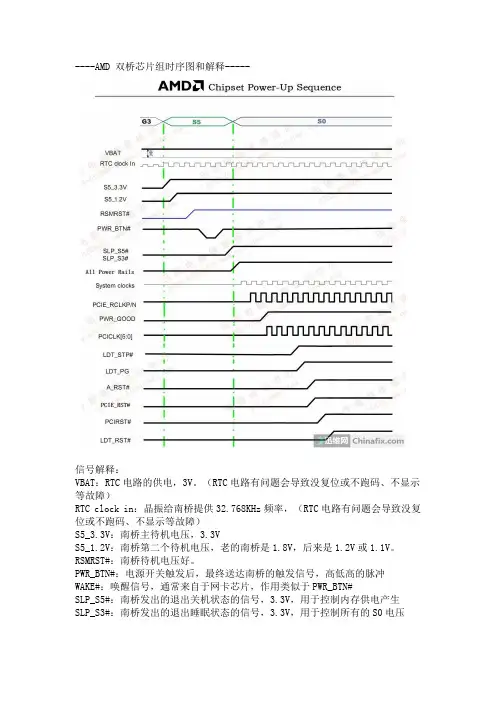

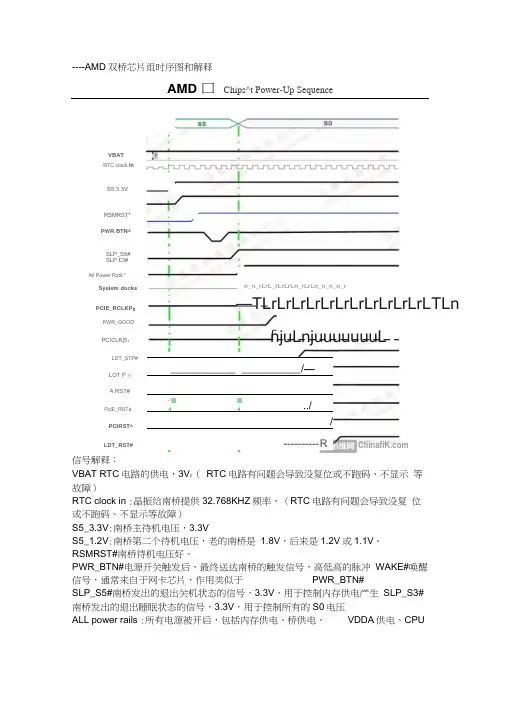

----AMD 双桥芯片组时序图和解释-----信号解释:VBAT:RTC电路的供电,3V。

(RTC电路有问题会导致没复位或不跑码、不显示等故障)RTC clock in:晶振给南桥提供32.768KHz频率,(RTC电路有问题会导致没复位或不跑码、不显示等故障)S5_3.3V:南桥主待机电压,3.3VS5_1.2V:南桥第二个待机电压,老的南桥是1.8V,后来是1.2V或1.1V。

RSMRST#:南桥待机电压好。

PWR_BTN#:电源开关触发后,最终送达南桥的触发信号,高低高的脉冲WAKE#:唤醒信号,通常来自于网卡芯片,作用类似于PWR_BTN#SLP_S5#:南桥发出的退出关机状态的信号,3.3V,用于控制内存供电产生SLP_S3#:南桥发出的退出睡眠状态的信号,3.3V,用于控制所有的S0电压ALL power rails:所有电源被开启,包括内存供电、桥供电、VDDA供电、CPU 供电、总线供电等。

System clocks:时钟芯片开始工作PCIE_RCLKP/N:时钟芯片送给南桥的100M差分时钟对,作为南桥的主时钟信号PWR_GOOD:通知南桥,此时S0状态电压全部OKPCICLK[5:0]:南桥发出PCI时钟NB_PWRGD:南桥发出给北桥的电源好信号,悬空或连接北桥的POWERGOOD脚。

南桥内部集成了一个完整的时钟模块,如果不启用南桥集成的时钟模块,而使用外置时钟芯片,NB_PWRGD可以不采用,只需要把北桥的POWERGOOD连接到南桥的PWR_GOOD,即南北桥同时得到PG。

如果启用南桥集成的时钟模块,不使用外置时钟芯片,南桥在收到PWR_GOOD后需要延时39ms,才会发出NB_PWRGD给北桥。

延时的目的是为了等待南桥内部的时钟模块工作稳定。

LDT_STP#:南桥发给CPU的高电平,由内存供电上拉。

通知CPU退出停止状态。

LDT_PG:南桥发出给CPU的电源好,由内存供电上拉。

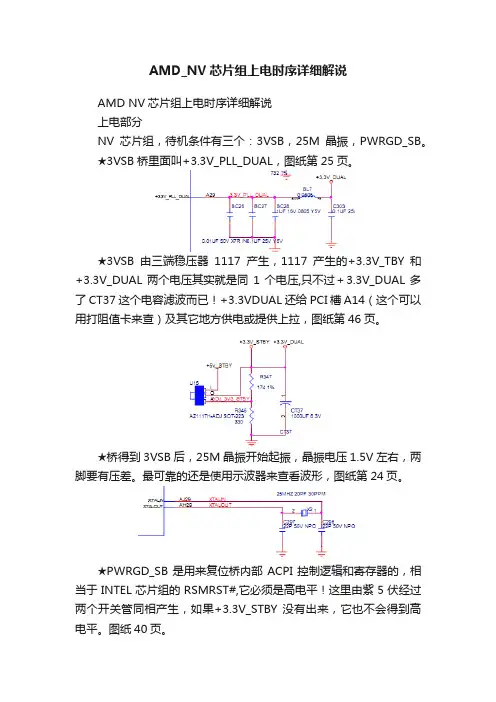

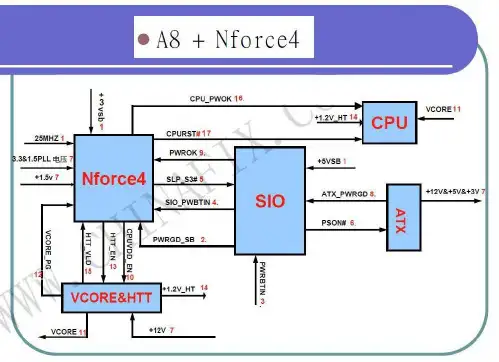

AMD_NV芯片组上电时序详细解说AMD NV芯片组上电时序详细解说上电部分NV芯片组,待机条件有三个:3VSB,25M晶振,PWRGD_SB。

★3VSB桥里面叫+3.3V_PLL_DUAL,图纸第25页。

★3VSB由三端稳压器1117产生,1117产生的+3.3V_TBY和+3.3V_DUAL两个电压其实就是同1个电压,只不过+3.3V_DUAL多了CT37这个电容滤波而已!+3.3VDUAL还给PCI槽A14(这个可以用打阻值卡来查)及其它地方供电或提供上拉,图纸第46页。

★桥得到3VSB后,25M晶振开始起振,晶振电压1.5V左右,两脚要有压差。

最可靠的还是使用示波器来查看波形,图纸第24页。

★PWRGD_SB是用来复位桥内部ACPI控制逻辑和寄存器的,相当于INTEL芯片组的RSMRST#,它必须是高电平!这里由紫5伏经过两个开关管同相产生,如果+3.3V_STBY 没有出来,它也不会得到高电平。

图纸40页。

★至此桥的待机条件已查完,下面看看它的触发电路,从开关开始查,图纸第42页。

开关16脚经过R333电阻接地,15脚信号名字叫PWRBTN*。

★PWRBTN*由R305电阻提供上拉连到IO(IT8716FCX)75脚,未触发开关之前为5伏。

触发开关后,IO75脚得到低电平跳变,此时IO本身供电正常,则从72脚发出低电平跳变到桥。

图纸34页。

跳变电压我们都用示波器来测量。

★桥待机条件满足,然后收到IO发过来的低电平跳变,将依次置高SLP_S5#,SLP_S4#,SLP_S3#。

其中SLP_S3#一路返回IO71脚,IO收到SLP_S3#高电平后,76脚由高电平变为低电平去拉低电源绿线完成上电,图纸34页。

★至此主板的上电已完成,ATX发出VCC3、VCC、+12V等主供电,最后延迟几百毫秒从灰线发出ATXPWOEROK信号,高电平。

◆需要注意的是,CMOS电路有问题,一般不会引起不上电,但会导致不跑码。

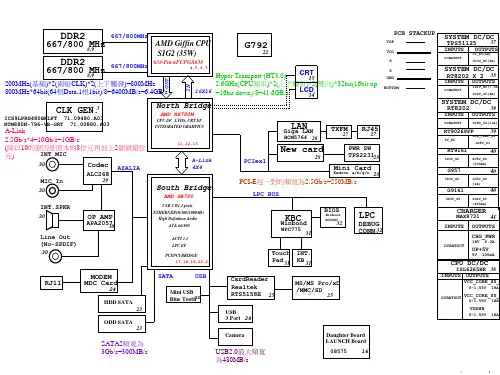

▪Dept.:▪By :Jeff.Ko7▪Date:2010/6/913VCORE 14FET SB_PWOK A TX power AM2IT8716 GB/CX Power button MCP61MCP61-PWRBTSW PWOK CK8_PWOK -PSOUT CPUPWROK -CPURST 5VSB 5VDUAL -RSMRST FET 14-SLP_S3PWM CPUVDD_EN 1121S5_EN Circuit 3VDUAL W83303AG FET S5_EN -SLP_S5SB_PWOK Circuit VCC12_DUAL W83303AG CPU_VLD VCORE_PWOK -IO_PSON -ATX_PSON MEM_VLD VID HT VREG HT1VDD_EN HT1_VLD 25MHz 5689107Core Power Planes 1216171932KHz CPUCLK0_H/L -LPCRST 2023315VCC12DDR18V DDRVTT VCORE DDR18V DDRVTT VCC12_HT VCC12_HT 18VDDA25VCC12 VCC12_HT 2P5V_PWR VCC3VCC3 VCC15 VCC15_DUAL VCC VCC12 VCC VDDA25GA-M61PM-S2 Power Sequencing CIRCUIT 2N7002▪▪▪AM2 Power-Up Sequence+3.0V_VBAT+5V_DUAL+3.3V_DUAL+1.5V_DUAL25MHz xtalPWRGD_SB+2.5V_SUS+1.25V_VTT_SUSCOREPowerPlanesSUSCLK(32KHz)CPUVDD_ENCPU_VLDHTVDD_EN+12V_HTSLP_S5#MEM_VLDSLP_S3#PWRGDCPU_CLKLPC_CLK+V_CPUHT_VLDLPC_PD#ITE8282M讲解一:ITE8282M初识●ITE8282M是联阳半导体公司生产的一颗用于K8CPU平台的增强型时序控制器。

----AMD 双桥芯片组时序图和解释AMD 口 Chips^t Power-Up Sequence信号解释:VBAT RTC 电路的供电,3V 0( RTC 电路有问题会导致没复位或不跑码、不显示 等故障)RTC clock in :晶振给南桥提供32.768KHZ 频率,(RTC 电路有问题会导致没复 位或不跑码、不显示等故障)S5_3.3V :南桥主待机电压,3.3VS5_1.2V :南桥第二个待机电压,老的南桥是 1.8V ,后来是1.2V 或1.1V 。

RSMRST#南桥待机电压好。

PWR_BTN#电源开关触发后,最终送达南桥的触发信号,高低高的脉冲 WAKE#唤醒信号,通常来自于网卡芯片,作用类似于 PWR_BTN#SLP_S5#南桥发出的退出关机状态的信号,3.3V ,用于控制内存供电产生 SLP_S3#南桥发出的退出睡眠状态的信号,3.3V ,用于控制所有的S0电压 ALL power rails :所有电源被开启,包括内存供电、桥供电、 VDDA 供电、CPUVBATn_n_rLrL_rLrLrLn_rLrLn_n_n_n_r—TLrLrLrLrLrLrLrLrLrLrLrLTLn___________ __________ /—-■ ■ 1 1..//---------- RRTC clock InS5.3.3VRSMRST*;PWR BTN^All Power Rztil.*Syslem docks PCIE_RCLKP ;NPWR_GOODnjuLnjuuuuuuuLPCICLK[5:Q]LDT_STP#A RST#PciE_RSTaPCIRST^ LDT_RST#SLP_S5# SLP £3#LOT P 右供电、总线供电等。

System clocks :时钟芯片开始工作PCIE_RCLKP/N时钟芯片送给南桥的100M差分时钟对,作为南桥的主时钟信号PWR_GO O D1知南桥,此时S0状态电压全部0KPCICLK[5: 0]:南桥发出PCI时钟NB—PWRGDS桥发出给北桥的电源好信号,悬空或连接北桥的POWERGO脚D 南桥内部集成了一个完整的时钟模块,如果不启用南桥集成的时钟模块,而使用外置时钟芯片,NB_PWRGD以不采用,只需要把北桥的POWERGOO接到南桥的PWR_GOO即南北桥同时得到PG如果启用南桥集成的时钟模块,不使用外置时钟芯片,南桥在收到PWR_GOOD需要延时39ms才会发出NB_PWRGD北桥。

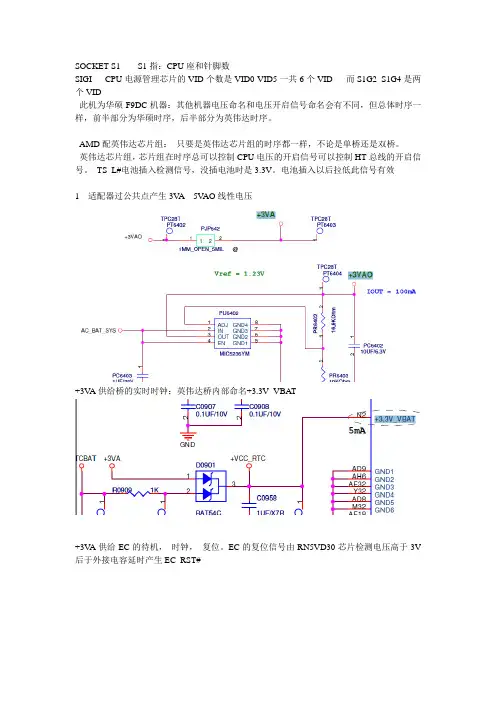

SOCKET S1 S1指:CPU座和针脚数SIGI CPU电源管理芯片的VID个数是VID0-VID5一共6个VID 而S1G2_S1G4是两个VID此机为华硕F9DC机器:其他机器电压命名和电压开启信号命名会有不同,但总体时序一样,前半部分为华硕时序,后半部分为英伟达时序。

AMD配英伟达芯片组:只要是英伟达芯片组的时序都一样,不论是单桥还是双桥。

英伟达芯片组,芯片组在时序总可以控制CPU电压的开启信号可以控制HT总线的开启信号。

TS_L#电池插入检测信号,没插电池时是3.3V。

电池插入以后拉低此信号有效1 适配器过公共点产生3V A 5V AO线性电压+3V A供给桥的实时时钟:英伟达桥内部命名+3.3V_VBAT+3V A供给EC的待机,时钟,复位。

EC的复位信号由RN5VD30芯片检测电压高于3V 后于外接电容延时产生EC_RST#+3V A要供给BIOS, EC在BIOS中读取数据,在BIOS程序配置正常后,EC发出VSUS_ON 待机电压开启信号,开启12VSUS。

更名RUN_3VO和RUN_5VO开启待机电压的3VSUS 5VSUS 开启1.2VSUS。

+12VSUS和+1.2VSUS都是通过线性电压芯片产生。

SUS电压供给英伟达的桥ACPI里面的待机电压:3V待机电压+3.3V_DUAL 还需要1.2V 的待机电压,桥内部命名:+1.2V_DUAL待机电压好以后TPS51020会发出一个待机电压好信号叫VUSU_GD给EC,EC再发出PWRGD_SB给桥英伟达的桥RSMRST#信号就叫PWRGD_SB至此整个待机条件满足。

PWRGD:电源好。

SB:待机.按开机键:PWR_SW#开机触发信号加给EC,EC收到信号且BIOS程序配置正常后发出PM_PWRBTN#给桥的PWRBTN#脚, 如果EC没有发出PWRBTN#信号要考虑ACIN 电池电量低。

LID_SW#休眠开关信号。

桥发出SP_S5#更名PM_SUSC#给EC ,EC发出SUSC#后更名SUSC#_PWR开启+1.8V 1,8V是内存电压,还有内存VTT0.9V,,开启场管转换+3V +5V +12V 和内存电压正常后发出MEM_VLD内存电压电源好信号给桥,此机器内存电压MEM_VLD不是由电源芯片产生而是由下面这个检测电路产生,其中NPN三极管的导通条件是G大于S 0.8V就可以导通。

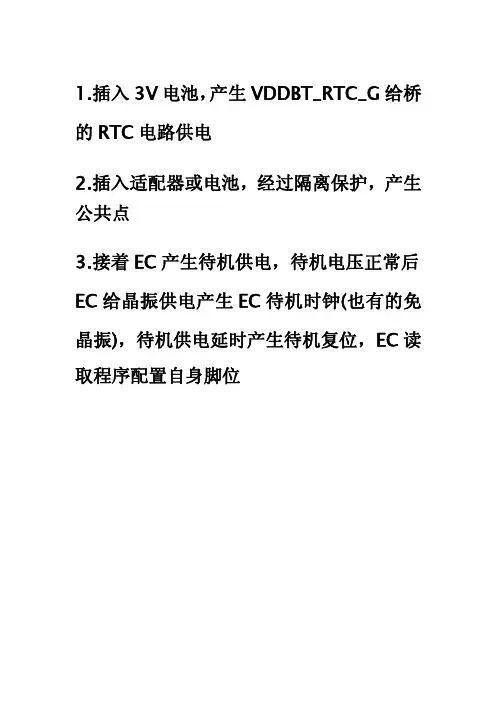

1.插入3V电池,产生VDDBT_RTC_G给桥的RTC电路供电

2.插入适配器或电池,经过隔离保护,产生公共点

3.接着EC产生待机供电,待机电压正常后EC给晶振供电产生EC待机时钟(也有的免晶振),待机供电延时产生待机复位,EC读取程序配置自身脚位

4.如果EC检测到适配器,会自动发出信号开启桥的待机供电(VDDIO_33_S,VDDCR_11_S)然后发给桥RSMRST#通知桥待机电压正常,如果EC检测不到适配器(电池模式),EC需要收到开关触发信号后,才会开启桥待机供电,以节省电力

5.按下开关,EC收到高-低-高跳变,并送给桥的PWRBTN#脚

6.桥的待机条件正常且收到PWRBTN#信号后,依次拉高SLP_S5#,SLP_S3#

7.SLP_S5#控制产生内存主供电,SLP_S3#控制产生桥供电(二级电压3.3V/5V/1.5V/1.1V)CPU多个供电

8.各路供电正常后,最终汇总产生PWR_GOOD给桥

9.桥供电,PWR_GOOD,25M晶振都正常后,先发出时钟

10.桥再发出APU_PG(LDT_PG)给CPU{这就是CPU_RESET#}

11.桥发出平台复位A_RST#,PCIE_RST#,PCIRST#(一般不采用)

12.桥发出APU_RST#(LDT_RST#)给CPU。

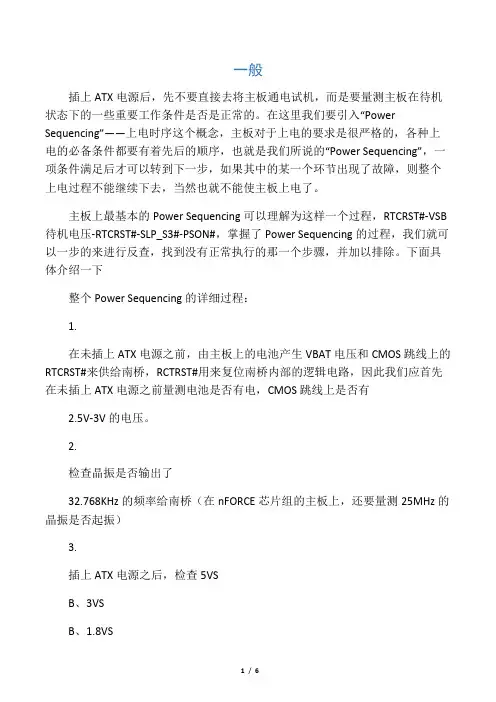

一般插上ATX电源后,先不要直接去将主板通电试机,而是要量测主板在待机状态下的一些重要工作条件是否是正常的。

在这里我们要引入“Power Sequencing”——上电时序这个概念,主板对于上电的要求是很严格的,各种上电的必备条件都要有着先后的顺序,也就是我们所说的“Power Sequencing”,一项条件满足后才可以转到下一步,如果其中的某一个环节出现了故障,则整个上电过程不能继续下去,当然也就不能使主板上电了。

主板上最基本的Power Sequencing可以理解为这样一个过程,RTCRST#-VSB 待机电压-RTCRST#-SLP_S3#-PSON#,掌握了Power Sequencing的过程,我们就可以一步的来进行反查,找到没有正常执行的那一个步骤,并加以排除。

下面具体介绍一下整个Power Sequencing的详细过程:1.在未插上ATX电源之前,由主板上的电池产生VBAT电压和CMOS跳线上的RTCRST#来供给南桥,RCTRST#用来复位南桥内部的逻辑电路,因此我们应首先在未插上ATX电源之前量测电池是否有电,CMOS跳线上是否有2.5V-3V的电压。

2.检查晶振是否输出了32.768KHz的频率给南桥(在nFORCE芯片组的主板上,还要量测25MHz的晶振是否起振)3.插上ATX电源之后,检查5VSB、3VSB、1.8VSB、1.5VSB、1.2VSB等待机电压是否正常的转换出来(5VSB和3VSB的待机电压是每块主板上都必须要有的,其它待机电压则依据主板芯片组的不同而不同,具体请参照相关芯片组的DATASHEET中的介绍)4.检查RSMRST#信号是否为3.3V的高电平,RSMRST#信号是用来通知南桥5VSB和3VSB待机电压正常的信号,这个信号如果为低,则南桥收到错误的信息,认为相应的待机电压没有OK,所以不会进行下一步的上电动作。

RSMRST#可以在I/O 、集成网卡等元件上量测得到,除了量测RSMRST#信号的电压外,还要量测RSMRST#信号对地阻值,如果RSMRST#信号处于短路状态也是不行的,实际维修中,多发的故障是I/O或网卡不良引起RMSRST#信号不正常。

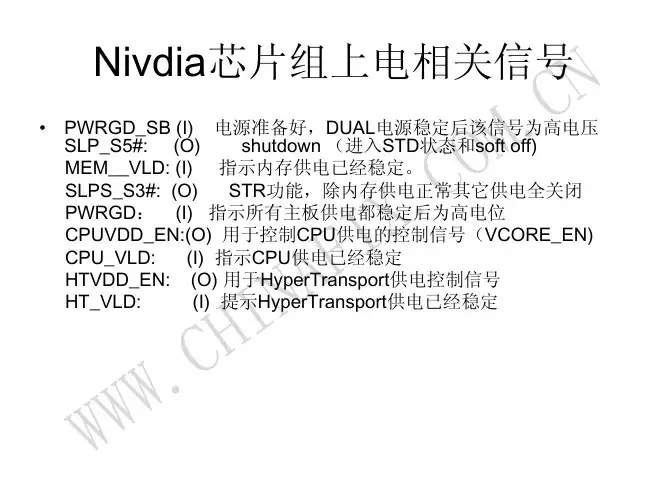

AMD平台时序讲解NVDIA 上电时序没有插电源:VBAT : 电池3VRTCRST:电池复位3V25M 晶振起震:测两脚有压差!当插上电源之后:3.3VSB/5VSB:待机电压PWRGD_SB:告诉南桥待机电压OK信号,和RSMRST 一样,一般是由3.3V 直接上拉得到!如果为低电平会导致不开机!按开关之后:PWRBTIN_:开关触发信号高低高跳变,到IO芯片PWBTOUT:IO 发出高低高的跳变信号到桥。

SLP_S5#:一般开启内存电压!由南桥发出!MEM_VLD(3.3V):内存电压OK信号!此信号到南桥,如果南桥收不到此信号会,导致不开机!一般有两种方式:1.MEM_VLD 信号直接由SLP_S5经过转换电路转换!不需要内存电压参与,则说明是开机之后,才产生内存电压!2.MEM_VLD 信号,有内存电压参与开启此信号需要先产生内存电压,后才开机!SLP_S3:通知IO可以开机!此信号是3.3V 由南桥发出到IO。

PS_ON:电源开启信号,为持续低电平,由IO发出此信号!3V/5V/12V: 电源工作后发出各个电压!桥电压: 经过三极管电路转换产生1.5V 电压。

M55_PWRGD : 告诉桥,电压OK,可以开启CPU供电!VCORE_EM: CPU供电开启信号!一般是高电平!CPU 产生电压!VCORE_PWORD: CPU供电正常之后发出的高电平信号!一般是到桥里面!也叫CPU_VLDHT_VDD EN (VTT电压): VTT电压的开启信号!HT_VLD : VTT 电压OK信号!HT_CPU_PWRGD: 桥发出的CPU PG信号,通知CPU所有电压OK!开始发出各个复位:CPU复位:。

上电时序总结BIOS(基本输入输出系统)在整个系统中的地位是非常重要的,它实现了底层硬件和上层操作系统的桥梁。

比如你现在从光盘拷贝一个文件到硬盘,您只需知道“复制、粘贴”的指令就行了,您不必知道它具体是如何从光盘读取,然后如何写入硬盘。

对于操作系统来说也只需要向BIOS发出指令即可,而不必知道光盘是如何读,硬盘是如何写的。

BIOS构建了操作系统和底层硬件的桥梁。

而我们平时说的BIOS 设定仅仅是谈到了其软件的设定,比如设置启动顺序、禁用/启用一些功能等等。

但这里有一个问题,在硬件上,BIOS是如何实现的呢?毕竟,软件是运行在硬件平台上的吧?这里我们不能不提的就是EC。

EC(Embed Controller,嵌入式控制器)是一个16位单片机,它内部本身也有一定容量的Flash来存储EC的代码。

EC在系统中的地位绝不次于南北桥,在系统开启的过程中,EC控制着绝大多数重要信号的时序。

在笔记本中,EC是一直开着的,无论你是在开机或者是关机状态,除非你把电池和Adapter完全卸除.在关机状态下,EC一直保持运行,并在等待用户的开机信息。

而在开机后,EC更作为键盘控制器,充电指示灯以及风扇和其他各种指示灯等设备的控制,它甚至控制着系统的待机、休眠等状态。

主流笔记本系统中.现在的EC有两种架构,比较传统的,即BIOS 的FLASH通过X-BUS 接到EC,然后EC通过LPC接到南桥,一般这种情况下EC的代码也是放在FLASH中的,也就是和BIOS共用一个FLASH。

右边的则是比较新的架构,EC和FLASH共同接到LPC总线上,一般它只使用EC内部的ROM。

至于LPC总线,它是INTEL当初为了取代低速落后的X-BUS而推出的总线标准。

EC上一般都含有键盘控制器,所以也称KBC。

那EC和BIOS在系统中的工作到底有什么牵连呢?在这里我们先简单的分析一下。

在系统关机的时候,只有RTC部分和EC部分在运行。

RTC部分维持着计算机的时钟和CMOS设置信息,而EC则在等待用户按开机键。

AMD 双桥芯片组时序信号解释:VBAT:RTC电路的供电,3V。

(RTC电路有问题会导致没复位或不跑码、不显示等故障)RTC clock in:晶振给南桥提供32.768KHz频率,(RTC电路有问题会导致没复位或不跑码、不显示等故障)S5_3.3V:南桥主待机电压,3.3V S5_1.2V:南桥第二个待机电压,老的南桥是1.8V,后来是1.2V或1.1V。

RSMRST#:南桥待机电压好。

PWR_BTN#:电源开关触发后,最终送达南桥的触发信号,高低高的脉冲WAKE#:唤醒信号,通常来自于网卡芯片,作用类似于PWR_BTN#SLP_S5#:南桥发出的退出关机状态的信号,3.3V,用于控制内存供电产生SLP_S3#:南桥发出的退出睡眠状态的信号,3.3V,用于控制所有的S0电压ALL power rails:所有电源被开启,包括内存供电、桥供电、VDDA供电、CPU供电、总线供电等。

System clocks:时钟芯片开始工作PCIE_RCLKP/N:时钟芯片送给南桥的100M差分时钟对,作为南桥的主时钟信号PWR_GOOD:通知南桥,此时S0状态电压全部OKPCICLK[5:0]:南桥发出PCI时钟NB_PWRGD:南桥发出给北桥的电源好信号,悬空或连接北桥的POWERGOOD脚。

南桥内部集成了一个完整的时钟模块,如果不启用南桥集成的时钟模块,而使用外置时钟芯片,NB_PWRGD可以不采用,只需要把北桥的POWERGOOD连接到南桥的PWR_GOOD,即南北桥同时得到PG。

如果启用南桥集成的时钟模块,不使用外置时钟芯片,南桥在收到PWR_GOOD后需要延时39ms,才会发出NB_PWRGD给北桥。

延时的目的是为了等待南桥内部的时钟模块工作稳定。

LDT_STP#:南桥发给CPU的高电平,由内存供电上拉。

通知CPU退出停止状态。

LDT_PG:南桥发出给CPU的电源好,由内存供电上拉。

A_RST#:南桥发出的平台复位,相当于INTEL的PLTRST#,3.3V。

驱动芯片上下电时序制定标准

一、电源电压稳定时间

在驱动芯片上电时,首先需要确保电源电压稳定。

电源电压稳定时间是指从电源上电开始,到电压稳定在设定范围内的持续时间。

该时间需要满足芯片启动的要求,以保证芯片正常工作。

二、芯片启动时间

芯片启动时间是指从电源电压稳定开始,到芯片内部电路完全启动并进入正常工作状态的持续时间。

该时间受到芯片内部电路设计和电源电压等因素的影响。

三、输出电压建立时间

输出电压建立时间是指从芯片启动开始,到输出电压稳定在设定范围内的持续时间。

该时间需要满足外部电路的要求,以保证整个系统的正常工作。

四、输出电流限制

在驱动芯片工作时,需要限制输出电流的大小,以避免对外部电路造成过大的电流冲击。

输出电流限制需要根据外部电路的具体要求进行设定。

五、关闭时序

在驱动芯片关闭时,需要按照一定的时序进行操作,以保证系统的正常关闭。

关闭时序包括芯片内部的关闭时序和外部电路的关闭时序。

六、故障保护功能

驱动芯片需要具备故障保护功能,以防止因故障导致系统损坏或数据丢失。

故障保护功能包括过流保护、过压保护、欠压保护等。

七、温度保护功能

驱动芯片需要具备温度保护功能,以防止因温度过高导致芯片损坏或性能下降。

温度保护功能包括过热保护、温度报警等。

八、静电保护功能

驱动芯片需要具备静电保护功能,以防止因静电放电导致芯片损坏或性能下降。

静电保护功能包括ESD保护、人体感应保护等。

AMD NV芯片组上电时序详细解说

上电部分

NV芯片组,待机条件有三个:3VSB,25M晶振,PWRGD_SB。

★3VSB桥里面叫+3.3V_PLL_DUAL,图纸第25页。

★3VSB由三端稳压器1117产生,1117产生的+3.3V_TBY和+3.3V_DUAL两个电压其实就是同1个电压,只不过+3.3V_DUAL多了CT37这个电容滤波而已!+3.3VDUAL还给PCI槽A14(这个可以用打阻值卡来查)及其它地方供电或提供上拉,图纸第46页。

★桥得到3VSB后,25M晶振开始起振,晶振电压1.5V左右,两脚要有压差。

最可靠的还是使用示波器来查看波形,图纸第24页。

★PWRGD_SB是用来复位桥内部ACPI控制逻辑和寄存器的,相当于INTEL芯片组的RSMRST#,它必须是高电平!这里由紫5伏经过两个开关管同相产生,如果+3.3V_STBY 没有出来,它也不会得到高电平。

图纸40页。

★至此桥的待机条件已查完,下面看看它的触发电路,从开关开始查,图纸第42页。

开关16脚经过R333电阻接地,15脚信号名字叫PWRBTN*。

★PWRBTN*由R305电阻提供上拉连到IO(IT8716FCX)75脚,未触发开关之前为5伏。

触发开关后,IO75脚得到低电平跳变,此时IO本身供电正常,则从72脚发出低电平跳变到桥。

图纸34页。

跳变电压我们都用示波器来测量。

★桥待机条件满足,然后收到IO发过来的低电平跳变,将依次置高

SLP_S5#,SLP_S4#,SLP_S3#。

其中SLP_S3#一路返回IO71脚,IO收到SLP_S3#高电平后,76脚由高电平变为低电平去拉低电源绿线完成上电,图纸34页。

★至此主板的上电已完成,ATX发出VCC3、VCC、+12V等主供电,最后延迟几百毫秒从灰线发出ATXPWOEROK信号,高电平。

◆需要注意的是,CMOS电路有问题,一般不会引起不上电,但会导致不跑码。

有少部分主板,CMOS电路不正常,也会导致不上电。

二、供电部分

1、内存供电:

★由PWM芯片RT9214产生,受控于SLP_S5#信号。

也就是说,只有南桥把SLP_S5#信号置为高电平时内存供电才会出来。

我们知道,在S3状态时,SLP_S5#信号高电平,SLP_S3#信号低电平,由于RT9214第1脚采用+5V_DUAL供电,所以此时RT9214芯片还是工作的,内存还有供电。

此外,另一路供电+1.8VDIMM_FB送至43页的IT8266超频芯片,该芯片没有装,所以这路供电没有采用。

★内存供电1.8V_SUS产生后还会经过两个NPN三极管同相产生MEM_VLD送至桥,作反馈,这个信号相当于内存供电的PG信号,高电平有效。

2、桥供电:NV桥有VCC

3、VCC5、+1.5V主供电,它们都不受时序控制。

★VCC3由电源橙色3.3V经过电阻送至桥。

★VCC5由电源红5V经过电阻送至桥。

★+1.5V由PWM芯片RT9214产生,RT9214只要1、5、7引脚高电平就会正常工作,这些引脚在ATX发出主供电后就正常。

3、CPU供电:采用PWM芯片ISL6566,此芯片工作原理是:VCC、PVCC、VCORE_EN、

VID组合。

其中VCC、PVCC由ATX经过电阻直接提供,VID组合在内存供电正常后由CPU内部的VID控制器发出,而VCORE_EN则由桥提供。

★桥必须先收到PWRGD信号以及本身主供电满足才发出VCORE_EN。

PWRGD

信号由ATXPWROK信号经过电阻分压而得到。

图中PWRGD_PS即ATXPWROK,CK8_PWRGD即桥PWRGD。

★PWM芯片ISL6566工作条件满足,控制MOS产生CPU供电,最后发出CPU_VREGPWRGD信号给桥。

4、桥收到ISL6566的CPU_VREGPWRGD信号后,发出HTVDD_EN去开启总线供电。

★总线供电+1.2VHT受控于HTVDD_EN信号,HTVDD_EN高电平时,+1.2VHT 才正常。

LDTV0、LDTV1是由IO发出,用在超频时调节总线电压的。

★总线供电正常后,经过两个NPN三极管同相发出HT_VLD信号给桥,HT_VLD 相当于总线PG信号。

5、VDDA:CPU的另外一个额外供电2.5V,它也和桥供电一样,不受时序控制,

ATX主供电出来后,VDDA2.5V即由三端稳压器1117产生。

◆桥主供电、VDDA不受时序控制,而内存供电、CPU供电、总线供电则受时序控制。

一环扣一环,任何一个环节不正常,就会导致无后续的供电产生。

如果没有内存供电,则需要查SLP_S5#信号是否正常送到RT9214芯片,中间的两个N沟道MOS是否有损坏。

如果没有CPU供电,则需要查ATXPWROK信号是否正常送到桥,桥的主供电是否正常。

内存供电正常后发出的MEM_VLD信号如果没有正常送到桥,不会导致桥不发出VCORE_EN信号,但是会导致不跑码。

如果没有总线供电,则要查CPU供电正常后发出的CPU_VLD信号是否送到桥,这是HTVDD_EN发出的前提条件。

此外,还要查IO发出的OV_LDTV0、OV_LDTV1信号是否正常。

以上供电产生的前提必须是芯片的其它工作条件也正常。

三、时钟&复位

1、时钟:NV芯片组的主板没有时钟芯片,它的时钟集成在桥里面,只要桥的

各供电正常,就会发出时钟给各个模块,这里就不再赘述。

2、复位:桥得到HT_VLD信号,并且供电正常,则发出各路复位和CPU_PWRGD 信号。

★PCI A15复位,由桥直接发送。

★IDE复位,由桥直接发送。

★PCI-E复位,由桥直接发送。

★桥发出的LPC_RESET*复位分两路,一路给BIOS芯片,另一路给IO。

★声卡复位由桥直接送出。

★网卡复位由桥直接送出。

★CPU_PWRGD由桥发出,经过08门和PWRGD_SB相“与”后,再由RN107排阻上拉。

★CPURST#由桥发出,经过08门和PWRGD_SB相“与”后,再由RN107排阻上拉。

CPU收到CPU_PWRGD和RESET#后,主板时序已完成,开始寻址跑码。

◆如果PCI,IO芯片等的复位正常,而CPU收到CPU_PWRGD却未收到CPU_RST#信号,说明桥发出复位的条件已满足,只需查CPU_RST#到桥的相关电路。

要么中间有断线或者是相关元件损坏,要么是桥内部发出CPU_RST#复位的模块损坏,而不需去查桥的复位条件。