基于cyclone

- 格式:docx

- 大小:394.60 KB

- 文档页数:7

基于CycloneⅢ构成的RS编码系统苗鑫;邓攀;殷奎喜【摘要】本文采用Ahera公司的FPGA器件CycloneIII系列EP3CIO作为核心器件构成了R-S(255,223)编码系统;利用QuartusⅡ9.0作为硬件仿真平台,用硬件描述语言Verilog_HDL实现编程,并且通过JTAG接口与EP3C10连接。

R—S(Reed—Solomon)码是一类纠错能力很强的特殊的非二进制BCH码,能应对随机性和突发性错误,广泛应用于各种通信系统中和保密系统中。

R—S (255,223)x6能够检测32字节长度和纠错16字节长度的连续数据错误信息。

%This paper uses Altera company FPGA Cyclone III series EP3C10 devices as a core component of R-S (255223) coding system;Using Quartus II 9.0 as a hardware emulation platform, using hardware description language Verilog__HDL programming, and through the JTAG interface and EP3C10 conneetion.R-S ( Reed-Solomon ) code is a kind of special non binary BCH code which's error correction capability is very strong, can deal with random and burst error, widely used in all kinds of communication systems and security systems.R-S (255223) code is capable of detecting and correcting the length of 32 bytes 16 byte length of continuous data error information.【期刊名称】《电子设计工程》【年(卷),期】2012(020)004【总页数】4页(P189-192)【关键词】CycloneⅢ;QuartusⅡ9.0;Verilog_HDL;R—S(255;223).码【作者】苗鑫;邓攀;殷奎喜【作者单位】南京师范大学物理科学与技术学院,江苏南京210046;南京师范大学物理科学与技术学院,江苏南京210046;南京师范大学物理科学与技术学院,江苏南京210046【正文语种】中文【中图分类】TN911.22R-S码是用其发明人的名字Reed和Solomon命名的。

一、引言在遥感图像处理中,图像配准是一项十分重要的工作。

它指的是将两幅或多幅不同时间或不同传感器所获取的图像,经过数学变换,使它们在同一坐标系下的一种处理方法。

而在图像配准的过程中,控制点的选取是至关重要的一环。

本文将重点讨论cyclone控制点配准原理。

二、控制点配准原理的基本概念1. 控制点的定义控制点是指在空间中已知准确位置的一些点。

在图像配准过程中,利用这些控制点可以对两幅或多幅图像进行准确的匹配,从而实现图像的配准。

2. cyclone控制点配准原理的概述在遥感图像处理中,cyclone控制点配准原理是一种常用的配准方法,其主要原理是通过在两幅图像中选取一定数量的控制点,并利用这些控制点之间的空间位置关系,来进行图像配准操作。

通过对控制点的匹配和变换过程,可以使得两幅图像在同一坐标系下达到较高的匹配精度。

三、cyclone控制点配准原理的具体步骤1. 选择控制点在进行图像配准时,首先需要在两幅图像中选择一定数量的控制点。

这些控制点要尽可能覆盖整个图像区域,并且需保证它们在实际空间中有一定的几何关系。

2. 控制点匹配选取好控制点后,接下来就是进行控制点的匹配工作。

这个过程需要对两幅图像进行特征提取和特征匹配,从而找到相应的控制点对。

3. 坐标转换在完成控制点匹配后,需要进行坐标转换的工作。

通过对选取的控制点进行空间坐标的转换,使得两幅图像在同一坐标系下实现匹配。

4. 评价配准精度需要对配准后的图像进行评价,检验配准的精度是否符合要求。

若不符合要求,可能需要调整控制点或者调整配准参数。

四、cyclone控制点配准原理的应用场景1. 遥感图像处理在遥感图像处理中,由于不同时间或不同传感器获取的图像可能会存在一定程度的偏移或变形,因此需要进行图像配准操作。

cyclone控制点配准原理可以有效地应用于这种场景下,提高图像配准的精度。

2. 地理信息系统在地理信息系统中,常常需要将不同时间或不同来源的地理数据进行整合和分析。

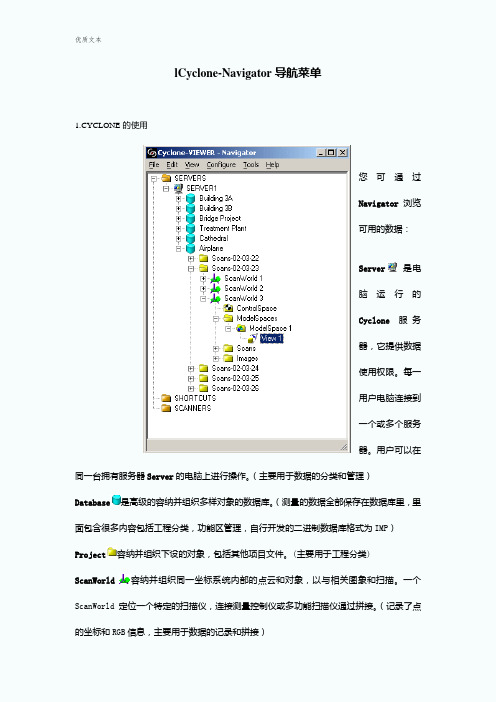

lCyclone-Navigator导航菜单1.CYCLONE的使用您可通过Navigator浏览可用的数据:Server是电脑运行的Cyclone服务器,它提供数据使用权限。

每一用户电脑连接到一个或多个服务器。

用户可以在同一台拥有服务器Server的电脑上进行操作。

(主要用于数据的分类和管理)Database是高级的容纳并组织多样对象的数据库。

(测量的数据全部保存在数据库里,里面包含很多内容包括工程分类,功能区管理,自行开发的二进制数据库格式为IMP)Project容纳并组织下设的对象,包括其他项目文件。

(主要用于工程分类) ScanWorld容纳并组织同一坐标系统内部的点云和对象,以与相关图象和扫描。

一个ScanWorld定位一个特定的扫描仪,连接测量控制仪或多功能扫描仪通过拼接。

(记录了点的坐标和RGB信息,主要用于数据的记录和拼接)ModelSpace容纳同一坐标系统内部的一组点云和3D对象,相当于一个3D模型。

(cyclone 里最重要的编辑区,几乎包括了所有的编辑操作,如点云的显示隐藏、旋转拉伸、点云切片、定义坐标系统,生成和插入模型、模型切片等等)ModelSpace View压缩设置(可视的和互动的),在空间模型浏览器中查看模型空间时使用。

一个给定的模型空间可能有多个模型空间视图,每个都有查看相同数据的不同方式。

(ModeSpace的视图,属于ModeSpace)Scan 相当于一次可以生成点云的扫描记录。

(相当于将点的X,Y,Z坐标以TXT文件的形式保存)Image是输入位图,或扫描的视频图象。

(记录扫描仪照的照片,扫描的全景为111张照片的拼合体,可将这些照片直接赋予点云,让点云更加直观)以下对象也可以在数据库中找到,但是不能通过Cyclone-VIEWER打开:Registration是连接不同ScanWorlds(每个都有不同的坐标系统)使其通向共同坐标系统的路径。

(也就是两站之间的拼接,可通过标靶和点云两种拼接方式)ControlSpace 是专门的模型空间, 容纳用于拼接的对象。

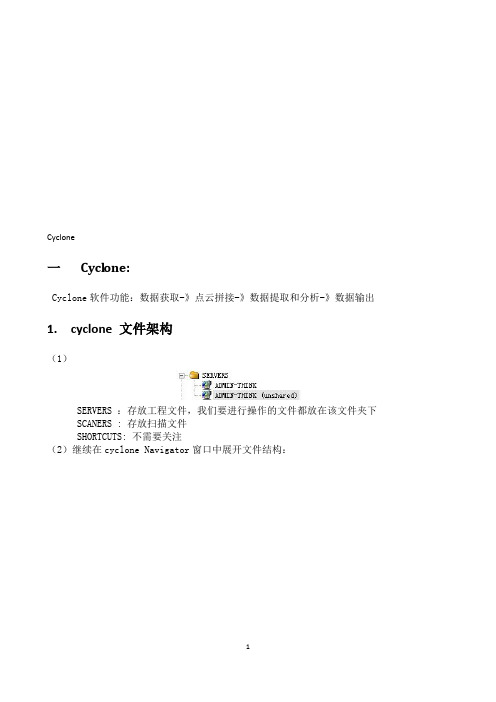

Cyclone一Cycl one:Cyclone软件功能:数据获取-》点云拼接-》数据提取和分析-》数据输出1. cyclone 文件架构(1)SERVERS :存放工程文件,我们要进行操作的文件都放在该文件夹下SCANERS : 存放扫描文件SHORTCUTS: 不需要关注(2)继续在cyclone Navigator窗口中展开文件结构:ControlSpace:控制点和标靶的信息(只能看,不能编辑的)Modelspaces: 所有的编辑都在此模块Scans:标靶和扫描的一些信息Images:扫描时拍的照片。

2 cyclone中导入扫描的工程文件:(1)直接导入数据库文件(*.imp):I 打开cyclone,选中ADMIN-THINK(unshared),右击,单击“database”,出现如下对话框:2-1II 点击Add ,找到数据库文件,例如找到5.1Moudule 1 QuickStart.imp的位置,选中打开。

选择OK即可加入。

这样5.1Moudule 1 QuickStart在server文件夹下显示出来。

(2)导入的扫描文件中不含有*.Imp文件:I首先建立一个空的文件夹,例如20111018,在20111018下新建一个空的数据库文件,例如20111018.imp,步骤如下:a.打开cyclone-》选中ADMIN-THINK(unshared),右击,单击“database”,出现如下对话框:2-2B 单击Add.找到你想存放的目录,先新建一个文件夹,例如20111018,再双击打开该文件夹,在文件名栏输入你需要建立的数据库名,例如20111018,点击打开,选择OK。

这样一个空的工程文件20111018.imp建立了。

在cyclone的server下可以展开查看。

II导入扫描的数据:选中工程文件,右击选中import scanstation C10 data import scanstation C10 project,找到你需要导进来的扫描数据文件即可。

摘要:本文主要通过介绍Cyclone 系列FPGA 器件的配置方案,主要阐述了低成本专用配置芯片的主动串行(AS )配置方案以及基于微处理器的被动串行(PS )配置方案的配置过程。

介绍了如何结合工程设计选择配置方案,改变现在的任意选择配置方案的现象。

提出一种实时解压数据减少贮存要求和配置时间的配置方案,这些方案在工程项目中具有很高的实际应用价值。

关键词:Cyclone FPGA 配置模式主动串行被动串行0引言FPGA 是英文Field -Programmable Gate Array 的缩写,即现场可编程门阵列,它是在PAL 、GAL 、CPLD 等可编程器件的基础上进一步发展的产物。

FPGA 技术广泛应用于通讯、视频、信息处理等特定领域。

FPGA 主要生产厂商有Altera 、Xilinx 、Actel 和Lattice ,对比不同的FPGA 编程技术特点,综合各个厂家不同系列器件的技术优势、逻辑资源、器件功耗、芯片速度、供货、价格和系统要求等诸多因素考虑,在很多项目设计中采用Altera 公司基于SRAM 架构Cyclone 系列器件。

Cyclone 器件与其他FPGA 器件一样是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。

这些配置数据可通过多种模式加载到FPGA 内部的SRAM 中,由于SRAM 的易失性,每次上电时,都必须对FPGA 进行重新配置。

1Cyclone FPGA 配置模式Cyclone 系列FPGA 器件配置方案主要有三种,包括使用低成本配置芯片的主动串行(AS )配置、被动串行(PS )配置以及基于JTAG 配置,实际应用时可以使用其中的一种方案配置Cyclone 系列FPGA 器件,来实现用户编程所要实现的功能。

Cyclone 系列FPGA 器件是用SRAM 单元配置数据的。

由于SRAM 掉电后容易丢失数据,配置数据必须即时地下载到上电的Cyclone 器件中。

摘要Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

本论文的开头部分详细介绍了Cyclone系列芯片的体系结构。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

之后,论文对Cyclone系列芯片的配置方法进行了探讨,并着重介绍了低成本的串行配置方案。

接着,论文对此次毕业设计中用到的主要开发工具进行了简要介绍,其中包括Protel 99SE和Quartus II软件。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

关键词:Cyclone,逻辑阵列块,逻辑单元,互连,锁相环,I/O元素,串行配置器件,Quartus IIABSTRACTAltera®Cyclone™FPGAs—the lowest-cost FPGAs ever—are half the cost of competing devices. Cyclone FPGAs are the optimal solution for high-volume, price-sensitive applications that previously required the use of fixed solutions such as gate arrays and standard cells.At the beginning of the dissertation, we describes the Cyclone architecture in detail. Cyclone FPGAs are built on a cost-optimized, all-copper 1.5-V SRAM process. With up to 20,060 logic elements (LEs) and 288 Kbits of RAM, Cyclone FPGAs can integrate many complex functions. Cyclone FPGAs offer multiple full-featured phase-locked loops (PLLs) to manage board-level clock networks and dedicated I/O interfaces for interfacing with industry standard external memory devices. Altera's Nios® embedded processor and a full intellectual property (IP) portfolio is available for development with Cyclone FPGAs.Then we discuss the configuration schemes of the Cyclone devices,especially the low-cost active serial configuration scheme.After that, we talk about the tools which we used in this graduation design. These tools contain Potel 99SE and Quartus II .Lastly, we use the EP1C12 device in the 240-pin PQFP package and the EPCS1 device which is used to configure EP1C12 in the active serial configuration scheme to implement an electronic clock. In this part, the thesis mainly explains the composition, internal design (including drawing schematic diagram, drawing PCB diagram and programming in VHDL) and simulation of the board.KEY WORDS: Cyclone, LAB, LE, Interconnect, PLL, IOE, Serial Configuration Device, Quartus II目录第一章绪论 (1)1.1.可编程逻辑与ASIC简介 (1)1.2.课题来源及意义 (1)1.3.作者所做工作 (2)1.4.论文结构安排 (2)第二章Cyclone系列芯片的结构分析 (3)2.1.概述 (3)2.1.1.Cyclone主要特性 (3)2.1.2.功能描述 (4)2.2.逻辑阵列块(LAB) (5)2.2.1. LAB互连 (6)B控制信号 (6)2.2.3.逻辑单元(LE) (7)2.2.4.LUT链和寄存器链 (8)2.2.5.addnsub信号 (8)2.2.6.LE的操作模式 (8)2.2.7.进位选择链 (9)2.2.8.清零/重置逻辑控制 (9)2.3.多通道互连(MultiTrack Interconnect) (9)2.4.嵌入式存储器 (10)2.4.1.存储模式 (11)2.4.2.支持奇偶校验位 (11)2.4.3.支持移位寄存器 (12)2.4.4.存储器的配置大小 (12)2.4.5.字节使能 (13)2.4.6.独立时钟模式 (13)2.4.7.输入/输出时钟模式 (13)2.4.8.读/写时钟模式 (13)2.4.9.单端口模式: (14)2.5.全局时钟网络和锁相环 (14)2.5.1.全局时钟网络 (14)2.5.2.双效时钟管脚 (15)2.5.4.锁相环(PLLs) (15)2.6.I/O结构 (16)第三章Cyclone系列芯片的主动串行配置方法 (19)3.1.Cyclone系列芯片主要配置方法简介 (19)3.2.串行配置的实现 (20)3.2.1.配置多个层叠状态的器件 (21)3.2.2.对串行配置器件进行编程 (22)3.2.3.串行配置器件的管脚描述 (22)第四章Protel 99SE及Quartus II软件简介 (23)4.1.Protel电子电路设计软件 (23)4.2.Quartus II开发工具 (24)4.2.1.Quartus II概述 (24)4.2.2.Quartus II的功能 (24)第五章基于Cyclone系列芯片的简单应用 (27)5.1.板卡的组成及结构图 (27)5.2.板卡的逻辑设计 (29)5.2.1.七段显示器模块的逻辑设计 (29)5.2.2.电子时钟时间计数模块的逻辑设计 (32)5.2.4.弹跳消除电路模块的逻辑设计 (34)5.2.3.电子时钟时间设定及其时间显示模块的逻辑设计 (36)附录一消除弹跳电路及微分电路组合模块的程序代码 (41)附录二自由计数器模块及状态转换模块的程序模块 (43)结束语 (45)致谢 (46)参考文献 (47)第一章绪论1.1.可编程逻辑与ASIC简介可编程逻辑器件(PLD)是由用户编程实现所需要逻辑功能的数字集成电路。

基于cycloneⅡ的虚拟示波器设计

摘要

以LabWindows/CVI为开发平台,利用嵌入NIosⅡ软核的FPGA构成SOPC系统,设计了1种双通道虚拟示波器,详细阐述了虚拟示波器的数据采集电路的设计方法,信息处理部分电路设计方法,SOPC系统的构建方法,USB通信接口的设计方法,完成了虚拟示波器上位机软件设计,实际测试结果表明,该虚拟器可以实现多种触发方式,界面友好,操作简单。

关键字:虚拟示波器 SOPC系统 CycloneⅡ芯片 NiosⅡ处理器

0 引言

虚拟示波器是采用基于计算机的虚拟技术,用以模拟虚拟示波器的面板操作和处理功能,也就是使用个人计算机及其接口电路来采集现场或实验室信号,并通过图形用户界面(GUI)来模仿示波器的操作面板,完成信号采集,调理,分析和显示输出等功能。

CycloneⅡ系列FPGA是Altera公司的低成本FPGA,具有以下特性:支持NiosⅡ软核处理器;嵌入式存储资源支持各种存储器应用;有从低到中等速度的I/O和存储器接口;使用片内锁相环管理片内和片外系统时序;支持串行总线和网络接口及各种通信协议;采用新的串行配置器件的低成本配置方案;广泛的IP核支持。

CycloneⅡ器件主要由嵌入式存储器块,逻辑阵列块(LAB),锁相环(PLL),内嵌乘法器模块和I/O单元(IOE)等模块组成。

嵌入式存储器包括数十个M4K存储器块。

每个M4K存储器块具有很强的伸缩性,可以实现最大4608位的存储器。

联合使用多个M4K存储器块可以形成更大存储容量的存储器。

使用这些嵌入式存储器能够实现双端口存储器,单端口存储器或者FIFO存储器。

LAB是由一系列相邻的LE构成的。

每个LAB包含16个LE,LE进位链和级联链,LAB 控制信号,LAB局部互联,LUT链和寄存器链。

CycloneⅡ中设置了复杂的全局时钟网络,以减少时钟信号的传输延迟。

有2~4个锁相环,可以用来调整时钟信号的波形,频率和相位。

锁相环提供了CycloneⅡ中的通用时钟,并可以对时钟信号进行分频和倍频,还可以调整时钟信号的占空比。

CycloneⅡ器件的内嵌乘法器模块可以实现一些常用的数字信号处理功能函数,如有限长单位脉冲响应滤波器(FIR),快速傅里叶变换(FFT)和离散余弦变换(DCT)。

CycloneⅡ器件的IOE中有3个触发器,分别是输入触发器,输出触发器和输出使能触发器。

CycloneⅡ器件最多可支持129个通道的LVDS和RSDS。

CycloneⅡ器件内的LVDS缓冲器可以支持最高达640Mbps的数据传输速率。

进行电路设计时,必须进行器件的选择。

一般要考虑一下几项因素:器件的资源,最高时钟频率,工作电压,最大I/O引脚数,以及封装形式等。

表1 CycloneⅡ系列器件的逻辑资源

1 虚拟示波器硬件电路设计

1.1 虚拟示波器数据采集通道电路设计

为减少虚拟示波器对被测电路的影响,要求虚拟示波器采集通道的输入阻抗在1MΩ以上,因此必须设计合适的衰减器和可控增益的放大器,虚拟示波器数据采集通道的原理如图1所示:

图1 虚拟示波器数据采集通道组成

图1中,虚拟示波器的2个通道完全对称,且相互独立。

从探头进来的信号经过衰减网络,获得合适的信号强度,进行AC/DC切换开关后,送到可控增益放大器,将不同幅度的信号放大为幅度大致相同的信号,经高速A/D转换获得两路独立的数字信号,同时触发电路完成触发功能,使波形能平稳地显示。

1.1.1 衰减与AC/DC转换电路

衰减与AC/DC转换电路,下图为虚拟示波器的衰减与AC/DC转换电路

图2 衰减与AC/DC转换电路

图2中,R1,R2,R3,C1和R4,C2组成1:10的分压网络,通过CPU控制三极管Q1,Q2和继电器K1,K2分别控制进行1/10的衰减与AC/DC切换控制。

1.1.2 可控增益放大器

虚拟示波器需要设计宽范围可调节的增益放大电路器,以实现10mV~±200V范围内的输入电压采样。

本系统采用模拟多路器切换运放的反馈电阻,以达到改变增益的木器,电路图如图3所示。

图3 可控增益放大器

图3中,UI内部包含两通道JFFT高输入阻抗的运放,前级为跟随器,以满足示波器的高输入阻抗要求,第二级为可控增益放大器,由模拟多路器和运放共同构成。

1.1.3 A/D转换电路

虚拟示波器的A/D转换器采用Linear公司的LTC2289,它的采样频率可达80MHz,有2个独立通道。

1.2 虚拟示波器信息处理部分硬件设计

虚拟示波器信息处理部分主要包括FPGA系统和USB通信部分,其组成方框如图4所示

图4 数字部分

图4中,虚拟示波器模拟输入通道的模拟信号经A/D转换后获得数字信号,经过1个数据缓冲器输入到FPGA,FPGA通过逻辑电路和NiosⅡ管理将数据进行存储,上传等。

图4中SARM用于缓存采样数据;FLASH用于存储NiosⅡ应用程序,并实现系统上电时将程序加载至SDRAM中。

系统选择的USB接口芯片CY7C68001为USB2.0标准控制器,其可工作在高速或者全速状态,支持4个可配置共享4KB FIFO空间的端点,并具有一个标准8位或16位主机接口,非常适合高速USB接口。

2 虚拟示波器SOPC系统构建及NiosⅡ软件开发

2.1虚拟示波器SOPC系统构建

采用ALTERA公司的NiosⅡ软核处理器,并利用FPGA设计虚拟示波器系统。

ALTERA的NiosⅡ软核处理器是一个32位的RISC嵌入式处理器,具有5级流水线,采用数据和指令分离的Harvard结构,提供众多标准外设和软件集成开发环境。

在虚拟示波器中,需要开发符合AVALON总线的示波器模块,并加入到自定义IP中。

在SOPC插件中,将示波器模块等自定义模块集成为IP核,分别将NiosⅡJTAG_UART,FLASH以及SARM等IP核加入虚拟示波器系统中。

配置完成后生成系统,并在QuartusⅡ中进行引脚配置,然后综合,布线,生成配置文件,通过JTAG对FPGA进行配置,即可获得虚拟示波器系统的信息处理部分硬件电路。

2.2 NiosⅡ软件开发

NiosⅡ的软件开发一般采用分层的方式进行,采用HAL完成硬件相关设备的封装操作,因此每个CPU外设都需要有相应的驱动程序。

虚拟示波器系统中,NiosⅡ的驱动分层结构如图5所示:

图5 NiosⅡ软件分层结构

虚拟示波器系统需要为定义的IP设计相应的驱动程序,对于最底层与硬件相关的操作,

NiosⅡ提供了IOWR和IOPD2个宏,分别用于对寄存器的读,写操作。

虚拟示波器上位机程序采用LabWindows/CVI开发,其本身不支持USB通信,因此采用了调用外部模块的方法,编写程序将USB通信底层函数进行封装,编译成DLL,再供LabWindows/CVI进行调用。

3 虚拟示波器面板程序的开发

虚拟示波器系统采用LabWindows/CVI开发平台设计仪器控制面板。

系统利用曲线图控件,数值按钮控件,二值开关控件,按钮等控件,通过合理布局,生产ui文件并到处C 文件模板,在里面加入按钮回调函数,获得操作友好,方便的虚拟示波器用户界面,其面板如图6所示:

图6 虚拟示波器面板

图6 中,用户对虚拟示波器面板上的垂直调幅调节,水平宽度调节等按钮操作时,系统会将相应的操作命令传送给下位机,并由下位机调节垂直幅度和水平时基等,从而实现用户对虚拟示波器系统的操作。

4 结论

本文基于CycloneⅡ设计了1种双通道虚拟示波器,该示波器利用FPGA中嵌入的Nios Ⅱ软核构成的SOPC系统,完成虚拟示波器各模块的管理,利用嵌入式USB协议,完成各种波形数据的采集,经上位机软件完成了波形显示和数据分析,并实现了仪器的各种操作功能。

参考文献

[1]宁涛.虚拟仪器及其新进展[J].仪器仪表学报,2007,28(4):254—255.

[2]梁秋明,田梦君.基于LabVIEW的虚拟示波器的设计与实现[J].电子测量技术,2009,32(3):158—161.

[3]赵江滨,刘世元,胡友民.组件化虚拟仪器软件系统的性能研究[J].仪器仪表学报,2009,30(10):2131—2137

[4]程乃平,席有猷,赵阳.基于Lab/windows/CVI的虚拟频谱分析仪设计[J].电子测量技术,2009,32(7):109—111.。