GSM900低噪声放大器设计

- 格式:doc

- 大小:624.00 KB

- 文档页数:7

低噪声放大器的设计参数:低噪声放大器的中心频率选为2.4GHz,通带为8MHz通带内增益达到11.5dB,波纹小于0.7dB通带内的噪声系数小于3通带内绝对稳定通带内输入驻波比小于1.5通带内的输出驻波比小于2系统特性阻抗为50欧姆微带线基板的厚度为0.8mm,基板的相对介电常数为4.3 步骤:1.打开工程,命名为dzsamplifier。

2.新建设计,命名为dzsamplifier。

设置框如下:点击OK后,如下图。

模板为BJT_curve_traver,带有这个模板的原理图可以自动完成晶体管工作点扫描工作。

3.在ADS元件库中选取晶体管。

单击原理图工具栏中的,打开元件库,然后单击,在搜索“32011”。

其中sp开头的原件是S参数模型,可以用来作S参数仿真,但这种模型不能用来做直流工作点扫描。

以pb开头的原件是封装原件,可以做直流工作点扫描,此处选择pb开头的。

4.按照下图进行连接5.将参数扫描控制器中的【Start】项修改为Start=0.6.点击进行仿真,仿真结束后,数据显示窗自动弹出。

如下图:7.晶体管S参数扫描。

(1)重新新建一个新的原理图S_Params,进行S参数扫描。

如下图:点击OK后,出现:(2)在ADS元件库中选取晶体管。

单击原理图工具栏中的,打开元件库,然后单击,在搜索“32011”。

此处选择sp 开头的。

(3)以如图的形式连接。

(4)双击S参数仿真空间SP,将仿真控件修改如下。

(5)点击仿真按钮,进行仿真。

数据如下图所示:(6)双击S参数的仿真控件,选中其中的【Calculate Noise】,如图执行后:注意:晶体管参数指标如下:1.晶体管sp_hp_AT32011_5_1995105的频率范围为0.1GHz-5.1GHz,满足技术指标。

2.通带内噪声系数满足技术指标。

3.通带内增益不满足技术指标。

4.通带内输入驻波比不满足技术指标。

5.通带内输出驻波比不满足技术指标。

结论如下:1.频率范围和噪声系数满足技术指标,可以选取该晶体管。

GSM900/DCS1800 双频手机RF部分的设计Desige of RF Unit for GSM900/DCS1800 Dual-band Handset李航[摘要]:本文介绍了GSM/DCSl800双频段手机RF部分的基本工作原理和各单元的设计方案、技术指标和参数计算。

对几种不同的双频手机RF方案,在经过分析和比较之后,提出了一种性能价格比较高的技术方案。

[关键词]:GSM/DCSl800 双频手机射频电路电路设计GSM手机属高科技通信产品,其销售对象是千家万户,因此对手机的性能价格比要求特别高,手机的利润只能体现在大批量的生产和销售中。

针对这种情况,在满足欧洲电信标准ETS GSMll.10技术规范的前提条件下,RF部分的设计者必须在先行方案设计中就充分注意到性能价格比,这将对手机在未来的市场上能否有竞争力产生十分重要的影响。

GSM手机的性价比是由各个组成单元的性价比来决定的,所以,对RF部分各个单元电路进行认真、细致的分析和比较,这对于提高整机的性价比是十分重要的。

l GSM900/DCSl800双频手机的特点双频手机与现阶段普及型的单频手机相比,有下面的特点:根据基站的控制信令,双频手机即可以工作在900MHz频段网络,也可以工作在1800MHz频段网格,当一个网络繁忙或信号质量差时,双频手机可自动切换到另一个频段的网络上工作,而且这种切换基本上不影响话音质量。

另外,从近来国际上手机的发展趋势和FTA(full type approval)认证的情况来看,双频手机在将来会是主流产品。

双频手机在两个不同的工作频段上,其基带部分信源编码、信道编码的算法和处理、信令处理的方法和帧格式、调制解调方式、信道间隔等均相同,与单频手机在电路结构上的差别在于射频前端和相对应的控制软件。

2 GSM900/1800双频手机RF部分的主要技术指标和设计要求四类机,阶段2增强型(class IV phase Ⅱ pluse )E—GSM900MHz部分的主要RF指标如下:工作方式:TDMA—TDD工作频率:上行Tx(反向)880MHz-915MHz,下行Rx(正向)925MHz—960MHz 双工频率间隔:45MHz,载波间隔:200kHz每载波时隙数:8(当前全速率)/16(今后半速率)每帧长度:4.615ms,每时隙长:577μs传输速率:270.833kbps(即在每时隙上传156.25bits)调制方式:采用I/Q正交GMSK调制静态参考灵敏度:优于-102dB/RBER(Resiodual BER)<2%动态范围:-47dBm—110dBm频率误差:<1×10-7,相位误差的均方根值<5°,相位误差峰值:<20°射频输出功率:5级(33dBm)--19级(5dBm),级差:Δ=2dB,共有15个功率等级。

高效低噪声射频放大器设计随着科技的发展和普及,现代人对于通信技术也有了更高的要求。

射频放大器是通信技术中非常重要的元器件,它承担着信号的放大和传输任务。

为了保证通信技术的高效稳定性,设计高效低噪声射频放大器已经成为研究者所关注的重点。

本文以高效低噪声射频放大器设计为主题,阐述了射频放大器工作原理、设计思路和优化方法等方面内容。

一、射频放大器工作原理射频放大器是将一定带宽的电信号进行放大的元器件。

根据增益系数的不同,又可分为低增益射频放大器、中等增益射频放大器和高增益射频放大器三类。

低增益射频放大器广泛应用在接收机中,中等增益射频放大器应用于本振、中频放大等电路,而高增益射频放大器则常用于驱动输出等级。

基于放大器原理,射频放大器一般由放大电路、滤波电路、稳定电路和整流电路等部分组成。

其中,放大电路是评估射频放大器性能的关键部分之一。

二、设计思路在射频放大器的设计中,设计思路非常重要。

设计思路具有指导性和概括性,可避免重复性工作和研究过程的冗余。

设计思路包括如下几个方面:(1)选择合适的放大器结构和器件。

对于低噪声放大器,应选择晶体管、场效应晶体管等器件,高功率放大器应该选择晶体管、静电复合晶体管等器件。

(2)提高射频放大器的增益。

增益是射频放大器最为重要的参数之一。

射频放大器的增益受到许多因素的影响,在设计中应该充分考虑电路参数对增益参数的影响,一般采用电容耦合、电感耦合、差动模式、共源共极等优化技术。

(3)提高射频放大器的线性度。

通信技术中要求射频放大器具有高的线性度,电路中采用线性化技术、负反馈技术、A级放大器等方式可提高线性度。

(4)选用合适的功率稳定电路。

功率稳定是射频放大器中一个非常重要的参数。

采用零稳态技术、瞬态保护、电流限制等稳定电路可充分保证射频放大器的工作性能稳定。

(5)选用合适的整流电路。

提高整流效率是射频放大器制作中的一个重要工作。

在设计时,要根据整流电路的差异,采用合适的元件、选择合适的工作方式等对整流效率进行优化。

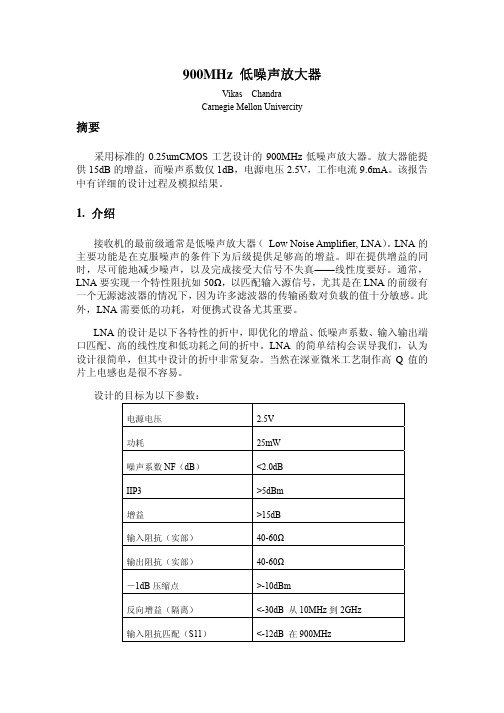

900MHz 低噪声放大器Vikas ChandraCarnegie Mellon Univercity摘要采用标准的0.25umCMOS工艺设计的900MHz低噪声放大器。

放大器能提供15dB的增益,而噪声系数仅1dB,电源电压2.5V,工作电流9.6mA。

该报告中有详细的设计过程及模拟结果。

1. 介绍接收机的最前级通常是低噪声放大器(Low Noise Amplifier, LNA)。

LNA的主要功能是在克服噪声的条件下为后级提供足够高的增益。

即在提供增益的同时,尽可能地减少噪声,以及完成接受大信号不失真——线性度要好。

通常,LNA要实现一个特性阻抗如50Ω,以匹配输入源信号,尤其是在LNA的前级有一个无源滤波器的情况下,因为许多滤波器的传输函数对负载的值十分敏感。

此外,LNA需要低的功耗,对便携式设备尤其重要。

LNA的设计是以下各特性的折中,即优化的增益、低噪声系数、输入输出端口匹配、高的线性度和低功耗之间的折中。

LNA的简单结构会误导我们,认为设计很简单,但其中设计的折中非常复杂。

当然在深亚微米工艺制作高Q值的片上电感也是很不容易。

设计的目标为以下参数:电源电压 2.5V功耗 25mW噪声系数NF(dB) <2.0dBIIP3 >5dBm增益 >15dB输入阻抗(实部) 40-60Ω输出阻抗(实部) 40-60Ω-1dB压缩点 >-10dBm从10MHz到2GHz反向增益(隔离) <-30dB在900MHz输入阻抗匹配(S11) <-12dB输出阻抗匹配(S22) <-12dB在900MHz传输函数平坦度(中心频率周围)-3dB带宽>100MHz采用标准的0.25umCMOS工艺设计的900MHz低噪声放大器。

为了得到纯实数的输入阻抗,我们采用源极电感负反馈的电路[1]。

这种结构与其它结构相比在得到50Ω阻抗时具有更低的噪声。

但源极电感负反馈的电路要求电路可以调谐,而该设计是窄带的。

低噪声放大器设计1. 引言本文档旨在讨论低噪声放大器的设计。

低噪声放大器在电子电路中起着重要的作用,可以提供高增益而又尽可能降低输入信号的噪声。

因此,低噪声放大器在无线通信、雷达系统和敏感测量等领域中得到广泛应用。

2. 设计原则低噪声放大器的设计应遵循以下原则:2.1 最小化噪声系数噪声系数是衡量放大器噪声性能的重要指标。

因此,在设计过程中应采取措施最小化噪声系数,例如使用低噪声元件、优化电路布局以降低噪声等。

2.2 选择合适的放大器拓扑结构不同的放大器拓扑结构具有不同的性能特点。

根据具体应用需求,选择合适的拓扑结构可以提高低噪声放大器的性能。

2.3 优化功率匹配功率匹配是低噪声放大器设计中的一个重要考虑因素。

通过优化功率匹配,可以提高放大器的效率和性能。

3. 设计步骤以下是一个简单的低噪声放大器设计的步骤:3.1 确定应用需求和规格首先,确定放大器的应用需求和规格。

这包括增益要求、频率范围、输入输出阻抗等。

3.2 选择合适的放大器拓扑结构根据应用需求,选择合适的放大器拓扑结构,例如共源放大器、共栅放大器等。

3.3 选取适当的元件选择适当的元件来实现放大器的设计。

对于低噪声放大器,应选择具有低噪声特性的元件,如低噪声晶体管等。

3.4 进行电路模拟和优化使用电路模拟工具进行低噪声放大器的电路设计和仿真。

通过不断优化电路参数,以满足设计需求和要求。

3.5 PCB设计和布局进行PCB设计和布局,优化电路的布局和连接,减少噪声干扰和信号损耗。

3.6 制造和测试根据设计要求,制造和测试低噪声放大器。

进行性能测试和验证。

4. 结论低噪声放大器设计是一个复杂而重要的工作,它需要综合考虑多个因素和技术。

本文档介绍了低噪声放大器设计的一般原则和步骤,希望能为读者提供一些参考和指导。

低噪声放大器的设计及优化低噪声放大器是一种重要的电路,其中最主要的特性是在增益很高的条件下,使噪声保持在很低的水平,这使它在许多电子设备中得到广泛应用,如电话、放射通讯等。

由于低噪声放大器具有良好的抗干扰能力和优秀的信号放大特性,在现代电子学中具有举足轻重的地位。

本文将从低噪声放大器的基本原理入手,介绍低噪声放大器的设计和优化方法,希望能够为读者提供一些参考和帮助。

低噪声放大器的基本原理低噪声放大器是一种运放电路,由多个晶体管、电阻器和电容器组成。

其主要作用是将微弱的信号放大到可控的幅度,并且在放大过程中对信号噪声进行有效的抑制,从而使得放大后的信号保持高质量的信号-噪声比。

低噪声放大器的噪声来源主要有三个,即器件本身的噪声、热噪声和环境噪声。

因此为了降低噪声,需要从这三个方面入手进行优化。

低噪声放大器的设计方法低噪声放大器的设计目标是在放大信号的同时,最大程度地消除噪声干扰,使得信噪比尽可能地高。

其设计方法包括了以下几个方面。

1. 确定器件的噪声参数器件的噪声参数是决定低噪声放大器噪声水平的关键参数。

在器件选型阶段,需要仔细研究器件的散热特性、噪声系数、增益等参数,以选取最优的器件,同时在电路设计中要注意控制和平衡各种参数,从而最大程度地减少噪声。

2. 优化放大器电路结构电路结构的合理设计和选择可以有效地降低低噪声放大器的噪声。

在实际设计中,需要结合各种器件的噪声参数和放大器电路的性能要求,优化电路结构以达到最佳的信噪比。

3. 提高放大器的带宽提高带宽可以通过增加电路的半导体晶片数目、增加电容和减小电感等方式来实现。

高带宽低噪声放大器的优点在于可以提高电路的响应速度,从而保证电路的准确性和灵敏度,同时也可以降低电路的噪声水平,提高信噪比。

4. 优化放大器的稳定性和线性度稳定性和线性度是低噪声放大器的两个重要性能参数。

稳定性决定了放大器在长时间稳定工作中的表现,不稳定的放大器会导致输出波形失真、振荡和其他问题。

微波电路与系统仿真实验报告

一、实验名称:GSM900频段低噪声放大器仿真

二、实验技术指标:

1.频段:909-915MHz

2.增益:≥17dB

3.噪声系数:<0.7dB

4.输入反射系数:优于-20dB

5.输出反射系数:优于-15dB

6.芯片选择:A TF-54143或VMMK-1218

三、报告日期:2015年12月14日

四、报告页数:共7页

五、报告内容:

1.电路原理图(原理图应标明变量名称的含义,可用文字表述或画图说明)

如下图所示,a为低噪声放大器的原理框图,包括晶体管以及输出输入匹配,在图中未画出部分还有晶体管的偏置电路。

对于低噪声放大器设计与最大功率传输的放大器设计不同,最大功率传输放大器的设计必须满足双共轭匹配,而这样噪声的功率也会很大,所以为了获得最小噪声系数,应选择最佳信源反射系数Гopt。

此时放大器的输入匹配网络的任务是使管子端口满足如下图b中所示的要求。

(a)微波晶体管放大器原理图(b)最佳噪声匹配放大器的设计步骤为:1、选管;题目指标给出了放大器设计可选择的管子,所以本次设计选择了ATF-54143,查阅ATF-54143晶体管的模型参数,由于ATF-54143晶体管在ADS2011中没有模型,所以本文是查找网络资源下载的ATF-54143的模型文件导入到设计中的,A TF-54143模型如下图所示,左图为晶体管封装模型,右图为内部电路。

2、确定工

作电流和工作电压;查阅ATF-54143介绍资料确定Vds和Ids的值,如下图所示,可以看出工作频率为900MHz时的晶体管在不同电压电流下的增益、噪声系数、P1dB、三阶截断功率的值,根据这些值选择Vds=4V,Ids=60mA,此时的Vgg=0.58V。

设置电压电流,建立晶

体管的直流偏置电路。