(完整版)OC门及三态门解析

- 格式:ppt

- 大小:1.57 MB

- 文档页数:1

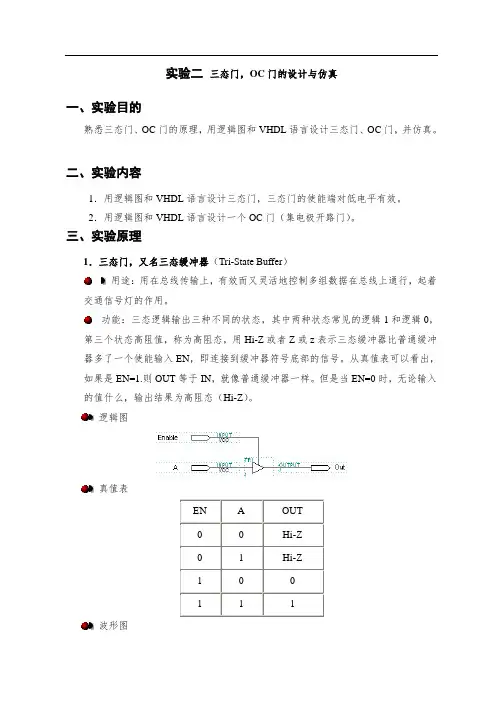

实验二三态门,OC门的设计与仿真一、实验目的熟悉三态门、OC门的原理,用逻辑图和VHDL语言设计三态门、OC门,并仿真。

二、实验内容1.用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2.用逻辑图和VHDL语言设计一个OC门(集电极开路门)。

三、实验原理1.三态门,又名三态缓冲器(Tri-State Buffer)用途:用在总线传输上,有效而又灵活地控制多组数据在总线上通行,起着交通信号灯的作用。

功能:三态逻辑输出三种不同的状态,其中两种状态常见的逻辑1和逻辑0,第三个状态高阻值,称为高阻态,用Hi-Z或者Z或z表示三态缓冲器比普通缓冲器多了一个使能输入EN,即连接到缓冲器符号底部的信号。

从真值表可以看出,如果是EN=1.则OUT等于IN,就像普通缓冲器一样。

但是当EN=0时,无论输入的值什么,输出结果为高阻态(Hi-Z)。

逻辑图真值表EN A OUT0 0 Hi-Z0 1 Hi-Z1 0 01 1 1波形图2.OC门,又名集电极开路门(opndrn)用途:集电极开路门(OC门)是一种用途广泛的门电路。

典型应用是可以实现线与的功能。

逻辑图真值表A B0 01 Hi-Z波形图四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:1、编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

VHDL 设计源代码如下:三态门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tri_s ISPORT (enable,datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END tri_s;ARCHITECTURE bhv OF tri_s ISBEGINPROCESS (enable,datain)BEGINIF enable='1' THEN dataout<=datain;ELSE dataout<='Z';END IF;END PROCESS;END bhv;OC门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY oc ISPORT(datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END oc;ARCHITECTURE bhv OF oc ISBEGINPROCESS (datain)BEGINIF (datain='0') THEN dataout<='0';ELSE dataout<='Z';END IF;END PROCESS;END bhv;2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

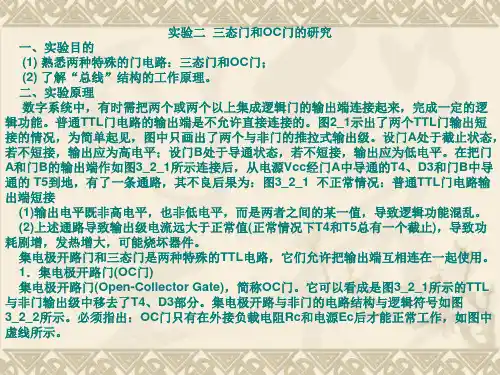

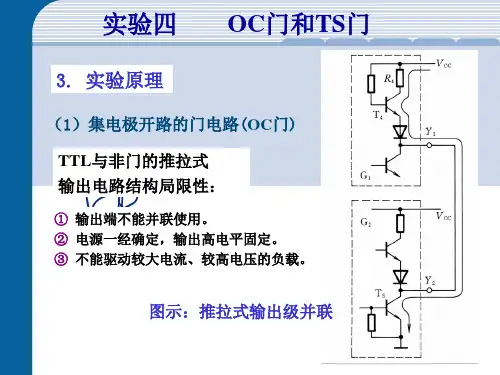

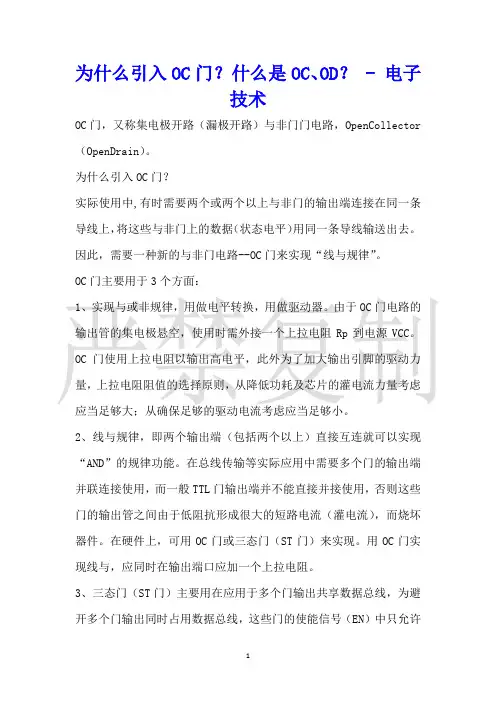

为什么引入OC门?什么是OC、OD? - 电子技术OC门,又称集电极开路(漏极开路)与非门门电路,OpenCollector (OpenDrain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与规律”。

OC门主要用于3个方面:1、实现与或非规律,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动力量,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流力量考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与规律,即两个输出端(包括两个以上)直接互连就可以实现“AND”的规律功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避开多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

什么是OC、OD?集电极开路门(集电极开路OC或漏极开路OD)Open-Drain是漏极开路输出的意思,相当于集电极开路(Open-Collector)输出,即TTL中的集电极开路(OC)输出。

一般用于线或、线与,也有的用于电流驱动。

Open-Drain是对MOS管而言,Open-Collector是对双极型管而言,在用法上没啥区分。

开漏形式的电路有以下几个特点:a.利用外部电路的驱动力量,削减IC内部的驱动。

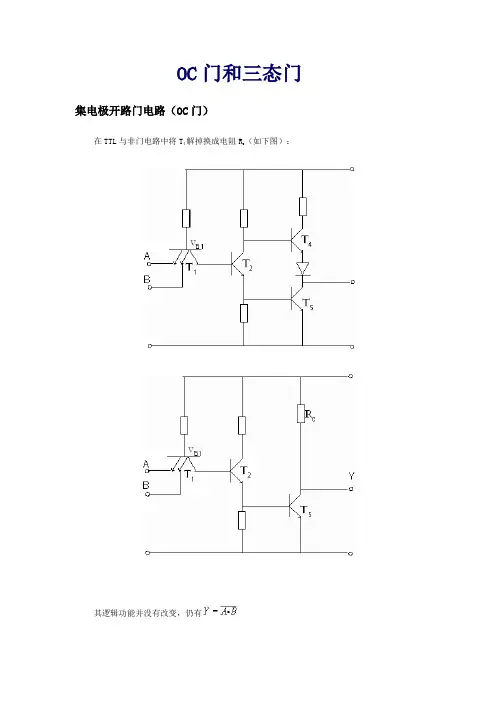

OC门和三态门集电极开路门电路(OC门)在TTL与非门电路中将T4解掉换成电阻R c(如下图):其逻辑功能并没有改变,仍有A=B=1, T5导通,输出端为低电平Y=0。

A、B中只要有一个0, T5截止,输出端为高电平5V(TTL与非门输出高电平Yv OH=3.6V),Y=1。

由R4取代T4,显然逻辑功能未变,但速度大为降低。

把R4不做在集成电路的内部(T5的集电极处于开路状态),使用OC门集成块时,用户必须选定合适的阻值,将R c接到门的输出端与电源之间,该OC门才能具有稳定的逻辑功能(如不把R c接进去,任其集电极开路,该电路不具备正常的逻辑功能)。

这种电路称为集电极开路门电路——简称OC门。

用如下符号表示:OC门的最大特点是具有线与功能。

几个OC门共用一个R c(输出端并接在一起),其输出为单个OC门输出之积(与)。

可以等于也可以大于v cc。

三态输出门电路(TS(Three-state output Gate)门)上图为三态门输出门电路的原理图。

在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。

普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。

T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。

三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。

因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(v cc)阻抗无穷大。

因此这第三种状态也称高阻状态。

现对三种状态进行分析:控制信号可在E N处加入,也可在处加入:E N=0,=1,则C=0,v B1=0.9V,v c2=0.9Vv B4=v c2=0.9V,T4截止(T4导通的电位v B4>1.4V)v B1=0.9V,T5截止,输出端Y为高阻状态。

E N=1,=0,C=1,对与非门另两个A、B输入端无影响,为正常的与非门电路。

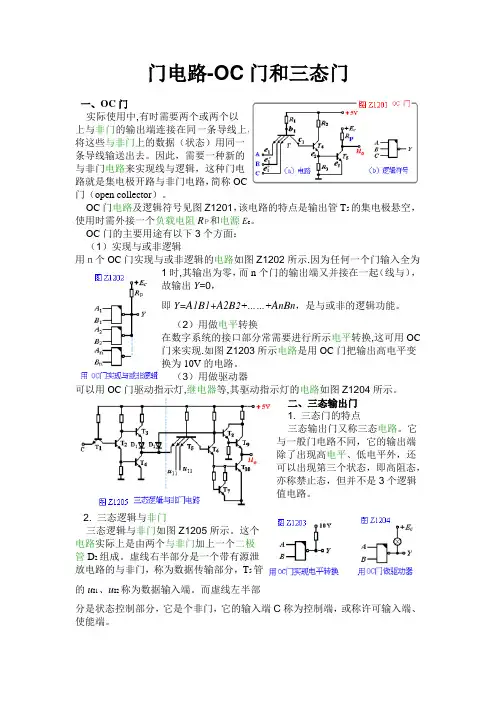

门电路-OC门和三态门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。

因此,需要一种新的与非门电路来实现线与逻辑,这种门电路就是集电极开路与非门电路,简称OC门(open collector)。

OC门电路及逻辑符号见图Z1201,该电路的特点是输出管T5的集电极悬空,使用时需外接一个负载电阻RP和电源E c。

OC门的主要用途有以下3个方面:(1)实现与或非逻辑用n个OC门实现与或非逻辑的电路如图Z1202所示.因为任何一个门输入全为1时,其输出为零,而n个门的输出端又并接在一起(线与),故输出Y=0,即Y=A1B1+A2B2+……+A n B n,是与或非的逻辑功能。

(2)用做电平转换在数字系统的接口部分常需要进行所示电平转换,这可用OC门来实现.如图Z1203所示电路是用OC门把输出高电平变换为10V的电路。

(3)用做驱动器可以用OC门驱动指示灯,继电器等,其驱动指示灯的电路如图Z1204所示。

二、三态输出门1. 三态门的特点三态输出门又称三态电路。

它与一般门电路不同,它的输出端除了出现高电平、低电平外,还可以出现第三个状态,即高阻态,亦称禁止态,但并不是3个逻辑值电路。

2. 三态逻辑与非门三态逻辑与非门如图Z1205所示。

这个电路实际上是由两个与非门加上一个二极管D2组成。

虚线右半部分是一个带有源泄放电路的与非门,称为数据传输部分,T5管的u I1、u I2称为数据输入端。

而虚线左半部分是状态控制部分,它是个非门,它的输入端C称为控制端,或称许可输入端、使能端。

当C端接低电平时,T4输出一个高电平给T5,使虚线右半部分处于工作状态,这样,电路将按与非关系把u I1,u I2接受到的信号传送到输出端,使u0或为高电平,或为低电平。

当C端接高电平时,T4输出低电平给T5,使T6、T7、T10截止。

另一方面,通过D2把T8的基极电位钳在1v左右,使T9截止。

锁存器:输出端的状态不会随输入端的状态变化而变化,只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。

通常只有0和1两个值。

典型的逻辑电路是D触发器。

缓冲器:多用在总线上,提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。

三态缓冲器就是典型的线与逻辑器件,可允许多个器件挂在一条总线上,当然OC输出也可用在线与逻辑应用上。

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:实现与或非逻辑,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

三态门(ST门),主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector (Open Drain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:1、实现与或非逻辑,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC 门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。

因此,需要一种新的与非门电路来实现线与逻辑,这种门电路就是集电极开路与非门电路,简称OC 门(open collector)。

OC门电路及逻辑符号见图T1119,该电路的特点是输出管T5的集电极悬空,使用时需外接一个负载电阻R和电源Ec。

POC门的主要用途有以下3个方面:(1)实现与或非逻辑用n个OC门实现与或非逻辑的电路如图T1120所示.因为任何一个门输入全为1时,其输出为零,而n个门的输出端又并接在一起(线与),故输出Y=0,即Y=A1B1+A2B2+……+A nB n,是与或非的逻辑功能。

oc门和三态门实验

TTL三态门和OC门(也可以称为集电极开路门或漏极开路门)都是集成电路门电路的输出类型,它们之间的主要区别在于输出电压的处理方式和用途。

TTL三态门:

TTL三态门是一种具有三个工作状态的门电路,即高电平、低电平和高阻态。

在高阻态时,输出晶体管是断开的,因此输出端对地和电源电压来说都是高阻抗的,即相当于输出端与输入端完全断开。

这种门电路通常用于多路复用和双向总线应用,以及需要避免线与(线路上的电位冲突)的应用。

OC门:

OC门是一种具有推挽输出的门电路,其输出晶体管在饱和时具有较低的电阻,使得输出电压可以接近电源电压。

与TTL三态门不同的是,OC门的输出端在饱和时是低阻抗的。

因此,OC门通常用于需要高电流输出的应用,如驱动LED、电机等。

此外,OC门还可以通过将多个门的输出并联起来,实现“线与”逻辑。

在这种配置下,当所有门的输出都为高电平时,输出为低电平;而当至少一个门的输出为低电平时,输出也为低电平。

这种特性在实现多路复用、解码器等功能时非常有用。

总结来说,TTL三态门和OC门的主要区别在于输出电路的处理方式和用途。

TTL三态门适用于需要高阻态的三态输出的应用,如多路复用和双向总线;而OC门适用于需要高电流输出的应用,如驱

动LED、电机等,并可以通过并联实现“线与”逻辑。

实验二 OC 门和三态门的应用一、实验目的1.能够正确使用数字电路实验系统。

2.掌握TTL 三态门的逻辑应用。

3.掌握TTL OC 门的逻辑应用4.熟悉TTL 三态门、OC 门电路应用的测试方法。

二、实验原理三态门工作时,有三种输出状态0态、1态、高阻态。

当使能端 时三态门正常工作;当使能端 时三态门工作在高阻状态。

适当的利用三态门的控制端可实现单向数据传输总线。

OC 门为集电极开路的与非门,正常工作时要在输出端和电源之间外接电阻R L 才能完成与非功能。

利用多个OC 门输出端“线与”可完成“与或非”功能,从而使OC 门的与非功能得到了扩展。

三、实验内容与步骤1. 74LS125三态门应用测试74LS125三态门外引脚排列为图2.1所示。

利用三态门实现总线传输,实验电路见图2.2所示。

将三个三态门的输入端分别接高电平、地、连续脉冲。

根据三个开关S 1、S 2、S 3的不同状态(S 1、S 2、S 3中每次只允许有一个为低电平),观察输出端指示灯LED 的变化,体会三态门实现总线传输的作用。

切记:要先认清三态门的使能端( ),用逻辑开关使三个三态门的使能端全处于高电平(三态门全处于高阻状态),才允许接通电源。

然后,只能一个门工作,观测总线的逻辑状态。

观测结束,先使工作的三态门转换到高阻状态,再让另一个门开始工作。

否则,将损坏器件。

将测试结果填入表2.1。

表2.1 三态门实现总线传输功能表2.TTLOC门(74LS03)实现线与功能测试OC 门选用芯片74LS03,实验电路如图2.3,此电路构成了线与逻辑。

完成真值表2.2测试,根据真值表判断其逻辑功能。

注意R C 的选择(R=1K Ω,R P =1K Ω)。

输入 使能端(控制端) 输出S1 S2 S3 Y A 1(0V ) A 2(5V ) 连续脉冲 V CC EN 4 A 4 Y 4 EN 3 A 3 Y 374LS125EN 1 A 1 Y 1 EN 2 A 2 Y 2 GND14 813 12 9 10 111EN 1ENS 1 逻辑电平 S 2开 5V×A 1A 2 Y 1 Y 2LED EN , EN=1 EN=0表2.2 OC 门线与功能测试表输入逻辑状态Y 输出A B C D状态 电位(V ) 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 11图2.1 74LS125三态门外引脚排列图 图2. 2 利用三态门实现总线传R P RR CV CC & ◇& ◇A BC DG 1G 2Y 1Y 2}&LED图2. 3 OC 门线与功能测试电路1 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1四、实验报告要求1.画出实验用各逻辑门的逻辑符号,并写出逻辑表达式。