数字电路实验 乘法器ppt课件

- 格式:ppt

- 大小:3.56 MB

- 文档页数:17

电路中的乘法器设计乘法器作为数字电路中重要的基本组件之一,被广泛应用于各种数字信号处理系统中。

乘法器的设计与优化对于提高性能、节省资源以及降低功耗都有着重要的价值。

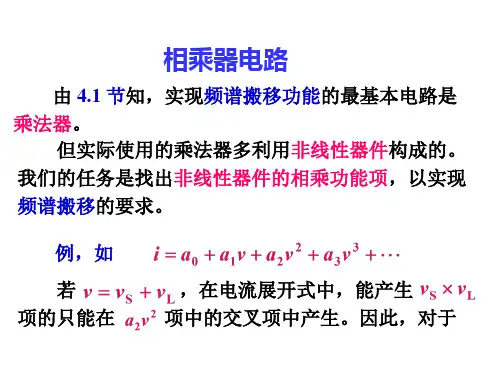

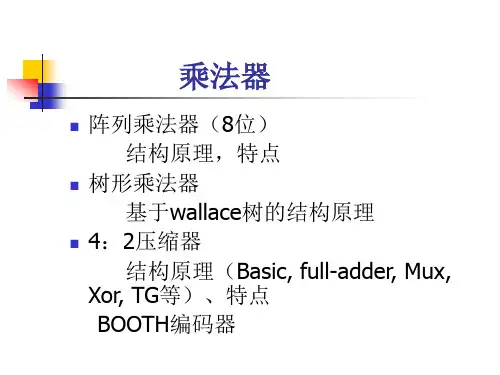

一、乘法器的原理和分类乘法器是一种将两个输入信号相乘并输出结果的电路。

在数字电路中,乘法器有多种不同的实现方式,常见的有布斯乘法器、波尔久杰斯基乘法器以及Wallace树乘法器等。

布斯乘法器是一种基于二进制补码运算的乘法器。

它通过将两个输入信号逐位相乘,并将结果相加得到最终的乘积。

此种乘法器的优点是结构简单,实现方便,但缺点是速度相对较慢。

波尔久杰斯基乘法器是一种通过分解乘法运算来提高速度的乘法器。

它将两个输入信号分别展开成若干个中间变量,并通过特定的组合电路将这些变量相乘,并最终将结果相加得到最终的乘积。

该乘法器相比布斯乘法器具有更快的运算速度,但需要更多的硬件资源。

Wallace树乘法器则是一种通过并行计算实现高速乘法的乘法器。

它将输入信号分组,并通过特定的组合电路实现了并行计算的功能,从而大大提高了运算速度。

然而,该乘法器在实现过程中,需要大量的硬件资源,且相对复杂。

二、乘法器的设计优化在实际乘法器的设计过程中,往往需要考虑多个因素,如运算速度、资源利用率、功耗以及抗干扰能力等。

为了达到更好的设计效果,我们可以采取一些优化策略。

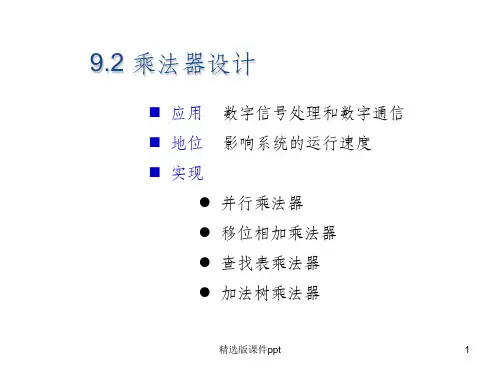

第一,使用合适的乘法算法。

不同的乘法算法在运算速度、资源利用率以及功耗等方面会有所不同,根据具体的应用需求选择合适的乘法算法是非常重要的。

第二,考虑并行计算。

众所周知,乘法操作是一个非常耗时的运算,可以通过并行计算的方式来提高运算速度。

比如,可以采用布斯树和Wallace树等并行计算的方法来实现高速乘法。

第三,精确控制电路延迟。

在进行乘法运算时,电路延迟是一个重要的因素,可以通过合理设计电路结构、选用合适的器件以及优化布线等方式来减少电路延迟,提高乘法器的运算速度。

第四,采用节能技术。

如今,节能已经成为电路设计不可忽视的因素之一。

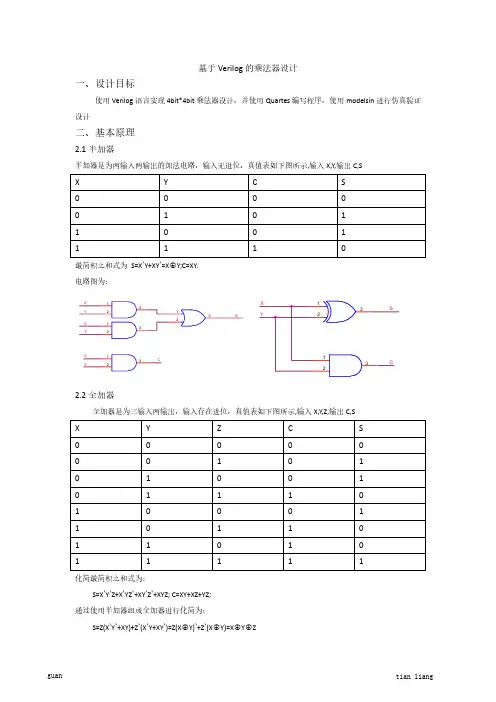

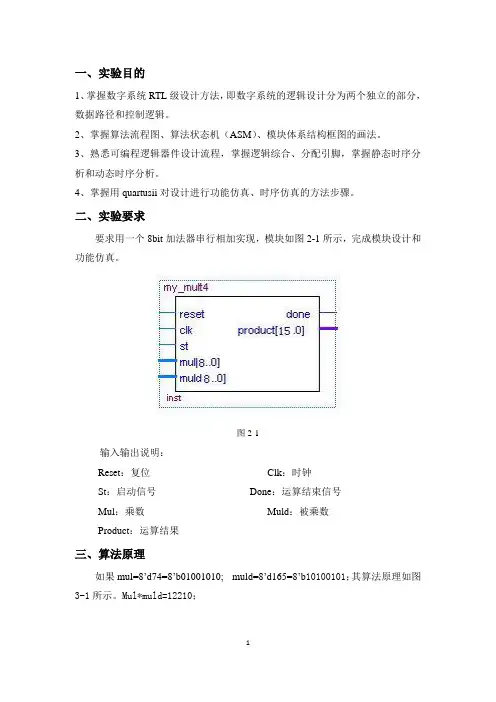

一、实验目的1、掌握数字系统RTL级设计方法,即数字系统的逻辑设计分为两个独立的部分,数据路径和控制逻辑。

2、掌握算法流程图、算法状态机(ASM)、模块体系结构框图的画法。

3、熟悉可编程逻辑器件设计流程,掌握逻辑综合、分配引脚,掌握静态时序分析和动态时序分析。

4、掌握用quartusii对设计进行功能仿真、时序仿真的方法步骤。

二、实验要求要求用一个8bit加法器串行相加实现,模块如图2-1所示,完成模块设计和功能仿真。

图2-1输入输出说明:Reset:复位Clk:时钟St:启动信号Done:运算结束信号Mul:乘数Muld:被乘数Product:运算结果三、算法原理如果mul=8’d74=8’b01001010; muld=8’d165=8’b10100101;其算法原理如图3-1所示。

Mul*muld=12210;MM图3-1四、模块算法流程图和结构框图说明:St:操作启动信号acc[16:0]: 累加器cnt: 移位计数器sum[8:0]: 加法器和muld: 8bit被乘数muL: 8bit乘数结果放在acc[15:0]中图4-1模块算法流程图图4-1是模块算法流程图,其原理如下:1、开始后,先判断st是否为1,如果st=1,则移位寄存器清零,把乘数加载到累加器的低八位。

如果,st=0,程序不能往下进行,继续判断st是否为1,直到st=1,为止。

2、把累加器的高九位和被乘数相加和赋给加法器。

3、判断累加器的最低位是否为1,若为1,把加法器的和赋给累加器的高九位,然后累加器右移一位,否则累加器直接右移一位。

4、判断cnt是否为7,如果为7,则,这次乘法运算完成,返回第1步,重新开始。

否则,cnt加1,并返回第2步。

图4-2 模块体系结构框图信号说明:clk:同步时钟load:数据加载信号right:ACC右移信号ad_update:ACC[16:8]更新信号done:结束信号st:开始信号M:乘数值信号图4-2是其模块体系结构图,它有两个模块组成控制逻辑模块和数据路径模块,数据路径模块是输入数据的处理单元,一般完成数据的算数运算、逻辑运算和移位等操作,主要由加法器、逻辑运算单元、译码器、多路选择器、计数器、移位寄存器和数据寄存器等器件构成,本模块,它只有加法器和移位寄存器单元。