数字电路实验报告实验二PPT课件

- 格式:ppt

- 大小:2.49 MB

- 文档页数:13

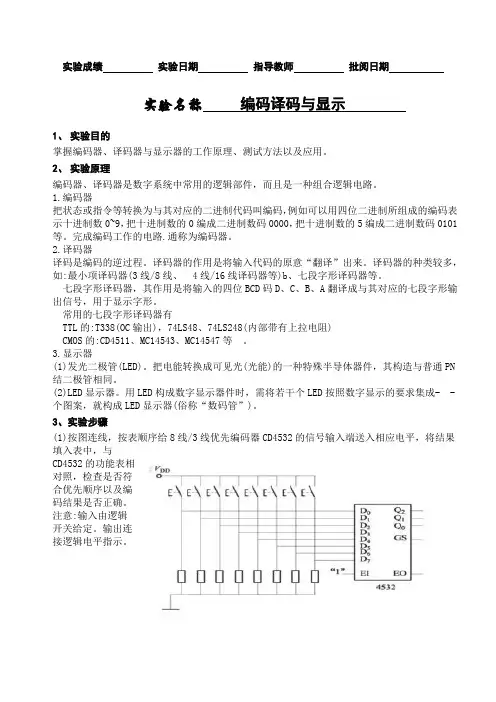

实验成绩实验日期指导教师批阅日期实验名称编码译码与显示1、实验目的掌握编码器、译码器与显示器的工作原理、测试方法以及应用。

2、实验原理编码器、译码器是数字系统中常用的逻辑部件,而且是一种组合逻辑电路。

1.编码器把状态或指令等转换为与其对应的二进制代码叫编码,例如可以用四位二进制所组成的编码表示十进制数0~9,把十进制数的0编成二进制数码0000,把十进制数的5编成二进制数码0101等。

完成编码工作的电路.通称为编码器。

2.译码器译码是编码的逆过程。

译码器的作用是将输入代码的原意“翻译”出来。

译码器的种类较多,如:最小项译码器(3线/8线、4线/16线译码器等)b、七段字形译码器等。

七段字形译码器,其作用是将输入的四位BCD码D、C、B、A翻译成与其对应的七段字形输出信号,用于显示字形。

常用的七段字形译码器有TTL的:T338(OC输出),74LS48、74LS248(内部带有上拉电阻)CMOS的:CD4511、MC14543、MC14547等。

3.显示器(1)发光二极管(LED)。

把电能转换成可见光(光能)的一种特殊半导体器件,其构造与普通PN 结二极管相同。

(2)LED显示器。

用LED构成数字显示器件时,需将若干个LED按照数字显示的要求集成- -个图案,就构成LED显示器(俗称“数码管”)。

3、实验步骤(1)按图连线,按表顺序给8线/3线优先编码器CD4532的信号输入端送入相应电平,将结果填入表中,与CD4532的功能表相对照,检查是否符合优先顺序以及编码结果是否正确。

注意:输入由逻辑开关给定。

输出连接逻辑电平指示。

(2)根据CD4532和CD4511的管脚图和功能表,自行设计连线,将编码器CD4532的输出端接到译码器CD4511的数据输入端,将CD4511的输出接七段显示数码管。

检查编码器与数字显示是否一致,若不一致,分析原因,检查故障并排除之,将结果填表。

(3)将十进制计数器/脉冲分配器CD4017接成八进制,用单次脉冲或1Hz脉冲信号检查CD4017的逻辑功能是否正常。

实验二 译码器及其应用一、 实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

4、学习译码器的扩展。

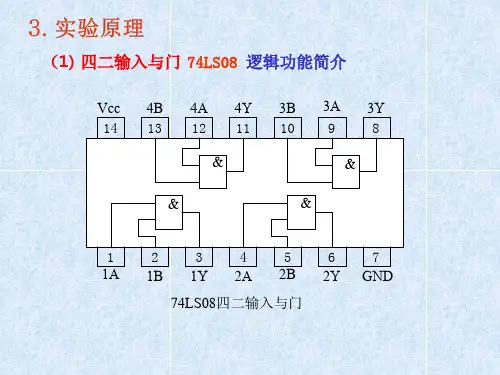

二、 实验设备及器件1、数字逻辑电路实验板1块 2、74HC(LS)20(二四输入与非门) 1片 3、74HC(LS)138(3-8译码器)2片三、 实验原理74HC(LS)138是集成3线-8线译码器,在数字系统中应用比较广泛。

下图是其引脚排列,其中A 2、A 1、A 0为地址输入端,Y ̅0~Y ̅7为译码输出端,S 1、S ̅2、S ̅3为使能端。

下表为74HC(LS)138功能表。

74HC(LS)138工作原理为:当S 1=1,S ̅2+S ̅3=0时,电路完成译码功能,输出低电平有效。

其中:Y ̅0=A ̅2A ̅1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅4=A 2A ̅1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅1=A ̅2A ̅1A 0̅̅̅̅̅̅̅̅̅̅ Y ̅5=A 2A ̅1A 0̅̅̅̅̅̅̅̅̅̅ Y ̅2=A ̅2A 1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅6=A 2A 1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅3=A ̅2A 1A 0̅̅̅̅̅̅̅̅̅̅Y ̅7=A 2A 1A 0̅̅̅̅̅̅̅̅̅̅因为74HC(LS)138的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项(的非),因此可以利用八条输出线组合构成三变量的任意组合电路。

实验用器件管脚介绍:1、74HC(LS)20(二四输入与非门)管脚如下图所示。

2、74HC(LS)138(3-8译码器)管脚如下图所示。

四、实验内容与步骤(四学时)1、逻辑功能测试(基本命题)m。

验证74HC(LS)138的逻辑功能,说明其输出确为最小项i注:将Y̅0~Y̅7输出端接到LED指示灯上,因低电平有效,所以当输入为000时,Y̅0所接的LED指示灯亮,其他同理。

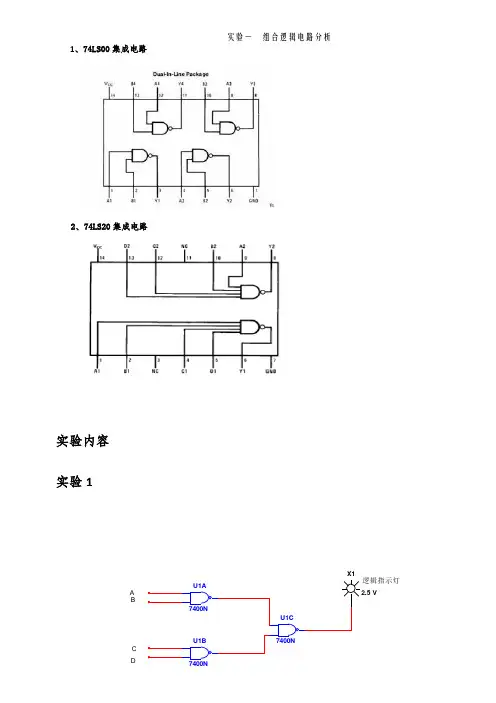

实验一组合逻辑电路分析1、74LS00集成电路2、74LS20集成电路实验内容实验1X1A BC D逻辑指示灯实验2密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。

否则,报警信号为“1”,则接通警铃。

试分析密码锁的密码ABCD 是什么? 答:由下表可知密码ABCD 是1001。

X1X2ABC D报警实验心得:1、 通过这次试验了解到了74LS00与非门及74LS20与非门的使用方法。

2、 熟悉了实验面板,及实验过程,为以后试验打下一个基础。

3、 熟悉了逻辑电平的接入方法。

4、 熟悉了基本逻辑电路的分析方法及步骤。

实验二 组合逻辑实验(一)半加器和全加器一、实验目的1.熟悉用门电路设计组合电路的原理和方法步骤。

二、预习内容1.复习用门电路设计组合电路的原理和方法步骤。

2.复习二进制的运算。

①用“与非“门设计半加器逻辑图。

②完成用“异或”门、“与或非”门、“与非”门设计全加器逻辑图。

③完成用“异或”门设计的3变量判奇电路的原理图。

三、参考元件74LS238 74LS00 74LS51 74LS136四、实验内容1.用与非门组成半加器,用异或门、与或非门、与非门组成全加器。

实验结果填入下表中:ABSCI半加器VCCABSCi2.实验结果填入下表中:ABL实验心得1.本实验主要使用74LS00与74LS51来设计半加器与全加器以及判奇电路,在实验中熟悉了这两个元件的使用方法。

加深了我对理论课知识的理解。

2.半加器不带前级进位,全加器带前级进位。

3.设计组合逻辑电路前先列写逻辑表达式,然后根据逻辑表达式连接电路。

实验三 组合逻辑实验(二)数据选择器和译码器的应用一、 实验目的熟悉数据选择器和数据分配器的逻辑功能和掌握其使用方法二、 预习内容1. 了解所有元器件的逻辑功能和管脚排列。

2. 复习有关数据选择器和译码器的内容。

3. 用八选一数据选择器产生逻辑函数L ABC ABC ABC ABC =+++和L A B C =⊕⊕4. 用3线-8线译码器和与非门构成一个全加器。

实验二常用电子仪器的使用

一、实验目的

掌握常用的电子仪器(示波器、函数信号发生器、直流稳压电源、数字万用表等)的主要技术指标、性能及正确使用方法。

二、实验条件,设备,器材

示波器、函数信号发生器、直流稳压电源、数字万用表。

三、实验原理

输入的电信号通过一个ADC(通常采用8bits 或者256个量化电平)数字化,输出的数据存储在示波器的存储器中。

数字化速率和放大器频宽决定所能精确地取样和显示的最快信号。

四、实验内容

1、示波器探头校正

2、测量并记录实验箱5M、1M、500K、100K连续脉冲源;

3、使用信号发生器产生50M、1M、1K正弦波、方波等信号。

五、实验步骤及数据记录

1.示波器探头校正

将示波器探头接【Probe Comp】; 使用【Auto Scale】; 测量、记录相关数据并保存波形图像。

2.测量并记录实验箱连续脉冲源

测量、记录相关数据并保存波形图像。

3.使用信号发生器产生相关信号并测量

使用信号发生器产生50M、1M、10K、1K正弦波、方波等信号

六、实验分析,结论,体会

通过本次实验,初步掌握了常用的电子仪器(示波器、函数信号发生器、直流稳压电源、数字万用表等)的主要技术指标、性能及正确使用方法。

数字电子技术实验报告2021 -2021学年第一学期XX:陶瑜学号:2021111990班级:计算机科学与技术三班座位号:31实验时间:周四下午第二讲实验指导教师:龙文杰实验2原理图:实验3代码:module ty_2021111990_3(codeout,indec);input[3:0] indec;output [6:0] codeout;reg[6:0]codeout;always(indec)begincase(indec)4'd0:codeout=7'b1111110;4'd1:codeout=7'b0110000;4'd2:codeout=7'b1101101;4'd3:codeout=7'b1110001;4'd4:codeout=7'b0110011;4'd5:codeout=7'b1011011;4'd6:codeout=7'b1011111;4'd7:codeout=7'b1110000;4'd8:codeout=7'b1111111;4'd9:codeout=7'b1111011;default: codeout=7'bx;endcaseendendmodule实验4原理图和波形图:实验5原理图和波形图:实验6原理图和波形图:实验6代码:1:计数器module jishuqi(d,clk,clr,load,ud,q,cout); parameter n=4;input[n-1:0] d;input clk,clr,load,ud;output reg[n-1:0] q;output cout;assign cout=(ud&(q==9))|(~ud&(q==0)); always (posedge clk,negedge clr)if(!clr)q<=0;else if(load)q<=d;else if(ud)if(q<9) q<=q+1;else q<=0;elseif(q>0) q<=q-1;else q<=9;endmodule2:7段译码器:module decode4_7(a,b,c,d,e,f,g,q);input[3:0]q;output a,b,c,d,e,f,g;reg[6:0]codeout;always (q)begincase(q)4'd0:codeout=7'b1111110;4'd1:codeout=7'b0110000;4'd2:codeout=7'b1101101;4'd3:codeout=7'b1110001;4'd4:codeout=7'b0110011;4'd5:codeout=7'b1011011;4'd6:codeout=7'b1011111;4'd7:codeout=7'b1110000;4'd8:codeout=7'b1111111;4'd9:codeout=7'b1111011;default: codeout=7'bx;endcaseendassign {a,b,c,d,e,f,g} = codeout[6:0]; endmodule实验7原理图和波形图:实验7代码:1.分频器module divfreq(clk,out); input clk;output reg out;reg [12:0] q5000;always (posedge clk)beginif(q5000<=2499)beginout<=1;q5000<=q5000+1;endelse if (q5000<4999)beginout<=0;q5000<=q5000+1;endelseq5000<=0;endendmodule2.计数器module counter100(set,out,out2,q100); output reg out2;input out;input [6:0] set; output reg [7:0] q100; always (posedge out) beginif (q100<set) beginout2<=1;q100<=q100+1; endelse if (q100<99) beginout2<=0;q100<=q100+1; endelse q100<=0; endendmodule。