数字电路实验 乘法器 ppt课件

- 格式:ppt

- 大小:4.00 MB

- 文档页数:16

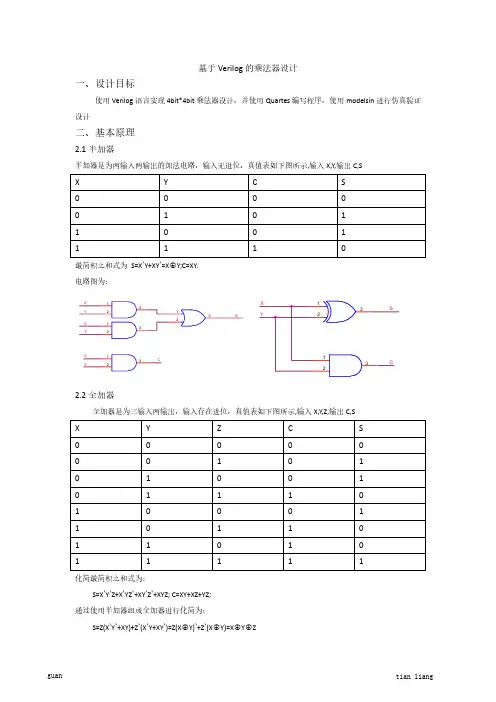

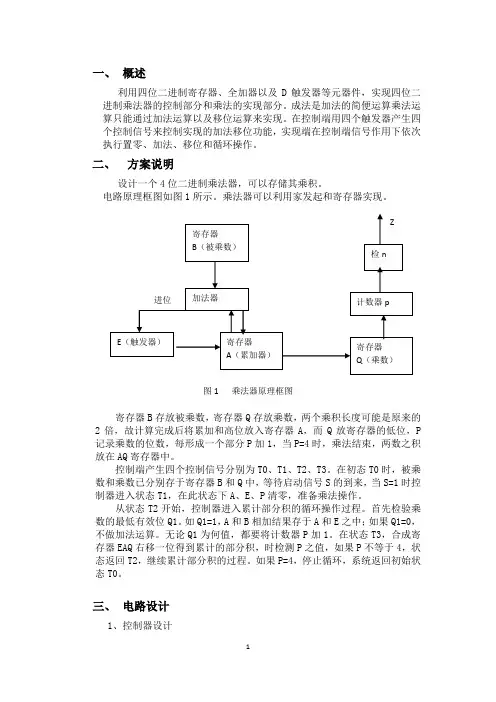

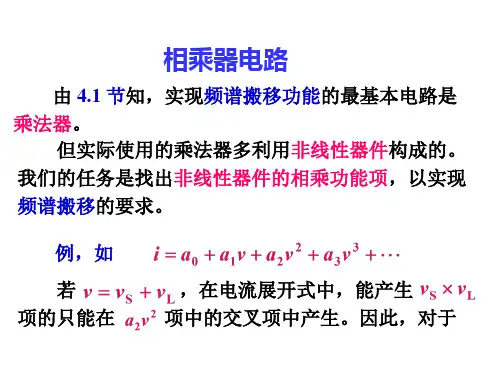

一、概述利用四位二进制寄存器、全加器以及D触发器等元器件,实现四位二进制乘法器的控制部分和乘法的实现部分。

成法是加法的简便运算乘法运算只能通过加法运算以及移位运算来实现。

在控制端用四个触发器产生四个控制信号来控制实现的加法移位功能,实现端在控制端信号作用下依次执行置零、加法、移位和循环操作。

二、方案说明设计一个4位二进制乘法器,可以存储其乘积。

电路原理框图如图1所示。

乘法器可以利用家发起和寄存器实现。

图1 乘法器原理框图寄存器B存放被乘数,寄存器Q存放乘数,两个乘积长度可能是原来的2倍,故计算完成后将累加和高位放入寄存器A,而Q放寄存器的低位,P 记录乘数的位数,每形成一个部分P加1,当P=4时,乘法结束,两数之积放在AQ寄存器中。

控制端产生四个控制信号分别为T0、T1、T2、T3。

在初态T0时,被乘数和乘数已分别存于寄存器B和Q中,等待启动信号S的到来,当S=1时控制器进入状态T1,在此状态下A、E、P清零,准备乘法操作。

从状态T2开始,控制器进入累计部分积的循环操作过程。

首先检验乘数的最低有效位Q1。

如Q1=1,A和B相加结果存于A和E之中;如果Q1=0,不做加法运算。

无论Q1为何值,都要将计数器P加1。

在状态T3,合成寄存器EAQ右移一位得到累计的部分积,时检测P之值,如果P不等于4,状态返回T2,继续累计部分积的过程。

如果P=4,停止循环,系统返回初始状态T0。

三、电路设计1、控制器设计根据图2所示的ASM图表,可以设计二进制乘法器的控制器。

图2 二进制乘法器ASM图表四个D触发器的驱动方程为:D0=T0S’+T3Z=((T0S’)’·(T3Z)’)’D1=T0S=((T0S)’)’D2=T1+T3Z’=(T1’·(T3Z’)’)’D3=T2控制器仿真电路如图2所示。

控制器中S为启动信号,高电平有效,系统开始工作时应使T0=1,T1=T2=T3=0,故图中设置了Reset信号(负脉冲)图2 二进制乘法器的控制逻辑图2. 二进制乘法器数据处理器(1) A寄存器A寄存器具有并入、移位、同步清0和保持功能。

数字乘法器第5章组合逻辑电路设计5.1 基本门电路的设计5.2 数据选择器的设计5.3 1对2数据分配器的设计5.4 4位BCD译码器的设计5.5 三态门的设计5.6 半加器的设计5.7 全加器的设计5.8 6位加法器的设计5.9 4位加减法器的设计5.10 3位乘法器的设计习题5.1 基本门电路的设计基本门电路主要用来实现基本的输入/输出之间的逻辑关系,包括与门、非门、或门、与非门、或非门、异或门、同或门等,下面以2输入端与非门为例讲解基本门电路的设计。

1.实验原理表5-1 2输入端与非门的真值表2输入端与非门是组合逻辑电路中的基本逻辑器件,有2个输入端A、B和1个输出端C。

其真值表如表5-1所示。

2输入端与非门应具备的脚位:输入端:A、B;输出端:C。

表5-1 2输入端与非门的真值表输入端输出端A B C 001 011 101 1102.原理图输入与非门原理图输入法的操作步骤介绍如下。

(1) 建立新文件:选取窗口菜单File→New,出现对话框,选择Graphic Editor file选项,单击OK按钮,进入图形编辑画面。

(2) 保存:选取窗口菜单File→Save,出现对话框,键入文件名nand2.gdf,单击OK按钮。

(3) 指定项目名称,要求与文件名相同:选取窗口菜单File→Project→Name,键入文件名nand2,单击OK 按钮。

(4) 确定对象的输入位置:在图形窗口内单击鼠标左键。

(5) 引入逻辑门:选取窗口菜单Symbol→Enter Symbol,在\Maxplus2\max2lib\prim处双击,在Symbol File菜单中选取NAND2逻辑门,单击OK按钮。

(6) 引入输入和输出脚:按步骤(5)选出2个输入脚和1个输出脚。

(7) 更改输入和输出脚的脚位名称:在PIN_NAME处双击鼠标左键,进行更名,输入脚为A、B,输出脚为C。

(8) 连接:将A、B脚连接到与非门的输入端,C 脚连接到与非门的输出端,如图5-1所示。