硬件设计需求分析Checklist

- 格式:xls

- 大小:41.00 KB

- 文档页数:1

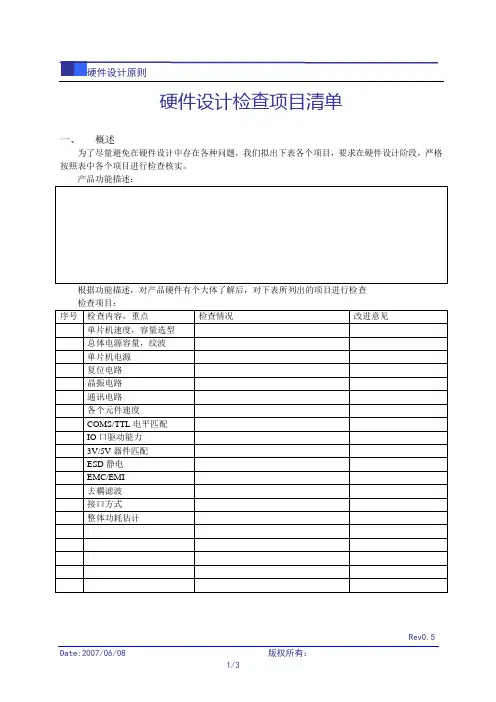

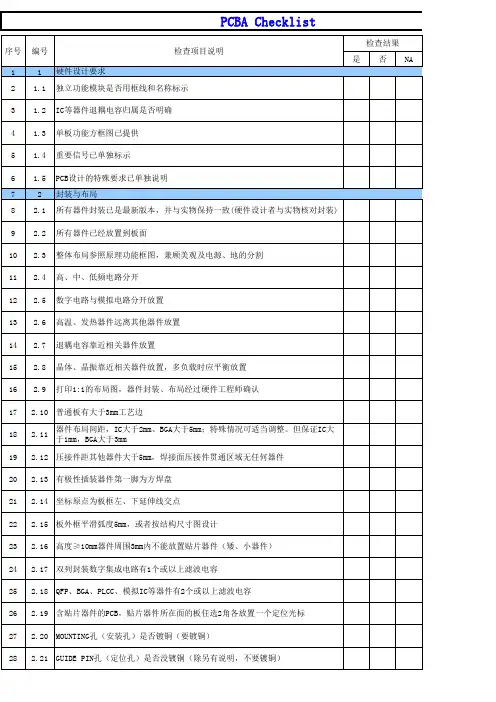

硬件设计检查项目清单一、概述为了尽量避免在硬件设计中存在各种问题,我们拟出下表各个项目,要求在硬件设计阶段,严格按照表中各个项目进行检查核实。

产品功能描述:根据功能描述,对产品硬件有个大体了解后,对下表所列出的项目进行检查检查项目:序号检查内容,重点检查情况改进意见单片机速度,容量选型总体电源容量,纹波单片机电源复位电路晶振电路通讯电路各个元件速度COMS/TTL电平匹配IO口驱动能力3V/5V器件匹配ESD静电EMC/EMI去耦滤波接口方式整体功耗估计二、基本原则系统的扩展和配置应遵循以下原则:1、尽可能选择典型电路,并符合单片机常规用法。

为硬件系统的标准化、模块化打下良好的基础。

2、系统扩展与外围设备的配置水平应充分满足应用系统的功能要求,并留有适当余地,以便进行二次开发。

3、硬件结构应结合应用软件方案一并考虑。

硬件结构与软件方案会产生相互影响,考虑的原则是:软件能实现的功能尽可能由软件实现,以简化硬件结构。

但必须注意,由软件实现的硬件功能,一般响应时间比硬件实现长,且占用CPU时间。

4、系统中的相关器件要尽可能做到性能匹配。

选用CMOS芯片单片机构成低功耗系统时,系统中所有芯片都应尽可能选择低功耗产品。

3V器件与5V器件之间的匹配;速度EMC/EMI5、可靠性及抗干扰设计是硬件设计必不可少的一部分,它包括芯片、器件选择、去耦滤波、印刷电路板布线、通道隔离等。

6、单片机外围电路较多时,必须考虑其驱动能力。

驱动能力不足时,系统工作不可靠,可通过增设线驱动器增强驱动能力或减少芯片功耗来降低总线负载。

7、尽量朝“单片”方向设计硬件系统。

系统器件越多,器件之间相互干扰也越强,功耗也增大,也不可避免地降低了系统的稳定性。

随着单片机片内集成的功能越来越强,真正的片上系统SoC已经可以实现,8、在混合电源系统中,要考虑二者的电平匹配问题。

如MCU是3.3V,外设是5V,就要考虑2者之间线的电平匹配问题,通常情况可以将MCU 的IO设置为开漏模式,并上拉到5V,如果有必要增加电平转换芯片。

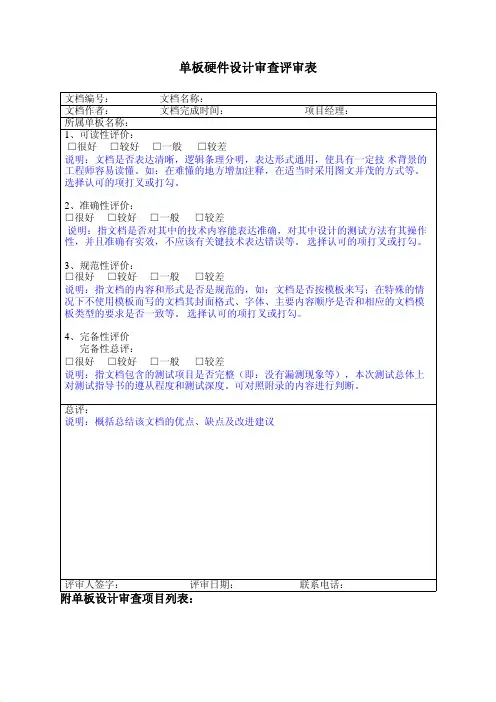

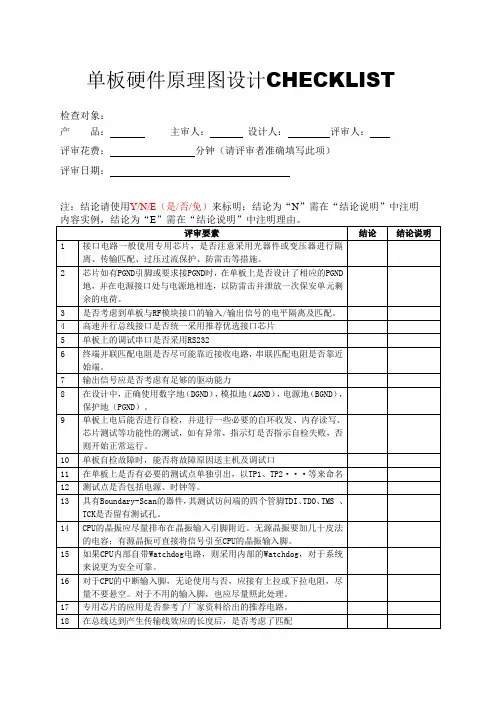

单板硬件设计审查评审表文档编号:文档名称:文档作者:文档完成时间:项目经理:所属单板名称:1、可读性评价:□很好□较好□一般□较差说明:文档是否表达清晰,逻辑条理分明,表达形式通用,使具有一定技术背景的工程师容易读懂。

如:在难懂的地方增加注释,在适当时采用图文并茂的方式等。

选择认可的项打叉或打勾。

2、准确性评价:□很好□较好□一般□较差说明:指文档是否对其中的技术内容能表达准确,对其中设计的测试方法有其操作性,并且准确有实效,不应该有关键技术表达错误等。

选择认可的项打叉或打勾。

3、规范性评价:□很好□较好□一般□较差说明:指文档的内容和形式是否是规范的,如:文档是否按模板来写;在特殊的情况下不使用模板而写的文档其封面格式、字体、主要内容顺序是否和相应的文档模板类型的要求是否一致等。

选择认可的项打叉或打勾。

4、完备性评价完备性总评:□很好□较好□一般□较差说明:指文档包含的测试项目是否完整(即:没有漏测现象等),本次测试总体上对测试指导书的遵从程度和测试深度。

可对照附录的内容进行判断。

总评:说明:概括总结该文档的优点、缺点及改进建议评审人签字:评审日期:联系电话:附单板设计审查项目列表:请参照此表,审查过的项目请打(9),未审查的项目请打(x),单板无此审查项目可不填。

1.单元电路审查:1.1滤波电路审查1.审查电路中有无设计电源滤波器。

有无审查()2.审查电路中电源滤波器的形式是否有效,是否为单电容型或单电感型,而未采用П形电源滤波器。

有无审查()3.对单板的П形电源滤波器参数进行审查。

有无审查()1.2ID电路审查1.审查ID电路的形式是否符合规范电路的要求。

有无审查()2.审查ID电路的参数是否正确。

有无审查()3.审查ID电路是否有隔离电阻或隔离芯片。

有无审查()4.在沿用未能提供正确ID处理的旧母板时,单板是否进行相应的处理。

有无审查()1.3主备倒换电路审查1.审查主备倒换电路是否为主倒备型电路。

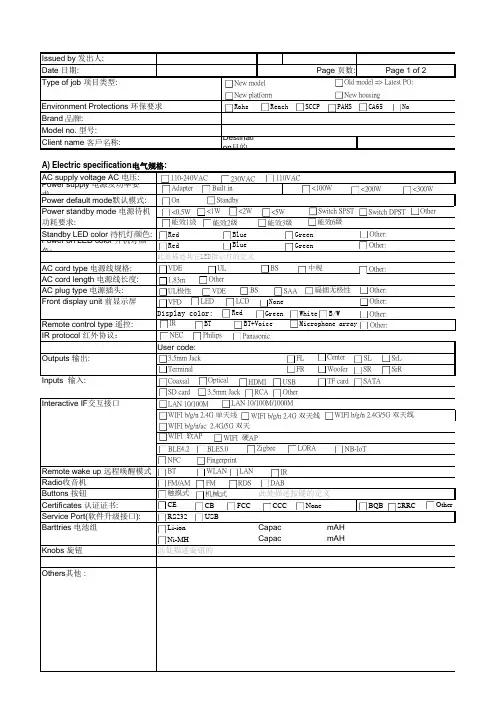

戴尔硬件pcb设计checklist 戴尔硬件PCB设计Checklist

1. PCB设计前准备

在进行PCB设计之前,需要做以下准备工作:

- 确定电路功能和性能需求

- 选择合适的元器件

- 制定PCB设计方案

- 准备好必要的设计工具和软件

2. PCB设计中的注意事项

在进行PCB设计时,需要注意以下事项:

- PCB板面积和厚度要与电路需求匹配

- PCB布线要合理,避免信号交叉和干扰

- PCB元器件布局要合理,尽量缩短元器件间距离

- PCB的供电系统要稳定,避免电压波动

- 为PCB添加必要的测试点和排查故障点

3. PCB设计后的检查

在完成PCB设计后,需要进行以下检查:

- 检查PCB的电路连接是否正确

- 检查PCB的电气性能是否满足要求

- 检查PCB的机械尺寸和板面尺寸是否符合要求

- 检查PCB的焊盘、锡膏、防护层等是否符合生产标准4. PCB设计后的优化

在完成PCB设计后,可以进行以下优化:

- 优化PCB的电路布线和元器件排布

- 优化PCB的供电系统和防护层

- 优化PCB的机械结构和布局

- 优化PCB的测试点和排查故障点

5. PCB设计的注意事项

在进行PCB设计时,需要注意以下事项:

- 所有元器件的电气性能参数应符合要求

- PCB的机械结构和尺寸应与产品需求匹配

- PCB的测试点和排查故障点要定位准确

- PCB的焊盘、锡膏、防护层等需要满足生产标准

6. 结论

通过以上的检查和优化,可以减少PCB设计中出现的故障和问题,并最终得到满足需求的电路板。

附录B (规范性附录)器件间距要求

表B.1

4 BGA外形与其他元器件的间隙≥

5 mm(200 mil)。

5 PLCC表面贴转接插座与其他元器件的间隙≥3 mm(120 mil)。

6 表面贴片连接器与连接器之间应该确保能够检查和返修。

一般连接器引线侧应该留有比连接器高度

大的空间。

7 元件到喷锡铜带(屏蔽罩焊接用)应该2mm(80mil)以上。

8 元件到拼板分离边需大于1mm(40mil)以上。

9 如果B面(焊接面)上贴片元件很多、很密、很小,而插件焊点又不多,建议插件引脚离开贴片元

件焊盘5mm以上,以便可以采用掩模夹具进行局部波峰焊。

注:其中间隙一般指不同元器件焊盘间的间隙,器件体大于焊盘时,指器件体的间隙)

附录C

(规范性附录)

内外层线路及铜箔到板边、非金属化孔壁的尺寸要求

表C.1单位:mm(mil) 板外形要素内层线路及铜箔外层线路及铜箔

距边最小尺寸一般边≥0.5(20) ≥0.5(20) 导槽边≥1(40) 导轨深+2

附录D (规范性附录)PCB布线最小间距

表D.1

附录E

(资料性附录)

丝印字符大小 (参考值)

表E.1。

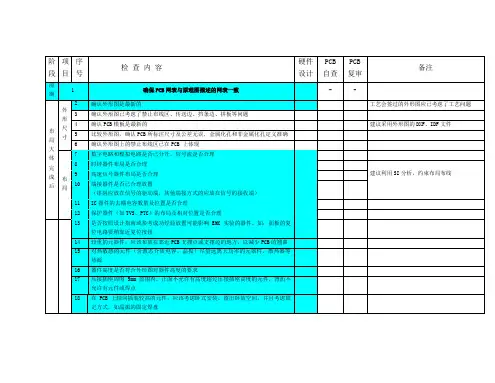

2: TTL信号和LVDS信号线之间是否相距一定距离(至少应该大于3~5倍差分线间距),减小直接串扰。

□是 □否 □无4:对于使用TTL和LVDS的系统,其电源之间是否用合适电感进行处理,以减小

TTL噪声进入LVDS系统。

□是 □否 □无5:对不用输入管脚是否按规范进行了处理。

□是 □否 □无6:对不用输出管脚,是否按规范进行了处理。

□是 □否 □无7:对高速LVDS器件使用,是否考虑了信号阻抗的匹配。

□是 □否 □无8:终端匹配元件是否要放在最靠近传输线末端的地方。

□是 □否 □无9:LVDS器件的电源管脚是否充分去藕,滤波电容的位置是否靠近电源和地管脚。

□是 □否 □无10:LVDS高速信号线上是否尽量避免了过孔。

□是 □否 □无11:LVDS高速信号线上是否避免了90度转折。

□是 □否 □无12:LVDS差分信号线是否做到电气等长和平衡。

□是 □否 □无13:LVDS信号是否有完整的参考地平面,保证有合理的回流路径。

□是 □否 □无14:电缆连接的情况下,电缆两端是否合理接地。

□是 □否 □无15:接插件中的LVDS信号的排布是否满足符合规范的原则。

□是 □否 □无

9。

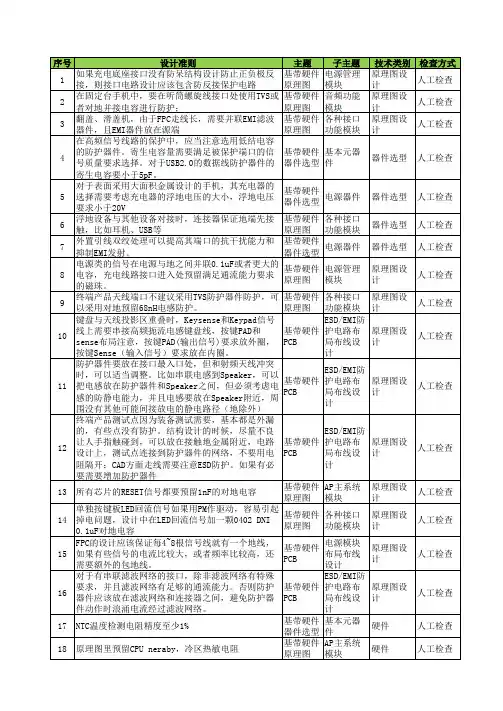

整机堆叠设计时应遵循热量分散的原则,手机整体框架结构是热性能的关键。

分析整机中主要发热的器件热阻及功耗,确认散热路径。

通常以下器件是主要的发热源:LCD的驱动芯片,喇叭,电池头部,高像素Camera,主板上的AP,PMIC,RF PA,WIFIPA,Tranceiver(MT6169在多个项目上实测温度都高于PA) 充电器件,背光驱动等大功率器件。

结构壳体厚度尽量减薄,以降低热阻,最好使用热阻较小的材料。

手机结构设计应保持内部具有良好的空气流通。

超薄机设计时,整机壳体应尽量采用大面积的金属结构件作为散热主体,例如采用A壳铝镁合金,金属后盖等。

主板采用半板,P型板等非整板设计时,A壳优选铝镁合金,其次为锌铝合金,最次为不锈钢片。

半版、P型板等非整板设计时,A壳不建议选用不锈钢片,散热的性能较差,节省的成本会转嫁到导热材料上。

(建议项,需踪合评估成本)整机堆叠设计硬件&结构热设计design guide项目检查项内容描述示意图导热材料设计项目检查项内容描述示意图检查结果导热材料选择导热率较高的材料,从性能上首选人工石墨,其次天热石墨,最后为铜箔;建议实际选用石墨的导热系数应≥1500W/m·K注:1.铜箔的散热参数约为400W/m·K,价格略低;2.天然石墨导热率为300~1500W/m·K,价格中等;3.人工石墨导热率为700~1900W/m·K,价格较高。

导热材料应能够覆盖温度高的部位,同时延伸到温度低的部分,将热量由温度高的位置传导到温度低的部分;必要时,可以增加导热材料的长度及宽度,大面积的延伸到整机温度低的部位。

使用导热材料时,导热材料应设计在B壳内侧,不可拆卸电池盖内侧,A壳金属面与PCB之间,芯片正上方,LCD铁框背面等位置。

整机温升较高时,应预留使用多层覆盖导热材料的方案,各层导热材料之间应保持一定的高度距离。

导热材料避免设计在电池盖,B壳外侧等位置,以免影响外观,长期使用磨损后导热效果下降。

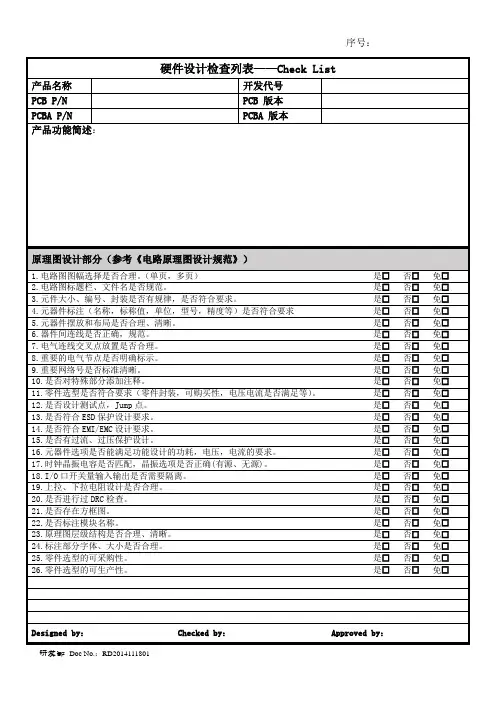

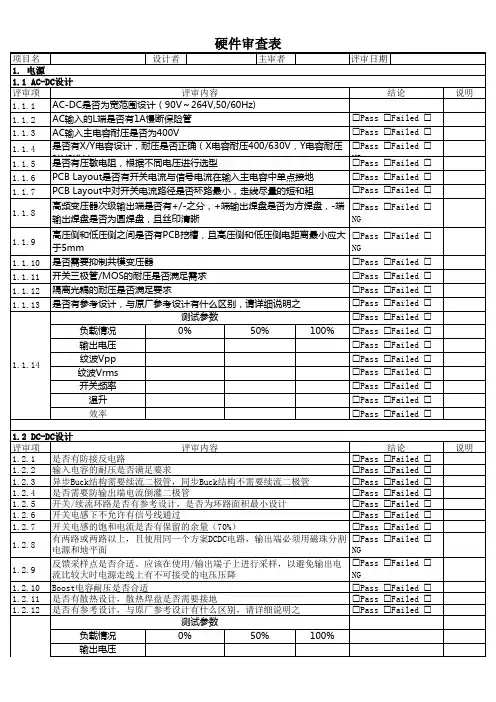

编号YES NO 不适用备注SA000SA001SA002SA003SA004SA005SA006SA007SB000SB001SB001SB002SC000对于不焊接、选择焊接或可调器件在其附近加文字备注并说明理由在相应位置添加兼容元器件的文字备注SB:器件选型原理图设计Checklist 灰色表示推荐参考的checklist 注明功率电阻,高耐压电容、变压器和保护器件(如压敏电阻,热敏电阻,ESD保护,放电管等)的关键指标和注意事项CHECKLIST要素集SA:文档格式与标注注明关键电路和元器件的重要参数。

如开关电源的频率、电感特性,隔离型DC-DC的隔离电压,晶体振荡器的负载电容,通用模块电路的功耗需求等原理图首页为版本信息说明。

包括版本号、版本修订记录、修订日期、修订人、详细修订内容和页数采用威胜信息通用原理图设计模版标注内容采用统一格式,字体为Courier New,粗体,字号不大于5号对于需要重点测试的关键网络添加测试点,文字备注不得选用已停产、即将停产、上市时间小于一年或供货周期大于八周的元器件物料和器件选型通过元件优选流程高压安规电容选型合理SC:封装不得选用唯一供应商供应的器件,必须有可替代性元器件型号,封装与生产厂家资料一致SC001SC002SD000SD001SD002SD003SD004SD005SD006SD007SD008SD009SD010SD011SD012SD013SD014SD015SD016SD017CPU的核心电源由LDO器件提供复位时,受控电源的电压不大于20%的额定电压值电源回路的电压范围设计合理电源回路各个电压的功率设计合理各类逻辑电平(如CMOS、TTL和LVTTL等)必须匹配CPU I/0、LED、继电器控制信号设计必须考虑芯片上电、复位时的状态电路设计有一定的扩展性器件原理图封装中,电源和地引脚不得隐藏如果硬件设计(或变更)涉及内核驱动设计(或相应变更)(如专用硬件资源分配、I/O功能定义、外部扩展地址分配等),硬件设计人员必须与内核组充分沟通、确认并达成共识。

XS1-L Hardware Design ChecklistDocument Revision1.3Publication Date: 2011/06/06Copyright©2011XMOS Limited,All Rights Reserved.1IntroductionThis document is intended for use by hardware designers using the XMOS XS1-L family of devices.It is a checklist of items that should be included in all XS1-L designs to ensure correct operation.For further details refer to the relevant device datasheet. 2ChecklistEach of the following sections contains items to check for each design using an XS1-L series device.2.1Ground PadThe centre ground pad for all XS1-L packages is the main device ground and must be connected to circuit ground.Multiple vias should be used from the centre pad to the circuit ground plane to minimise impedance and conduct heat away from the device.2.2Power supply sequencingThe VDDIO(and OTP_VDDIO if present)supply must be within specification(3.0V-3.6V)before the VDD(core)supply is turned on.Specifically,the VDDIO supplies should be within specification before VDD core reaches0.4V.2.3VDD ramp rateThe VDD(core)supply should ramp monotonically(constantly rising)from0V to its final value(0.95V-1.05V)within10ms to ensure correct startup.2.4VDD(core)supply capabilityThe VDD(core)supply should be capable of supplying at least300mA for an L1and 600mA for an L2device assuming they may be operating at full capacity.2.5Power supply decouplingEnsure the design has multiple decoupling capacitors per supply placed close to the relevant supply pins.An example would be a minimum of4x0402or0603size surface mount capacitors of100nF in value,per supply.The ground side of the decoupling capacitors should have as short a path back to the ground pins of the device(mainly the centre pad)as possible.A bulk decoupling capacitor of at least 10uF should be placed on each supply.2.6PLL_AVDDA low passfilter is highly recommended on this pin to avoid noise affecting the internal PLL.An RCfilter is used on the XMOS reference designs with a1uF or100nF ceramic capacitor and a4.7R(L1)or2.2R(L2)resistor.Thefilter(and especially the capacitor)should be placed close to the PLL_AVDD pin.2.7Power on resetThe RST_N and TRST_N pins must be asserted(low)during or after power up.The device should not be used until these resets have taken place.As the errata in the datasheets show,the internal pullups on these two pins can occasionally provide stronger than normal pullup currents.For this reason,an RC type reset circuit is discouraged as behaviour would be unpredictable.A voltage supervisor type reset device is recommended to guarantee a good reset.This also has the benefit of resetting the system should the relevant supply go out of specification.2.8Clock inputThe CLK input pin should be supplied with a clock with monotonic rising edges and low jitter levels.Note that the PCU_CLK pin(only on some packages)must also be supplied with a clock for the device to function correctly,even if the PCU is not being used.The main CLK input can be tied to the PCU_CLK input to satisfy this condition.2.9SPI bootIf booting the device from a SPI Flash,ensure the MODE pins are set correctly(MODE3 =1,MODE2=1)and that the SPI Flash is connected to the correct ports as shown below:Pin Name SPI Signal DescriptionX0D0MISO Data-Master In Slave OutX0D1SS Slave SelectX0D10SCLK ClockX0D11MOSI Data-Master Out Slave InIf code debug via JTAG is required(e.g.code development)then make sure the MODE pins are set to boot from JTAG(i.e.don’t boot anything,wait to have code loaded over JTAG).This condition requires MODE3=0,MODE2=0and can be set with a jumper or similar.2.10USB ULPI ModeThe XS1-L1contains support for connecting to a USB transceiver using the UTMI+ Low Pin Interface(ULPI).When using the XS1-L1with ULPI,the ULPI signals must only be connected to specific ports as shown in the following table.When using ULPI,some ports on the same core are used internally and so are not available for use by user software.These are shown greyed out in the table.The available ports are shown in green.All ports on other cores are unaffected.Note that this limitation only applies when the ULPI is enabled,the greyed out ports can still be used before or after the ULPI is being used.2.11USB ULPI Port Table3Device ConfigurationExample XS1-L designs including schematics and layouts can be found on the XMOS website at:/support/silicon4Related DocumentsInformation about XMOS technology is primarily available from the XMOS website; please see /documentation for the latest documents or click on one of the links below tofind out more information.Document Document referenceXS1-L148TQFP Datasheet xs1-l1-48tqfp-datasheetXS1-L164LQFP Datasheet xs1-l1-64lqfp-datasheetXS1-L1128TQFP Datasheet xs1-l1-128tqfp-datasheetXS1-L2124QFN Datasheet xs1-l2-124qfn-datasheetXS1-L System Specification xsystemlXS1-L Clock Frequency Control Application Note xs1l_clkXS1Port I/O Timing Application Note xs1_port_timingXS1-L Link Performance and Design Guidelines xs1l_linksEstimating Power Consumption For XS1-L Devices xs1l_powerDevice Package User Guide package_user_guide5Document HistoryDate Release Comment2010-04-20 1.0First release2010-04-22 1.1Added ULPI interface information2011-04-26 1.2Added XS1-L1-48TQFP&Device Package User Guide Links 2011-06-06 1.3Added ground pad requirementsCopyright©2011XMOS Limited,All Rights Reserved.XMOS Limited is the owner or licensee of this design,code,or Information(collectively,the“Information”) and is providing it to you“AS IS”with no warranty of any kind,express or implied and shall have no liability in relation to its use.XMOS Limited makes no representation that the Information,or any particular implementation thereof,is or will be free from any claims of infringement and again,shall have no liability in relation to any such claims.XMOS and the XMOS logo are registered trademarks of XMOS Limited in the United Kingdom and other countries,and may not be used without written permission.All other trademarks are property of their respective owners.Where those designations appear in this book,and XMOS was aware of a trademark claim,the designations have been printed with initial capital letters or in all capitals.。

附录B (规范性附录)器件间距要求

表B.1

4 BGA外形与其他元器件的间隙≥

5 mm(200 mil)。

5 PLCC表面贴转接插座与其他元器件的间隙≥3 mm(120 mil)。

6 表面贴片连接器与连接器之间应该确保能够检查和返修。

一般连接器引线侧应该留有比连接器高度

大的空间。

7 元件到喷锡铜带(屏蔽罩焊接用)应该2mm(80mil)以上。

8 元件到拼板分离边需大于1mm(40mil)以上。

9 如果B面(焊接面)上贴片元件很多、很密、很小,而插件焊点又不多,建议插件引脚离开贴片元

件焊盘5mm以上,以便可以采用掩模夹具进行局部波峰焊。

注:其中间隙一般指不同元器件焊盘间的间隙,器件体大于焊盘时,指器件体的间隙)

附录C

(规范性附录)

内外层线路及铜箔到板边、非金属化孔壁的尺寸要求

表C.1单位:mm(mil) 板外形要素内层线路及铜箔外层线路及铜箔

距边最小尺寸

一般边≥0.5(20) ≥0.5(20)

导槽边≥1(40) 导轨深+2 拼板分离

边

V槽中心≥1(40) ≥1(40)

邮票孔孔边≥0.5(20) ≥0.5(20)

距非金属化孔壁最小尺寸一般孔0.5(20)(隔离圈)0.3(12)(封孔圈)单板起拔扳手轴孔2(80) 扳手活动区不能布线

附录D

(规范性附录)

PCB布线最小间距

表D.1

要素推荐使用的最小间距甚高密板最小间距(局部、谨慎使

用)

line to pin 0.2mm(8 mil) 0.127mm(5 mil)

附录E

(资料性附录)

丝印字符大小 (参考值)

表E.1。