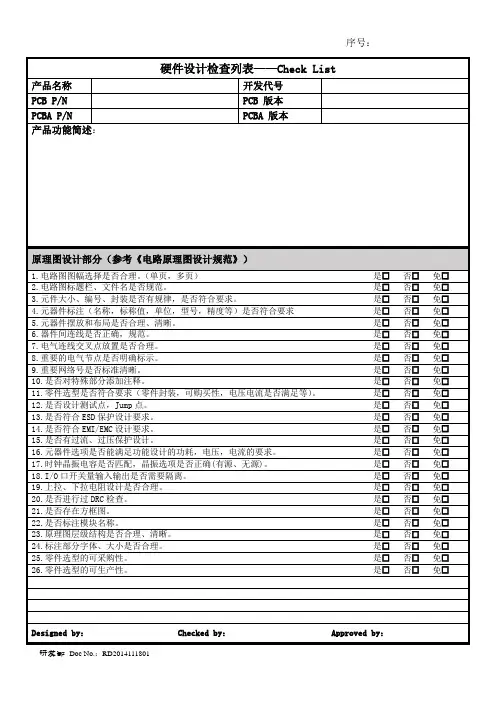

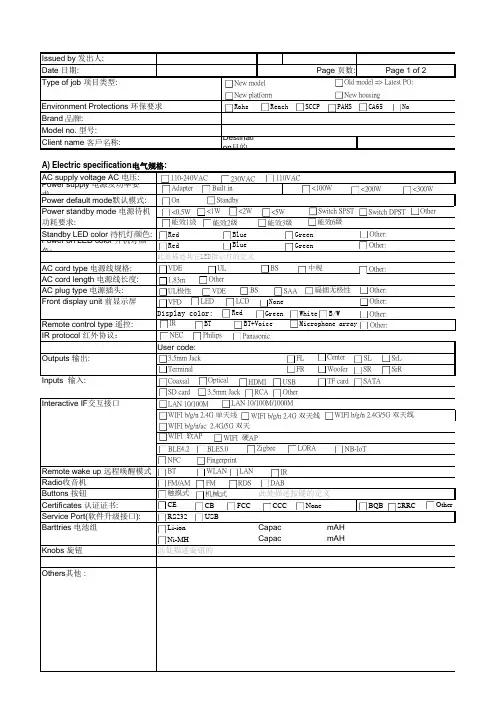

硬件设计checklist

- 格式:xls

- 大小:205.50 KB

- 文档页数:21

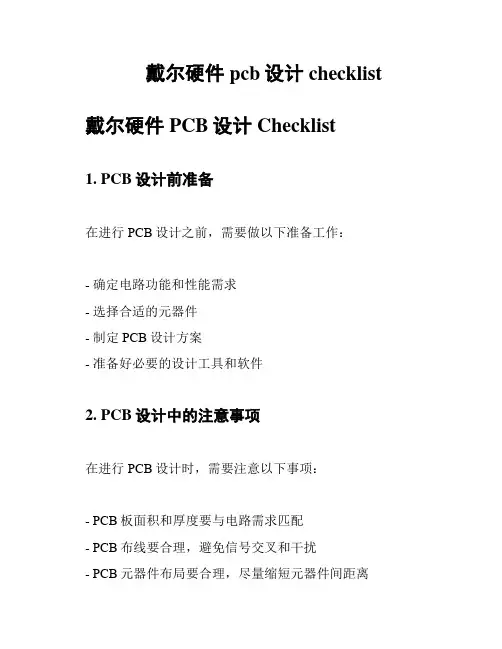

戴尔硬件pcb设计checklist 戴尔硬件PCB设计Checklist

1. PCB设计前准备

在进行PCB设计之前,需要做以下准备工作:

- 确定电路功能和性能需求

- 选择合适的元器件

- 制定PCB设计方案

- 准备好必要的设计工具和软件

2. PCB设计中的注意事项

在进行PCB设计时,需要注意以下事项:

- PCB板面积和厚度要与电路需求匹配

- PCB布线要合理,避免信号交叉和干扰

- PCB元器件布局要合理,尽量缩短元器件间距离

- PCB的供电系统要稳定,避免电压波动

- 为PCB添加必要的测试点和排查故障点

3. PCB设计后的检查

在完成PCB设计后,需要进行以下检查:

- 检查PCB的电路连接是否正确

- 检查PCB的电气性能是否满足要求

- 检查PCB的机械尺寸和板面尺寸是否符合要求

- 检查PCB的焊盘、锡膏、防护层等是否符合生产标准4. PCB设计后的优化

在完成PCB设计后,可以进行以下优化:

- 优化PCB的电路布线和元器件排布

- 优化PCB的供电系统和防护层

- 优化PCB的机械结构和布局

- 优化PCB的测试点和排查故障点

5. PCB设计的注意事项

在进行PCB设计时,需要注意以下事项:

- 所有元器件的电气性能参数应符合要求

- PCB的机械结构和尺寸应与产品需求匹配

- PCB的测试点和排查故障点要定位准确

- PCB的焊盘、锡膏、防护层等需要满足生产标准

6. 结论

通过以上的检查和优化,可以减少PCB设计中出现的故障和问题,并最终得到满足需求的电路板。

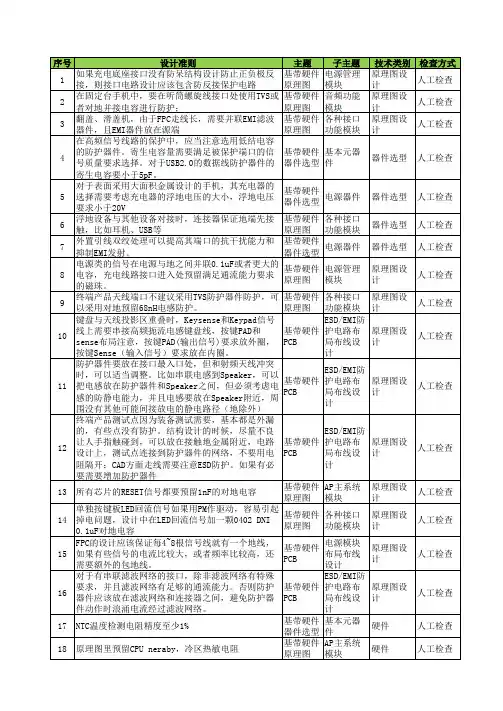

2: TTL信号和LVDS信号线之间是否相距一定距离(至少应该大于3~5倍差分线间距),减小直接串扰。

□是 □否 □无4:对于使用TTL和LVDS的系统,其电源之间是否用合适电感进行处理,以减小

TTL噪声进入LVDS系统。

□是 □否 □无5:对不用输入管脚是否按规范进行了处理。

□是 □否 □无6:对不用输出管脚,是否按规范进行了处理。

□是 □否 □无7:对高速LVDS器件使用,是否考虑了信号阻抗的匹配。

□是 □否 □无8:终端匹配元件是否要放在最靠近传输线末端的地方。

□是 □否 □无9:LVDS器件的电源管脚是否充分去藕,滤波电容的位置是否靠近电源和地管脚。

□是 □否 □无10:LVDS高速信号线上是否尽量避免了过孔。

□是 □否 □无11:LVDS高速信号线上是否避免了90度转折。

□是 □否 □无12:LVDS差分信号线是否做到电气等长和平衡。

□是 □否 □无13:LVDS信号是否有完整的参考地平面,保证有合理的回流路径。

□是 □否 □无14:电缆连接的情况下,电缆两端是否合理接地。

□是 □否 □无15:接插件中的LVDS信号的排布是否满足符合规范的原则。

□是 □否 □无

9。

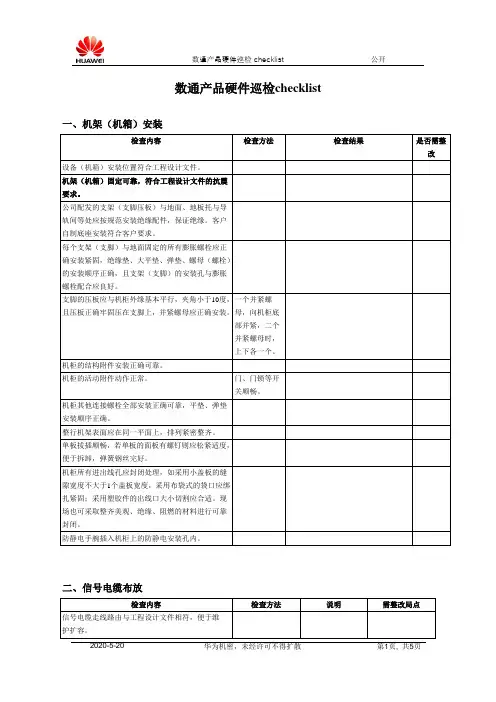

整机堆叠设计时应遵循热量分散的原则,手机整体框架结构是热性能的关键。

分析整机中主要发热的器件热阻及功耗,确认散热路径。

通常以下器件是主要的发热源:LCD的驱动芯片,喇叭,电池头部,高像素Camera,主板上的AP,PMIC,RF PA,WIFIPA,Tranceiver(MT6169在多个项目上实测温度都高于PA) 充电器件,背光驱动等大功率器件。

结构壳体厚度尽量减薄,以降低热阻,最好使用热阻较小的材料。

手机结构设计应保持内部具有良好的空气流通。

超薄机设计时,整机壳体应尽量采用大面积的金属结构件作为散热主体,例如采用A壳铝镁合金,金属后盖等。

主板采用半板,P型板等非整板设计时,A壳优选铝镁合金,其次为锌铝合金,最次为不锈钢片。

半版、P型板等非整板设计时,A壳不建议选用不锈钢片,散热的性能较差,节省的成本会转嫁到导热材料上。

(建议项,需踪合评估成本)整机堆叠设计硬件&结构热设计design guide项目检查项内容描述示意图导热材料设计项目检查项内容描述示意图检查结果导热材料选择导热率较高的材料,从性能上首选人工石墨,其次天热石墨,最后为铜箔;建议实际选用石墨的导热系数应≥1500W/m·K注:1.铜箔的散热参数约为400W/m·K,价格略低;2.天然石墨导热率为300~1500W/m·K,价格中等;3.人工石墨导热率为700~1900W/m·K,价格较高。

导热材料应能够覆盖温度高的部位,同时延伸到温度低的部分,将热量由温度高的位置传导到温度低的部分;必要时,可以增加导热材料的长度及宽度,大面积的延伸到整机温度低的部位。

使用导热材料时,导热材料应设计在B壳内侧,不可拆卸电池盖内侧,A壳金属面与PCB之间,芯片正上方,LCD铁框背面等位置。

整机温升较高时,应预留使用多层覆盖导热材料的方案,各层导热材料之间应保持一定的高度距离。

导热材料避免设计在电池盖,B壳外侧等位置,以免影响外观,长期使用磨损后导热效果下降。

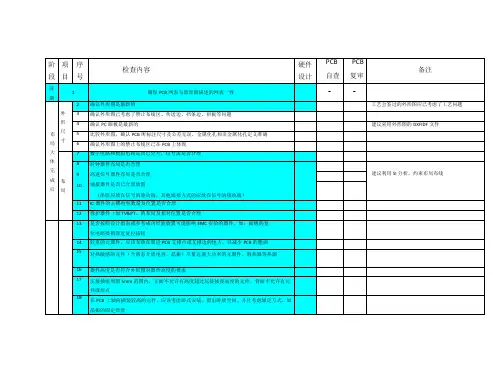

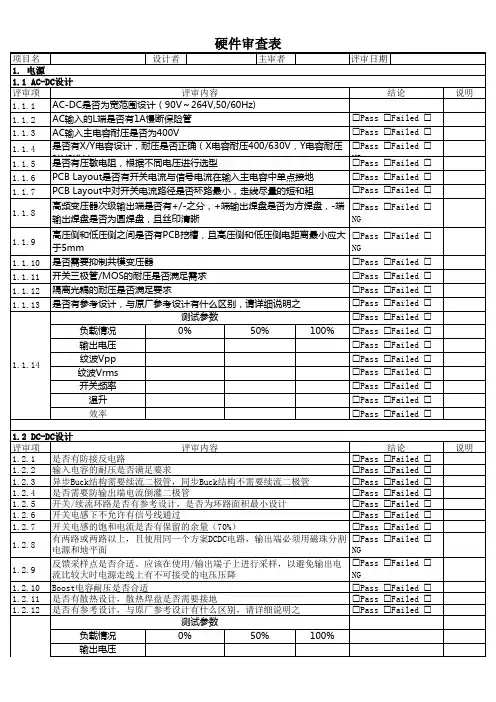

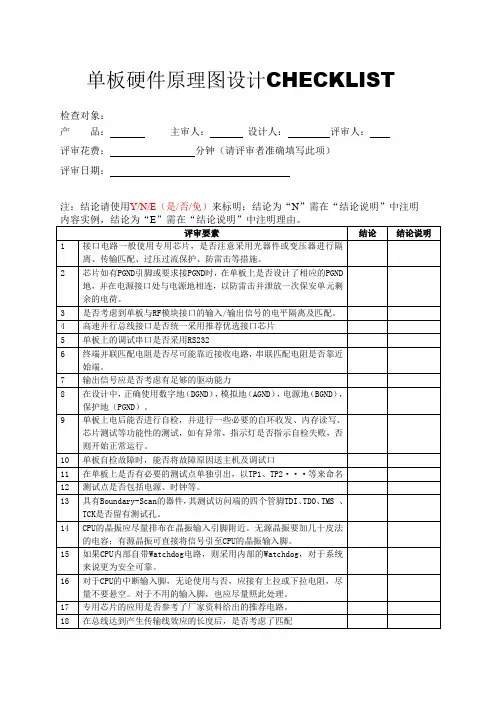

编号YES NO 不适用备注SA000SA001SA002SA003SA004SA005SA006SA007SB000SB001SB001SB002SC000对于不焊接、选择焊接或可调器件在其附近加文字备注并说明理由在相应位置添加兼容元器件的文字备注SB:器件选型原理图设计Checklist 灰色表示推荐参考的checklist 注明功率电阻,高耐压电容、变压器和保护器件(如压敏电阻,热敏电阻,ESD保护,放电管等)的关键指标和注意事项CHECKLIST要素集SA:文档格式与标注注明关键电路和元器件的重要参数。

如开关电源的频率、电感特性,隔离型DC-DC的隔离电压,晶体振荡器的负载电容,通用模块电路的功耗需求等原理图首页为版本信息说明。

包括版本号、版本修订记录、修订日期、修订人、详细修订内容和页数采用威胜信息通用原理图设计模版标注内容采用统一格式,字体为Courier New,粗体,字号不大于5号对于需要重点测试的关键网络添加测试点,文字备注不得选用已停产、即将停产、上市时间小于一年或供货周期大于八周的元器件物料和器件选型通过元件优选流程高压安规电容选型合理SC:封装不得选用唯一供应商供应的器件,必须有可替代性元器件型号,封装与生产厂家资料一致SC001SC002SD000SD001SD002SD003SD004SD005SD006SD007SD008SD009SD010SD011SD012SD013SD014SD015SD016SD017CPU的核心电源由LDO器件提供复位时,受控电源的电压不大于20%的额定电压值电源回路的电压范围设计合理电源回路各个电压的功率设计合理各类逻辑电平(如CMOS、TTL和LVTTL等)必须匹配CPU I/0、LED、继电器控制信号设计必须考虑芯片上电、复位时的状态电路设计有一定的扩展性器件原理图封装中,电源和地引脚不得隐藏如果硬件设计(或变更)涉及内核驱动设计(或相应变更)(如专用硬件资源分配、I/O功能定义、外部扩展地址分配等),硬件设计人员必须与内核组充分沟通、确认并达成共识。

附录B (规范性附录)器件间距要求

表B.1

4 BGA外形与其他元器件的间隙≥

5 mm(200 mil)。

5 PLCC表面贴转接插座与其他元器件的间隙≥3 mm(120 mil)。

6 表面贴片连接器与连接器之间应该确保能够检查和返修。

一般连接器引线侧应该留有比连接器高度

大的空间。

7 元件到喷锡铜带(屏蔽罩焊接用)应该2mm(80mil)以上。

8 元件到拼板分离边需大于1mm(40mil)以上。

9 如果B面(焊接面)上贴片元件很多、很密、很小,而插件焊点又不多,建议插件引脚离开贴片元

件焊盘5mm以上,以便可以采用掩模夹具进行局部波峰焊。

注:其中间隙一般指不同元器件焊盘间的间隙,器件体大于焊盘时,指器件体的间隙)

附录C

(规范性附录)

内外层线路及铜箔到板边、非金属化孔壁的尺寸要求

表C.1单位:mm(mil) 板外形要素内层线路及铜箔外层线路及铜箔

距边最小尺寸

一般边≥0.5(20) ≥0.5(20)

导槽边≥1(40) 导轨深+2 拼板分离

边

V槽中心≥1(40) ≥1(40)

邮票孔孔边≥0.5(20) ≥0.5(20)

距非金属化孔壁最小尺寸一般孔0.5(20)(隔离圈)0.3(12)(封孔圈)单板起拔扳手轴孔2(80) 扳手活动区不能布线

附录D

(规范性附录)

PCB布线最小间距

表D.1

要素推荐使用的最小间距甚高密板最小间距(局部、谨慎使

用)

line to pin 0.2mm(8 mil) 0.127mm(5 mil)

附录E

(资料性附录)

丝印字符大小 (参考值)

表E.1。

编号YES NO 不适用备注SA000SA001SA002SA003SA004SA005SA006SA007SB000SB001SB001SB002SC000对于不焊接、选择焊接或可调器件在其附近加文字备注并说明理由在相应位置添加兼容元器件的文字备注SB:器件选型原理图设计Checklist 灰色表示推荐参考的checklist 注明功率电阻,高耐压电容、变压器和保护器件(如压敏电阻,热敏电阻,ESD保护,放电管等)的关键指标和注意事项CHECKLIST要素集SA:文档格式与标注注明关键电路和元器件的重要参数。

如开关电源的频率、电感特性,隔离型DC-DC的隔离电压,晶体振荡器的负载电容,通用模块电路的功耗需求等原理图首页为版本信息说明。

包括版本号、版本修订记录、修订日期、修订人、详细修订内容和页数采用威胜信息通用原理图设计模版标注内容采用统一格式,字体为Courier New,粗体,字号不大于5号对于需要重点测试的关键网络添加测试点,文字备注不得选用已停产、即将停产、上市时间小于一年或供货周期大于八周的元器件物料和器件选型通过元件优选流程高压安规电容选型合理SC:封装不得选用唯一供应商供应的器件,必须有可替代性元器件型号,封装与生产厂家资料一致

SC001SC002SD000SD001SD002SD003SD004SD005SD006SD007SD008SD009SD010SD011SD012SD013SD014SD015SD016SD017CPU的核心电源由LDO器件提供复位时,受控电源的电压不大于20%的额定电压值电源回路的电压范围设计合理电源回路各个电压的功率设计合理各类逻辑电平(如CMOS、TTL和LVTTL等)必须匹配CPU I/0、LED、继电器控制信号设计必须考虑芯片上电、复位时的状态电路设计有一定的扩展性器件原理图封装中,电源和地引脚不得隐藏如果硬件设计(或变更)涉及内核驱动设计(或相应变更)(如专用硬件资源分配、I/O功能定义、外部扩展地址分配等),硬件设计人员必须与内核组充分沟通、确认并达成共识。

改进版本对底层软件接口具有良好的兼容性。

如特定的地址空间分配,寄存器地址和内容设定,新版本的修订应尽量不导致底层软件的修改。

SD:电路设计CPU与电平转换芯片SN74LVCH16245A或SN74LVTH16245A之间不使用上拉或下拉电阻电源回路各个电压之间的耐压设计合理电源回路各个电压的纹波设计合理对于需要大电流驱动的器件必须考虑源端的驱动能力用做开关管的三极管除了电流满足要求外外,其额定功率也要满足要求数字电路输入输出电平必须匹配使用排线接入的电源在入口地方考虑添加共模抑制电感电源上电顺序应该尽量满足要求元器件显示信息中至少包含型号,PCB封装,位号三类信息数字芯片的扇入扇出能力,驱动继电器、发光二极管的能力满足要求

SD018

SD019 SD020 SD021 SD022 SD023 SD024 SD025 SD026 SD027 SD028 SD029 SD030

SD031 SD032 SD033 SD034 SD035 SD036 SD037 SD038

SD039与其他模块相连接的输入输出接口(如插座插头、Modem通信、接插件和I/O 口等)信号定义一致

CMOS芯片输入管脚不得悬空

遥信输入回路限流电阻使用贴片封装,功率不小于1/4W(1206封装)

遥信输入回路滤波电容使用贴片封装,耐压值不小于50V

有线介质通信电路(如485、232、以太网和Modem等)的保护措施满足要求保证控制电路逻辑正确。

如mos管控制逻辑,电池充放电逻辑,掉电检测逻辑,继电器控制输出逻辑等

光耦的耐压、速度和电流传输比选择合理

高速信号必须考虑阻抗匹配

功率元件必须考虑散热设计

充电电路的限流电阻要满足功率要求(推荐使用1206封装)

光耦的前向导通电流(Forward current )不小于5mA

在与外部接口相连的电路中(如485电路、232电路等),用于限流的电阻,使用1206封装,以保证功率满足要求

对终端辅助端子做非法操作时(如短路等),不引起终端复位或损坏

钽电容价格较贵,不推荐使用

端子排上的输出电路具备短路保护能力

遥控、无功投切和告警回路采用双逻辑互斥控制

数字电路速度要匹配

开关器件(如光耦、继电器和发光二极管等)默认为不导通状态

考虑感性器件关断时反向电压的吸收设计(如继电器线圈反向并联二极管等)

钽电容容易起火,使用时其直流工作电压不超过50%的额定值

控制输出回路为电平触发逻辑器件

继电器的触点容量、对数、常闭常开和自保持选择合理

F

I

SE000SE001SE002SE003

SE004

SE005

SE007

SE008

SE009

SE010

SE011SE012SE013SE014SE015

SE016

SE017

SE018

SE019复位、硬件看门狗、使能信号、锁存信号和触发信号等重要电路具备抗干扰能力电源板上三相四线输入情况下,N相应该有和A、B、C三相平衡的抗干扰处理措施终端外接端子排信号定义、排列顺序必须符合技术条件要求插针上有防止误操作造成电源短路的措施数字地网络名为GND,符号为 。

当有多个数字地时,应显示出地网络标号,如 。

无显示时默认为GND。

模拟地网络名为AGND,符号为使用candence画原理图时,信号连接到其他页面时必须使用分页连接符元器件位号命名符合《元器件位号和电气网络命名规范》SE:网络

电气网络命名符合《元器件位号和电气网络命名规范》保护地网络名为EARTH,符号为AC电源网络采用电源符号DC电源网络采用电源符号不同网络命名不能相同,同一网络命名必须相同(单点接地时,地网络除外) SF:布局与走线

脉冲输入输出端口(含遥控遥信)必须做隔离、抗干扰设计不能存在没有连接的网络电路设计在满足功能要求的前提下成本尽量低

每个芯片必须配置合理的去耦电容,并且注明去耦电容所属芯片或引脚,以方便PCB设计人员进行器件摆放

单板电源输入端必须配置合理的旁路电容

考虑按钮的防抖动设计

GND_WL

SF000 SF001 SF002 SF003 SF004

SF005

SF006

SF007 SF008 SF009走线、电源符号和地符号位于栅格上

有protel画图时捕获栅格设置为10

有cadence画图时,Grid spacing使用默认值“1 of pin to pin”

与整个电路相关的接口电路放在整个页面右侧,功能模块的接口电路放在虚框内右侧

元器件摆放位置位于栅格上

布局均匀美观

有protel画图时电气栅格设置为8

元器件布局考虑信号流向,同一页各功能模块分区清晰,功能模块之间用虚框分开

有protel画图时可见栅格设置为10

地址线和数据线均采用总线形式。