45nm工艺库的版图规则

- 格式:ppt

- 大小:2.29 MB

- 文档页数:28

解析45NM纳米CPU制作工艺CPU的发展史也可以看作是制作工艺的发展史。

如果想要提高CPU的性能,那么更高的频率、更先进的核心以及更优秀的缓存架构都是不可或缺的,而此时自然也需要以制作工艺作为保障。

几乎每一次制作工艺的改进都能为CPU发展带来最强大的源动力,无论是Intel还是AMD,制作工艺都是发展蓝图中的重中之重,如今处理器的制造工艺已经走到了45纳米的新舞台,它将为新一轮CPU高速增长开辟一条康庄大道。

很多用户都对不同的CPU的制作工艺非常熟悉,然而如果问他们什么是制作工艺,65纳米、45纳米代表的是什么,有什么不同,这些问题他们未必能够准确地解答,下面我们就一起来详细了解一下吧。

一、铜导互连的末代疯狂:45纳米制作工艺几乎每一次制作工艺的改进都会给CPU发展带来巨大的源动力。

以如今炙手可热的Pentium4为例,从最初的0.18微米到随后的65纳米,短短四年中我们看到了惊人的巨变。

如今,45纳米制作工艺再一次突破了极限,这也被视为是铜导互连技术的最终畅想曲。

1.制作工艺的重要性早期的微处理器都是使用0.5微米工艺制造出来的,随着CPU频率的增加,原有的工艺已无法满足产品的要求,这样便出现了0.35微米以及0.25微米工艺,不久以后,0.18微米、0.13微米以及90纳米制造的处理器产品也相继面世。

另外一方面,早期芯片内部都是使用铝作为导体,但是由于芯片速度的提高,芯片面积的缩小,铝线已经接近其物理性能极限,所以芯片制造厂商必须找出更好的能够代替铝导线的新的技术,这便是我们常说的铜导技术。

铜导线与铝导线相比,有很大的优势,具体表现在其导电性要优于铝,而且电阻小,所以发热量也要小于现在所使用的铝,从而可以有效地提高芯片的稳定性。

我们今天所要介绍的65纳米技术也是向着这一方向发展。

Intel在IDF 2007上骄傲地展示45nm工艺光刻蚀是目前CPU制造过程当中工艺非常复杂的一个步骤,其过程就是使用一定波长的光在感光层中刻出相应的刻痕,由此改变该处材料的化学特性。

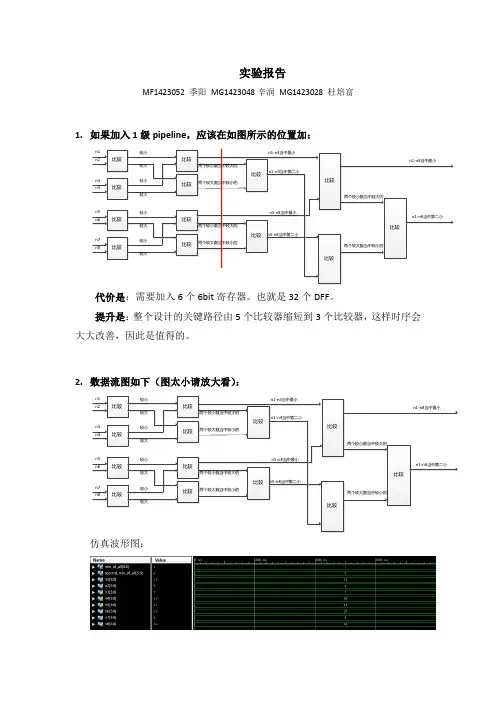

实验报告MF1423052 季阳MG1423048辛润MG1423028 杜培富1.如果加入1级pipeline,应该在如图所示的位置加:代价是:需要加入6个6bit寄存器。

也就是32个DFF。

提升是:整个设计的关键路径由5个比较器缩短到3个比较器,这样时序会大大改善,因此是值得的。

2.数据流图如下(图太小请放大看):仿真波形图:可知,输入是14,9,7,55,41,22,8,32,输出是7和8。

可知功能正确。

综合过后,资源使用率如下:可以看到,用了13个6bit比较器和20个6bit选择器。

综合过后,得到该纯组合逻辑的输入输出延迟为:可以看出,输入输出时延为11.741ns。

3.如果加入2级pipeline,应该在如图所示的位置加:代价是:需要加入10个6bit寄存器,也就是60个DFF。

提升是:整个设计的关键路径由3个比较器缩短到2个比较器,花的比较器多了28个,时序提升相比一级pipeline的设计较少,因此综合考虑起来是不值得的。

4.面积最小的设计:面积最小的设计假设8个数据是串行输入,前两个数比较一下大小,将小的写入Min寄存器,大的写入Max寄存器。

第三个数分别与这两个寄存器里面的数比较,留下较小的两个值。

数据依次进入,最终留在寄存器中的就是8个当中最小的2个数。

仿真波形图:可以看到,输入的输入依次是:33,17,9,5,3,5,9,17,输出是3和5,可知功能正确。

综合过后,资源使用率如下:可以看到,用了1个5bit计数器,24个寄存器,2个6bit比较器,3个6bit 选择器。

跟之前最快的设计相比,虽然这个设计用的比较器少了11个,选择器少了17个,但是多了1个5bit计数器和24个寄存器。

所以到底面积是大了还是小了还需要进一步验证。

因此,将这两个设计在Design Compiler下进行综合,综合工艺库为TSMC 45nm标准单元库。

下面比较其面积。

速度最快的设计面积占用:面积最小的设计面积占用:由结果可知:最快的设计占用面积是399.84,面积最小的设计占用268.128。

45nm铜工艺 面临的挑战作者:Peter Singer, Semiconductor International主编 摘要:本文综述了铜工艺即将面临的各种变化,包括扩散阻障层(barrier)、电镀添加剂、覆盖层以及与多孔超低k电介质之间的整合等。

随着半导体向45nm工艺的深入发展,铜工艺技术不可避免地要发生一些变化。

TaN扩散阻障层物理气相沉积(PVD)技术可能将被原子层沉积(atomic layer deposition,ALD)技术所取代,之后可能还会引进钌阻障层技术。

钌阻障层技术不再需要电镀种子层,但是其发展状况将取决于研究结果的进展程度。

电镀槽中的有机“添加剂”也可能会有所变化,因为有些添加剂最终会被包埋在铜中。

尽管有机添加剂的使用可以使沉积得到的铜填充没有任何缝隙,同时在密集区不会产生沉积过度的情况,因此不会给CMP带来额外负担,从而减小了CMP难度,但是包埋在铜里的杂质会提高电阻系数,并且使铜在退火时不太容易形成大金属颗粒。

铜工艺也有电致迁移这个严重的可靠性问题,它通常发生在铜导线顶部与电介质相接的交界处。

可能的解决办法是在铜表面选择性地沉积上一层钴钨磷化物(cobalt tungsten phosphide,CoWP)或钴钨硼化物(cobalt tungsten boride,CoWB),最终取代Si(C)N覆盖层,使铜原子迁移受到限制。

金属颗粒边界、缺陷和表面造成的电子散射问题也会逐渐突显出来,因为导线尺寸很小时电子散射效应会使电阻升高。

解决办法包括增大金属颗粒、减少缺陷数量和增加金属表面光滑度等。

当然,我们还需要将铜和多孔超低k介电材料整合在一起,该需求会进一步增加铜工艺的复杂度。

其中一个问题是这些多孔材料需要一些孔洞密封工艺,人们对其与沉积在上面的扩散阻障碍层之间的相互作用感到担心,不知道两者之间是否能够相互兼容。

铜工艺基础自1990年代中期IBM、Intel、AMD和其他IC制造商决定用铜制工艺取代铝工艺以来,铜工艺的主要优点基本保持不变。

第一页:制程是架构交叉体系下的性能提升稻草多年来Intel一直在奉行制程更新与处理器架构体系改变的交叉更替,以确保在制程没有改变的情况下可以借由处理器体系架构的更新来提升产品性能,又或是处理器架构没有改变的情况下借由制程的更新来提升产品性能。

就这样,我们从westwood核心到130nm再从90nm到netbeast,然后是65nm到Conroe、kentsfield,那今年Intel毫无疑问的将会在Conroe、Kentsfield上过渡到45nm工艺上,不过这次Intel的工艺转换还加入了一些新的元素。

所谓的制程工艺,就是指晶体管之间的线宽,如65nm制程就是指晶体管之间的线宽是65nm,但这次Intel 45nm制程的更新不仅是把晶体管间的线宽缩短到45nm,在构成处理器的细胞元件——晶体管上也有着非常重大的突破。

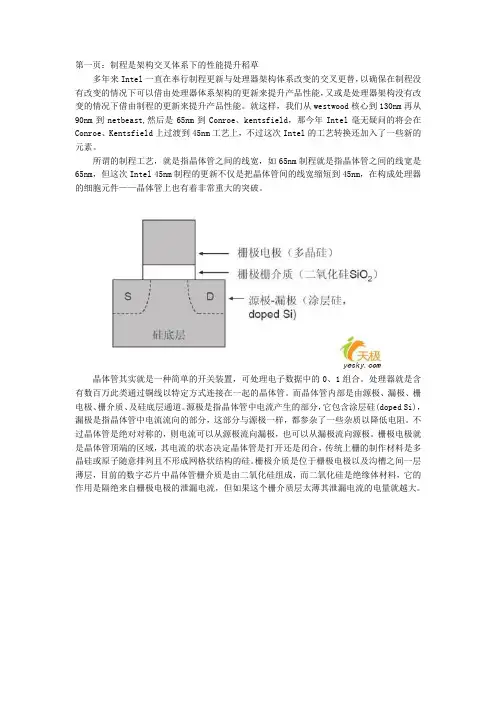

晶体管其实就是一种简单的开关装置,可处理电子数据中的0、1组合。

处理器就是含有数百万此类通过铜线以特定方式连接在一起的晶体管。

而晶体管内部是由源极、漏极、栅电极、栅介质、及硅底层通道。

源极是指晶体管中电流产生的部分,它包含涂层硅(doped Si),漏极是指晶体管中电流流向的部分,这部分与源极一样,都参杂了一些杂质以降低电阻。

不过晶体管是绝对对称的,则电流可以从源极流向漏极,也可以从漏极流向源极。

栅极电极就是晶体管顶端的区域,其电流的状态决定晶体管是打开还是闭合,传统上栅的制作材料是多晶硅或原子随意排列且不形成网格状结构的硅。

栅极介质是位于栅极电极以及沟槽之间一层薄层,目前的数字芯片中晶体管栅介质是由二氧化硅组成,而二氧化硅是绝缘体材料,它的作用是隔绝来自栅极电极的泄漏电流,但如果这个栅介质层太薄其泄漏电流的电量就越大。

Intel对晶体管的改进是来自之前晶体管的栅极介质,Intel是使用一种基于铪元素的化合物来替代之前的二氧化硅,这种基于铪元素的High-K介质具备良好的绝缘属性,同时可以在栅极及硅底层之间形成较高的场效应(High-K)。

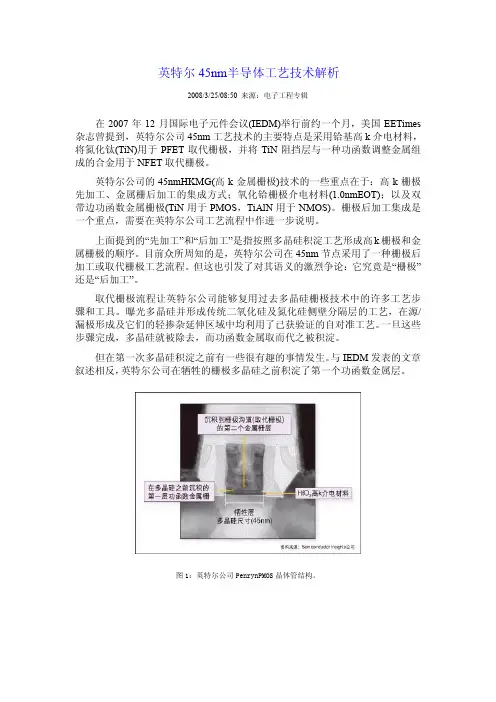

英特尔45nm半导体工艺技术解析2008/3/25/08:50 来源:电子工程专辑在2007年12月国际电子元件会议(IEDM)举行前约一个月,美国EETimes 杂志曾提到,英特尔公司45nm工艺技术的主要特点是采用铪基高k介电材料,将氮化钛(TiN)用于PFET取代栅极,并将TiN阻挡层与一种功函数调整金属组成的合金用于NFET取代栅极。

英特尔公司的45nmHKMG(高k金属栅极)技术的一些重点在于:高k栅极先加工、金属栅后加工的集成方式;氧化铪栅极介电材料(1.0nmEOT);以及双带边功函数金属栅极(TiN用于PMOS,TiAlN用于NMOS)。

栅极后加工集成是一个重点,需要在英特尔公司工艺流程中作进一步说明。

上面提到的“先加工”和“后加工”是指按照多晶硅积淀工艺形成高k栅极和金属栅极的顺序。

目前众所周知的是,英特尔公司在45nm节点采用了一种栅极后加工或取代栅极工艺流程。

但这也引发了对其语义的激烈争论:它究竟是“栅极”还是“后加工”。

取代栅极流程让英特尔公司能够复用过去多晶硅栅极技术中的许多工艺步骤和工具。

曝光多晶硅并形成传统二氧化硅及氮化硅侧壁分隔层的工艺,在源/漏极形成及它们的轻掺杂延伸区域中均利用了已获验证的自对准工艺。

一旦这些步骤完成,多晶硅就被除去,而功函数金属取而代之被积淀。

但在第一次多晶硅积淀之前有一些很有趣的事情发生。

与IEDM发表的文章叙述相反,英特尔公司在牺牲的栅极多晶硅之前积淀了第一个功函数金属层。

图1:英特尔公司PenrynPMOS晶体管结构。

图2:晶体管的物理栅极长度(LG)测量。

图3:0.346平方微米的SRAM单元。

对于P沟道晶体管,TiN紧跟着HfO2介电材料之后被积淀。

添加铝形成TiAlN后可以将功函数调整为适合于N沟道晶体管。

英特尔的工艺通过在多晶硅形成和图样化之前积淀首个功函数层可以保护HfO2免受多晶硅蚀刻。

SI工程师把首个金属栅极层称为顶部接口层(TIL),因为它为HfO2电介质提供了无可否认的保护。

Intel 65nm工艺实现与45nm工艺预览作者濮元恺 2006年8月一, 工艺的提升带来了什么那些说摩尔定律“脑死亡”的人应该清醒的了,虽然我自己也曾对摩尔定律的未来抱有很大的怀疑和迷茫,但Intel正用实际行动一次次证明自己。

high-k方面的突破,应变硅技术上升级,晶体管结构上的创新……一个个激动人心的技术,印证了Intel在半导体制造技术的足迹。

下面将结合最近收集到的材料,和大家一起了解Intel的65nm与未来的45nm工艺。

文中出现的技术词汇不单独注解,而是在原文里整体说明,希望本文能给硬件技术爱好者在晋级道路上提供一些帮助。

1, Intel的全盘计划这张图片就是Intel的CPU整体计划,它是一项粗略的计划。

P1262是我们熟悉的采用90nm制造的Pentium 4处理器,第一批产品在2003年末出厂,典型代表是Pentium 4 Prescott。

P1262延续了上一代Pentium 4的NetBrust(网络爆发)架构,在频率方面疯狂飙升,而且90nm工艺内有一些问题没有很好地解决。

P1262计划预期达到的频率是4.0GHz,实际最后一款产品止步于3.8 GHz。

P1264是我们正在经历的时代,周期同样是2年。

我们熟悉的产品是Core微架构的Conroe处理器,采用65nm工艺制造,功耗控制表现优秀,性能强大。

P1266是未来45nm工艺制造的处理器,它将从2007年持续到2009年,产品的名称和型号我们还不知。

然后由32nm工艺的P1268接替它继续实现摩尔定律。

P1264和P1266正是我们下面要说明的计划,因为它们使用了65nm与45nm工艺,这两款工艺的实现对Intel非常重要,Intel借助它们证实了自己在芯片制造界的领先地位,同时成功地延续着摩尔定律,也同时突破了很多技术壁垒。

2. 新工艺带来了什么a、更高的性能我们在这里说的65nm、45nm是指每一个晶体管的大小,晶体管越小,单个芯片能容纳的晶体管也越多,性能由此得到提升。

45nm远不是极限!神秘的处理器制程工艺王璐烽《微型计算机》2009年3月下2009-04-16“1965年,我为《电子学》撰写文章。

那时我预见到,我们将制造出更复杂的电路从而降低电器的成本—根据我的推算,10年之后,一块集成电路板里包含的电子元件会从当时的60个增加到6万多个,那是个大胆的推断。

1975年,我又对它做了修正,把每一年翻一番的目标改为每两年翻一番。

” —戈登·摩尔(Gordon Moore)摩尔定律指导集成电路(IC,Integrated Circuit)工业飞速发展到今天已经40多年了。

在进入21世纪的第8个年头,各类45nm芯片开始批量问世,标志着集成电路工业终于迈入了低于50nm的纳米级阶段。

而为了使45nm工艺按时“顺产”,保证摩尔定律继续发挥作用,半导体工程师们做了无数艰辛的研究和改进—这也催生了很多全新的工艺特点,像大家耳熟能详的High-K、沉浸式光刻等等。

按照业界的看法,45nm工艺的特点及其工艺完全不同于以往的90nm、65nm,反而很多应用在45nm制程工艺上的新技术,在今后可能贯穿到32nm 甚至22nm阶段。

今天就让我们通过一个个案例,来探索一下将伴随我们未来5年的技术吧。

你能准确说出45nm是什么宽度吗?得益于厂商与媒体的积极宣传,就算非科班出身,不是电脑爱好者的大叔们也能知道45nm比65nm更加先进。

但如果要细问45nm是什么的长度,估计很多人都难以给出一个准确的答案。

而要理解这个问题,就要从超大规模集成电路中最基本的单元—MOS(Metal Oxide Semiconductor金属氧化物半导体)晶体管说起。

我们用半导体制作MOS管就是利用其特殊的导电能力来传递0或者1的数字信号。

在栅极不通电的情况下,源区的信号很难穿过不导电的衬底到达漏区,即表示电路关闭(数字信号0);如果在栅极和衬底间加上电压,那么衬底中的电荷就会在异性相吸的作用下在绝缘氧化层下大量聚集,形成一条细窄的导电区,使得源区和漏区导通,那么电流就可以顺利从源区传递到漏区了(信号1)。

工艺库说明工艺库是采用0.18um的工艺,下面是调用工艺库名称及尺寸范围,工艺库的调用模型的名称可以自己进工艺库里面改,比如说我这里用的是nmos18表示nmos管,供给电压为1.8V。

工艺里面的数值可以自己修订,但是如果要流片的话必须要和工厂的工艺库一样。

具体尺寸说明如下,调用名称调用类型基本的宽长范围nmos18TT L:240nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vpmos18TT L:240nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vnmos18SS L:240nm-50um,W:240nm-100um,tox=4.45nm,vdd=1.8Vpmos18SS L:240nm-50um,W:240nm-100um,tox=4.45nm,vdd=1.8Vnmos33TT L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3Vpmos33TT L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3Vnmos18FF L:240nm-50um,W:240nm-100um,tox=3.5nm,vdd=1.8Vpmos18FF L:240nm-50um,W:240nm-100um,tox=3.5nm,vdd=1.8Vnmos18SNFP L:240nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vpmos18SNFP L:240nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vnmos18FNSP L:240nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vpmos18FNSP L:240nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vnmos33MM L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V pmos33MM L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V nmos33NN L:500nm-50um,W:800nm-100um,tox=7.5nm,vdd=3.3V pmos33NN L:500nm-50um,W:800nm-100um,tox=7.5nm,vdd=3.3V nmos33OO L:500nm-50um,W:800nm-100um,tox=6.5nm,vdd=3.3V pmos33OO L:500nm-50um,W:800nm-100um,tox=6.5nm,vdd=3.3V nmos33PP L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V pmos33PP L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V nmos33QQ L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V pmos33QQ L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V nmos018RR L:300nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V nmos033RR L:500nm-50um,W:800nm-100um,tox=7nm,vdd=3.3V nmos033UU L:500nm-50um,W:800nm-100um,tox=7.5nm,vdd=3.3V nmos033VV L:500nm-50um,W:800nm-100um,tox=6.5nm,vdd=3.3V nmos033WW L:500nm-50um,W:800nm-100um,tox=7.25nm,vdd=3.3V nmos033XX L:500nm-50um,W:800nm-100um,tox=6.75nm,vdd=3.3V nch YY L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V pch YY L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V nch ZZ L:180nm-50um,W:240nm-100um,tox=3.95nm,vdd=1.8V pch ZZ L:180nm-50um,W:240nm-100um,tox=3.95nm,vdd=1.8V nch AA L:180nm-50um,W:240nm-100um,tox=4.45nm,vdd=1.8V pch AA L:180nm-50um,W:240nm-100um,tox=4.45nm,vdd=1.8V nch BB L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V pch BB L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V nch CC L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V pch CC L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V nch EE L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V pch EE L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8V nch GG L:180nm-50um,W:240nm-100um,tox=3.95nm,vdd=1.8V pch GG L:180nm-50um,W:240nm-100um,tox=3.95nm,vdd=1.8V nch HH L:180nm-50um,W:240nm-100um,tox=4.45nm,vdd=1.8Vpch HH L:180nm-50um,W:240nm-100um,tox=4.45nm,vdd=1.8Vnch II L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vpch II L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vnch JJ L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vpch JJ L:180nm-50um,W:240nm-100um,tox=4.2nm,vdd=1.8Vbjtp KK饱和电流is=5.6*10-18,放大倍数bf=1.38,pnp,5*5um2bjtp1KK饱和电流is=2.8*10-17,放大倍数bf=1.36,pnp,10*10um2np KK面积=8e-9,饱和电流=2.82e-7np1KK面积=8e-9,饱和电流=1.17e-7np2KK面积=9.72e-8,饱和电流=4.204e-6np1FM面积=8e-9,饱和电流=2.82e-7pn1FM面积=8e-9,饱和电流=1.17e-7Psub/np FM面积=9.72e-8,饱和电流=4.204e-6注:还有很多其他的类型如FF,SNFP你都可以通过打开工艺库自己根据需要选择。