电路版图设计与规则

- 格式:doc

- 大小:2.36 MB

- 文档页数:16

电路版图设计一般流程1. 确定需求和规格在开始设计电路板之前,首先需要明确产品的具体需求和规格。

这包括产品的功能要求、性能要求、工作环境等。

只有清楚明确了需求和规格,才能够确定电路板设计的方向和目标。

2. 选择器件根据产品的需求和规格,选择适合的器件和元器件。

这包括集成电路、传感器、连接器等各种器件。

在选择器件时,需要考虑器件的性能、价格、供货周期等因素,确保选择的器件能够满足产品的需求。

3. 电路原理图设计根据选定的器件,绘制电路原理图。

电路原理图是电路板设计的基础,它反映了整个电路的连接关系和工作原理。

在设计电路原理图时,需要考虑电路的稳定性、可靠性和性能,确保电路能够正常工作。

4. PCB布局设计根据电路原理图,设计PCB(Printed Circuit Board)的布局。

PCB布局设计是电路板设计的关键环节,它直接影响到电路板的性能和可靠性。

在进行PCB布局设计时,需要考虑到器件的布局、信号的传输路径、电源的分布等因素,确保布局的合理性和稳定性。

5. 电路仿真和调试完成PCB布局设计后,需要进行电路仿真和调试。

通过电路仿真软件模拟电路的工作过程,检验电路的稳定性和性能。

根据仿真结果进行调整和优化,直到满足产品的需求为止。

6. PCB制造和组装完成电路板设计后,需要将PCB制造出来,并进行元器件的组装。

选择信誉良好的PCB制造厂商和组装厂商,确保PCB的质量和可靠性。

在组装过程中,需要注意器件的焊接、布线和测试,确保电路板能够正常工作。

7. 电路测试和验证完成PCB制造和组装后,需要进行电路的测试和验证。

通过各种测试方法对电路板进行验证,确保电路的稳定性和性能。

如果测试通过,就可以将电路板用于产品中;如果测试不通过,需要进行调整和优化,直到满足产品的要求为止。

总的来说,电路板设计是一项复杂而严谨的工作,需要经过多个环节的精心设计和调试。

只有经过严密的设计流程,才能确保最终产品的质量和性能。

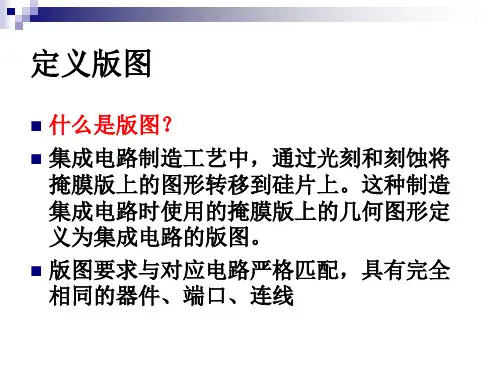

第三章集成电路版图设计每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:最小线宽 Minimum Width最小间距 Minimum Spacing最小延伸 Minimum Extension最小包围 Minimum Enclosure 最小覆盖 Minimum Overlay集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!3.2模拟集成电路版图设计中遵从的法则3.2.1电容的匹配对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容易达到高精度的匹配。

电路版图设计一般流程

电路版图设计的一般流程:

1.分析功能需求:首先,需要明确电路所要实现的功能,并对这些功能进行归类整合。

这涉及到确定输入变量、输出变量和中间变量。

2.框图设计:提出电路的功能要求,明确各功能块的功能及其相互间的连接关系,并进行框图设计。

3.设计单元电路:确定或设计各单元电路,确定其中的主要器件,并给出单元电路图。

4.整合单元电路:规范设计统一的供电电路即电源电路,并做好级联的设计,将各单元电路整合在一起。

5.设计电路全图:根据前面的设计,完成详尽的电路全图,确定全部元器件,并给出需用元器件清单。

6.绘制PCB图:根据元器件和电路设计,绘制印制电路板图,并给出相应的元器件分布图、接线图等。

如果是整机的设计,一般还需要提供整机结构图。

7.调试与测试:对于业余设计或单体实验开发类的电路,需要进行调试与测试,并给出实验与测试的结果。

8.编写设计说明书或报告:最后,需要编写设计说明书或设计报告,以便其他人理解和使用所设计的电路。

(第二讲)一. 集成电路设计基础1.4 版图设计规则 Design Rule李福乐 清华大学微电子所上一讲主要内容• 课程介绍 • 集成电路设计背景知识 • 硅栅CMOS集成电路版图流程 • CMOS工艺中集成元件的版图、结构和电特性版图设计规则Design Rule• 引言 • 设计规则(Topological Design Rule)– 上华0.6um DPDM CMOS工艺拓扑设计规则 – 设计规则的运用• 版图设计准则(‘Rule’ for performance)– 匹配 – 抗干扰 – 寄生的优化 – 可靠性引言• 芯片加工:从版图到裸片制加版工是一种多层平面“印刷”和 叠加过程,但中间是否会 带来误差?引言一个版图的例子:引言加工后得到的实际芯片版图例子:1引言• 加工过程中的非理想因素– 制版光刻的分辨率问题 – 多层版的套准问题 – 表面不平整问题 – 流水中的扩散和刻蚀问题 – 梯度效应引言• 解决办法– 厂家提供的设计规则(topological design rule),确保完成设计功能和一定的芯片成 品率,除个别情况外,设计者必须遵循– 设计者的设计准则(‘rule’ for performance),用以提高电路的某些性 能,如匹配,抗干扰,速度等设计规则(topological design rule)基本定义(Definition) WidthEnclosure设计规则ExtensionExtensionSpace SpaceOverlap1.请记住这些名称的定义 2.后面所介绍的 layout rules 必须熟记,在画layout 时须遵守这些规则。

上华0.6um DPDM CMOS工艺拓扑 设计规则版图的层定义N-well P+ implantpoly1contactvia High Resistoractive N+ implantpoly2 metal1metal2设计规则 Nwell符号 尺寸含义1.a 3.0 阱的最小宽度1.b 4.8 不同电位阱的阱间距1.c 1.5 相同电位阱的阱间距P+ Active gb P+ fe N+ ActiveN+ c da2设计规则 Nwell符号 尺寸含义1.d 0.4 阱对其中N+有源区最小覆盖1.e 1.8 阱外N+有源区距阱最小间距1.f 1.8 阱对其中P+有源区最小覆盖1.g 0.4 阱外P+有源区距阱最小间距P+ Active gb P+ fe N+ ActiveN+ c da设计规则 active符号 尺寸含义2.a 0.6 用于互连的有源区最小宽度2.b 0.75 最小沟道宽度2.c 1.2 有源区最小间距aN+ c.4b P+P+ c.2ac.3 N+c.1 N+b设计规则 poly1可做MOS晶体管栅极、 导线、poly-poly电容的 下极板符号 尺寸含义4.a 0.6 用于互连的poly1最小宽度4.b 0.75 Poly1最小间距4.c 0.6 最小NMOS沟道长度4.d 0.6 最小PMOS沟道长度eeN+fbgcP+fbgadb设计规则 poly1可做MOS晶体管栅极、 导线、poly-poly电容的 下极板符号 尺寸含义4.e 0.6 硅栅最小出头量4.f 0.5 硅栅与有源区最小内间距4.g 0.3 场区poly1与有源区最小内 间距eeN+fbgcP+fbgadb设计规则 High Resistor在Poly2上定义高阻区符号 尺寸含义5.a 2.0 高阻最小宽度5.b 1.0 高阻最小间距5.c 1.0 高阻对poly2的最小覆盖5.d 1.0 高阻与poly2的间距d/f ce ha bf设计规则 High Resistor其上禁止布线 高阻层定义电阻长度 Poly2定义电阻宽度d/f c符 尺寸 号含义5.e 0.6 高阻与poly2电阻接触孔间距5.f 0.8 高阻与低阻poly2电阻的间距5.g 0.5 高阻与有源区的间距5.h 1.0 高阻与poly1电阻的间距a behf3设计规则 poly2可做多晶连线、多晶 电阻和poly-poly电容 的上极板符号 6.a 6.b 6.c6.d 6.e 6.f 6.g尺寸 1.2 1.0 0.5 3.2 1.5 0.8 -含义 poly2做电容时的最小宽度 poly2做电容时的最小间距 Poly2与有源区的最小间距 做关键电容时的间距 电容底板对顶板的最小覆盖 电容Poly2对接触孔最小覆盖 Poly2不能在有源区上 Poly2不能跨过poly1边沿c j ibdea设计规则 poly2可做多晶连线、多晶 电阻和poly-poly电容 的上极板符号 6.h 6.i 6.j 6.k 6.l 6.m尺寸含义0.8 poly2做导线时的最小宽度1.0 poly2做电阻时的最小间距1.0 Poly2电阻之间的最小间距- Poly2不能用做栅0.5 电阻Poly2对接触孔最小覆盖- 除做电容外,Poly2不能与 poly1重叠c j ibdea设计规则 implantb a符号 尺寸含义8.a 0.9 注入区最小宽度8.b 0.9 同型注入区最小间距8.c 0.6 注入区对有源区最小包围8.d 0.6 注入区与有源区最小间距Hc d N+Ef设计规则 implant符号 尺寸含义8.E 0.75 N+(P+)注入区与P+(N+)栅 间距8.f 0.75 N+(P+)注入区与N+(P+)栅 间距8.H 0 注入区对有源区最小覆盖 (定义butting contact)Hb ac d N+Ef设计规则 contact定义为金属1与扩散 区、多晶1、多晶2 的所有连接!符号 尺寸含义10.a .6*.6 接触孔最小面积10.a.1 .6*1.6 N+/P+ butting contact面积10.b 0.7 接触孔间距dgcafaba.1 ec.3g设计规则 contact符号 尺寸含义10.c 0.4 有源区,(d, e)Poly1, Poly2对最小孔最小覆盖10.c.3 0.8 有源区对butting contact最小覆盖10.f 0.6 漏源区接触孔与栅最小间距10.g 0.6 Poly1,2上孔与有源区最小间距dgcafaba.1 ec.3g4设计规则 metal1符号 尺寸含义11.a 0.9 金属1最小宽度11.b 0.8 金属1最小间距11.c.1 0.3 金属1对最小接触孔的最小覆盖11.c.2 0.6 金属1对butting contact的最小覆盖- 1.5mA 最大电流密度/um-- 禁止并行金属线90度拐角,用135度拐角代替ac.2bc.1 c.2设计规则 via定义为两层金属之 间的连接孔符号 尺寸含义12.a .7*.7 过孔最小面积12.b 0.8 过孔间距12.d~f - 接触孔、poly-poly电容和栅 上不能打过孔12.g 0.4 金属1对过孔的最小覆盖12.h 0.5 过孔与接触孔的最小间距建议 12.k0.5 Poly与有源区对过孔的最小 间距或覆盖1.5mA 单个过孔的最大电流agbhh设计规则 metal2可用于电源线、地 线、总线、时钟线 及各种低阻连接符号 尺寸含义13.a 0.9 金属2最小宽度13.b(e) 0.8 金属2最小间距13.c 0.4 金属2对过孔的最小覆盖13.d 1.5 宽金属2与金属2的最小间距13.f - 禁止并行金属线90度拐角,用 135度拐角代替13.h 1.5mA 最大电流密度 /umac be dd Width>10um设计规则 power supply line由于应力释放原符号 尺寸含义则,在大晶片上会17.a 20.0 金属2最小宽度存在与大宽度金属17.b 300.0 金属2最小长度总线相关的可靠性 问题。

Layout主要工作注意事项●画之前的准备工作●与电路设计者的沟通●Layout 的金属线尤其是电源线、地线●保护环●衬底噪声●管子的匹配精度一、l ayout 之前的准备工作1、先估算芯片面积先分别计算各个电路模块的面积,然后再加上模块之间走线以及端口引出等的面积,即得到芯片总的面积。

2、Top-Down 设计流程先根据电路规模对版图进行整体布局,整体布局包括:主要单元的大小形状以及位置安排;电源和地线的布局;输入输出引脚的放置等;统计整个芯片的引脚个数,包括测试点也要确定好,严格确定每个模块的引脚属性,位置。

3、模块的方向应该与信号的流向一致每个模块一定按照确定好的引脚位置引出之间的连线4、保证主信号通道简单流畅,连线尽量短,少拐弯等。

5、不同模块的电源,地线分开,以防干扰,电源线的寄生电阻尽可能较小,避免各模块的电源电压不一致。

6、尽可能把电容电阻和大管子放在侧旁,利于提高电路的抗干扰能力。

二、与电路设计者的沟通搞清楚电路的结构和工作原理明确电路设计中对版图有特殊要求的地方包含内容:(1)确保金属线的宽度和引线孔的数目能够满足要求(各通路在典型情况和最坏情况的大小)尤其是电源线盒地线。

(2)差分对管,有源负载,电流镜,电容阵列等要求匹配良好的子模块。

(3)电路中MOS管,电阻电容对精度的要求。

(4)易受干扰的电压传输线,高频信号传输线。

三、layout 的金属线尤其是电源线,地线1、根据电路在最坏情况下的电流值来确定金属线的宽度以及接触孔的排列方式和数目,以避免电迁移。

电迁移效应:是指当传输电流过大时,电子碰撞金属原子,导致原子移位而使金属断线。

在接触孔周围,电流比较集中,电迁移更容易产生。

2、避免天线效应长金属(面积较大的金属)在刻蚀的时候,会吸引大量的电荷,这时如果该金属与管子栅相连,可能会在栅极形成高压,影响栅养化层质量,降低电路的可靠性和寿命。

解决方案:(1)插一个金属跳线来消除(在低层金属上的天线效应可以通过在顶层金属层插入短的跳线来消除)。

第三章集成电路版图设计

每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)

什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)

制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:

最小线宽 Minimum Width

最小间距 Minimum Spacing

最小延伸 Minimum Extension

最小包围 Minimum Enclosure

最小覆盖 Minimum Overlay

集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!

3.2模拟集成电路版图设计中遵从的法则

3.2.1电容的匹配

对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容

易达到高精度的匹配。

在需要匹配的电容之问使用相同的单位电容就能够最大可能的实现匹配。

4)在匹配的电容四周摆放一些虚构的电容,能够有效减少工艺误差,这些虚构的电容也要和匹配的单位电容有相同的形状和大小,并有相同间距。

5)尽可能是需要匹配的电容大些。

增加电容的面积能有效减少随机的不匹配。

一般在CMOS工艺中比较适当的大小是20um×20um到50um×50um。

如果电容的面积大于1000um²,建议把它分成一些单位电容,做交叉耦合处理能够减少梯度影响以及提高全面匹配。

6)对于矩形阵列,尽可能减小纵横比,1:l是最佳的。

7)连接匹配电容的上极板到高阻抗信号上,这样比接下极板能够减少寄生电容。

如果衬底的噪音耦合也是非常关心,建议在整个电容建一个N阱,这个阱最好连接到一个干净的模拟参考电压,比如地线。

8)需要匹配的电容要远离大功耗的器件、开关晶体管以及数字晶体管,以减少耦合的影响。

9)不要在匹配电容上走金属线,减少噪音和耦合的影响。

3.2.2电阻的匹配

在IC版图(layout)的设计中,作为无源器件的电阻,其匹配也是很重要的,一个优秀的IC版图工程师将会遵守更多的匹配规则,使其因工艺产生的误差减小到最少。

1)遵循三个匹配的原则:电阻应该被放置相同的方向、相同的器件类型以及相互靠近。

这些原则对于减少工艺误差对模拟器件的功能的影响是非常有效的。

2)使用相同的类型、相同宽度、长度电阻以及相同的间距,版图如下图所示。

3)对于高精确的电阻,建议电阻的宽度为工艺最小宽度的5倍,这样能够有效降低工艺误差。

版图如下图所示。

4)对于高精确的电阻,建议电阻的宽度为工艺最小宽度的5倍,这样能够有效降低工艺误差。

版图如下图所示。

5)避免使用短的电阻,因为短的电阻更容易受工艺误差的影响,中度匹配的电阻一般应该大于5方块电阻,精确匹配的电阻一般至少不小于50um。

6)使用交叉阵列电阻。

如果阵列中有大量的电阻时,建议把电阻放置成多层的结构,形成二维阵列。

版图如下图所示。

7)匹配的电阻要远离大功率器件、开关晶体管以及数字晶体管,减少耦合的影响。

8)不要在匹配的电阻上使用金属连线,尽可能避免耦合和噪音的影响。

版图如下图所示。

9)对于一些阻值小于20欧姆的电阻,使用金属层(metal layer)来做电阻,会得到准确的阻值。

3.2.3 IC版图中的Metal slot和Metal density

在IC版图[layout]时,Design Rules中往往会注明金属线大于一定宽度时要挖slot,同时也会对metal density做出限定,小于规定的百分比时就要加dummy metal,由此看到的是这两条规则向着同一目的,那就是整个芯片上的金属的均匀性。

试想芯片上的金属密度不够均匀,有的地方密度大,有的地方密度小,那么在经过金属淀积后,metal density小的地方已经出现了低凹,再进行刻蚀和抛光后,原本Layout(版图)上metal density较低的区域,对应在wafer上此时的metal的厚度要相比metal density较高区域的薄。

故直接影响到wafer的平

坦度,从而影响后续工序的精准度,造成IC之电性不良、直接影响wafer的良率。

当整个芯片layout金属密度过低时,wafer 上对应需要刻蚀掉的metal量就多,容易造成刻蚀不干净,有过多metal残留于wafer上,影响后续工序。

而当整个芯片layout金属密度过高时,则wafer 上对应需要刻蚀掉的metal量就少,容易造成刻蚀过量,对正常的metal导线也去刻蚀掉。

3.2.4 IC设计中的几种功率管版图

1)常规连线

优点:提供了源极和漏极间最大可能的金属连线数量,使连线宽度最大化

缺点:产生额外压使器件中的电流分布不均匀

3.2.5 IC设计中实际的设计规则(见附件)

2)对角连线

优点:逐渐变细的总线可以减小偏置效应,使电流均匀分布于晶体管各叉指。

3)华夫饼式

优点:面积最省

缺点:a)没有考虑金属边线影响;b)沟道存在大量转弯;c)没有背栅接触。

4)曲栅式

曲栅增加了栅极的宽度,使栅极捏死紧密,可以轻易地容纳分布式背栅接触孔,栅极135度弯曲不易发生局部雪崩击穿,源和漏接触孔对角放置增加源、漏限流作用,改善器件稳定性。