第二章-版图设计规则

- 格式:ppt

- 大小:3.27 MB

- 文档页数:86

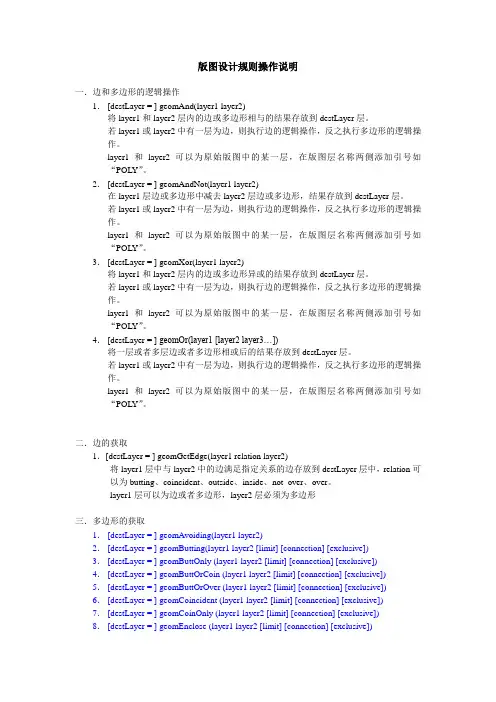

版图设计规则操作说明一.边和多边形的逻辑操作1.[destLayer = ] geomAnd(layer1 layer2)将layer1和layer2层内的边或多边形相与的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

2.[destLayer = ] geomAndNot(layer1 layer2)在layer1层边或多边形中减去layer2层边或多边形,结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

3.[destLayer = ] geomXor(layer1 layer2)将layer1和layer2层内的边或多边形异或的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

4.[destLayer = ] geomOr(layer1 [layer2 layer3…])将一层或者多层边或者多边形相或后的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

二.边的获取1.[destLayer = ] geomGetEdge(layer1 relation layer2)将layer1层中与layer2中的边满足指定关系的边存放到destLayer层中,relation可以为butting、coincident、outside、inside、not_over、over。

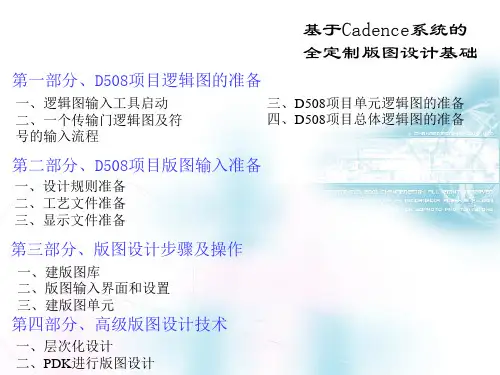

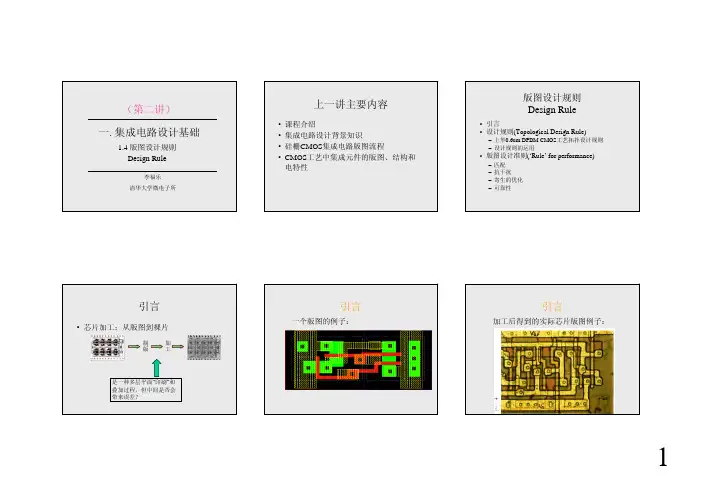

(第二讲)一. 集成电路设计基础1.4 版图设计规则 Design Rule李福乐 清华大学微电子所上一讲主要内容• 课程介绍 • 集成电路设计背景知识 • 硅栅CMOS集成电路版图流程 • CMOS工艺中集成元件的版图、结构和电特性版图设计规则Design Rule• 引言 • 设计规则(Topological Design Rule)– 上华0.6um DPDM CMOS工艺拓扑设计规则 – 设计规则的运用• 版图设计准则(‘Rule’ for performance)– 匹配 – 抗干扰 – 寄生的优化 – 可靠性引言• 芯片加工:从版图到裸片制加版工是一种多层平面“印刷”和 叠加过程,但中间是否会 带来误差?引言一个版图的例子:引言加工后得到的实际芯片版图例子:1引言• 加工过程中的非理想因素– 制版光刻的分辨率问题 – 多层版的套准问题 – 表面不平整问题 – 流水中的扩散和刻蚀问题 – 梯度效应引言• 解决办法– 厂家提供的设计规则(topological design rule),确保完成设计功能和一定的芯片成 品率,除个别情况外,设计者必须遵循– 设计者的设计准则(‘rule’ for performance),用以提高电路的某些性 能,如匹配,抗干扰,速度等设计规则(topological design rule)基本定义(Definition) WidthEnclosure设计规则ExtensionExtensionSpace SpaceOverlap1.请记住这些名称的定义 2.后面所介绍的 layout rules 必须熟记,在画layout 时须遵守这些规则。

上华0.6um DPDM CMOS工艺拓扑 设计规则版图的层定义N-well P+ implantpoly1contactvia High Resistoractive N+ implantpoly2 metal1metal2设计规则 Nwell符号 尺寸含义1.a 3.0 阱的最小宽度1.b 4.8 不同电位阱的阱间距1.c 1.5 相同电位阱的阱间距P+ Active gb P+ fe N+ ActiveN+ c da2设计规则 Nwell符号 尺寸含义1.d 0.4 阱对其中N+有源区最小覆盖1.e 1.8 阱外N+有源区距阱最小间距1.f 1.8 阱对其中P+有源区最小覆盖1.g 0.4 阱外P+有源区距阱最小间距P+ Active gb P+ fe N+ ActiveN+ c da设计规则 active符号 尺寸含义2.a 0.6 用于互连的有源区最小宽度2.b 0.75 最小沟道宽度2.c 1.2 有源区最小间距aN+ c.4b P+P+ c.2ac.3 N+c.1 N+b设计规则 poly1可做MOS晶体管栅极、 导线、poly-poly电容的 下极板符号 尺寸含义4.a 0.6 用于互连的poly1最小宽度4.b 0.75 Poly1最小间距4.c 0.6 最小NMOS沟道长度4.d 0.6 最小PMOS沟道长度eeN+fbgcP+fbgadb设计规则 poly1可做MOS晶体管栅极、 导线、poly-poly电容的 下极板符号 尺寸含义4.e 0.6 硅栅最小出头量4.f 0.5 硅栅与有源区最小内间距4.g 0.3 场区poly1与有源区最小内 间距eeN+fbgcP+fbgadb设计规则 High Resistor在Poly2上定义高阻区符号 尺寸含义5.a 2.0 高阻最小宽度5.b 1.0 高阻最小间距5.c 1.0 高阻对poly2的最小覆盖5.d 1.0 高阻与poly2的间距d/f ce ha bf设计规则 High Resistor其上禁止布线 高阻层定义电阻长度 Poly2定义电阻宽度d/f c符 尺寸 号含义5.e 0.6 高阻与poly2电阻接触孔间距5.f 0.8 高阻与低阻poly2电阻的间距5.g 0.5 高阻与有源区的间距5.h 1.0 高阻与poly1电阻的间距a behf3设计规则 poly2可做多晶连线、多晶 电阻和poly-poly电容 的上极板符号 6.a 6.b 6.c6.d 6.e 6.f 6.g尺寸 1.2 1.0 0.5 3.2 1.5 0.8 -含义 poly2做电容时的最小宽度 poly2做电容时的最小间距 Poly2与有源区的最小间距 做关键电容时的间距 电容底板对顶板的最小覆盖 电容Poly2对接触孔最小覆盖 Poly2不能在有源区上 Poly2不能跨过poly1边沿c j ibdea设计规则 poly2可做多晶连线、多晶 电阻和poly-poly电容 的上极板符号 6.h 6.i 6.j 6.k 6.l 6.m尺寸含义0.8 poly2做导线时的最小宽度1.0 poly2做电阻时的最小间距1.0 Poly2电阻之间的最小间距- Poly2不能用做栅0.5 电阻Poly2对接触孔最小覆盖- 除做电容外,Poly2不能与 poly1重叠c j ibdea设计规则 implantb a符号 尺寸含义8.a 0.9 注入区最小宽度8.b 0.9 同型注入区最小间距8.c 0.6 注入区对有源区最小包围8.d 0.6 注入区与有源区最小间距Hc d N+Ef设计规则 implant符号 尺寸含义8.E 0.75 N+(P+)注入区与P+(N+)栅 间距8.f 0.75 N+(P+)注入区与N+(P+)栅 间距8.H 0 注入区对有源区最小覆盖 (定义butting contact)Hb ac d N+Ef设计规则 contact定义为金属1与扩散 区、多晶1、多晶2 的所有连接!符号 尺寸含义10.a .6*.6 接触孔最小面积10.a.1 .6*1.6 N+/P+ butting contact面积10.b 0.7 接触孔间距dgcafaba.1 ec.3g设计规则 contact符号 尺寸含义10.c 0.4 有源区,(d, e)Poly1, Poly2对最小孔最小覆盖10.c.3 0.8 有源区对butting contact最小覆盖10.f 0.6 漏源区接触孔与栅最小间距10.g 0.6 Poly1,2上孔与有源区最小间距dgcafaba.1 ec.3g4设计规则 metal1符号 尺寸含义11.a 0.9 金属1最小宽度11.b 0.8 金属1最小间距11.c.1 0.3 金属1对最小接触孔的最小覆盖11.c.2 0.6 金属1对butting contact的最小覆盖- 1.5mA 最大电流密度/um-- 禁止并行金属线90度拐角,用135度拐角代替ac.2bc.1 c.2设计规则 via定义为两层金属之 间的连接孔符号 尺寸含义12.a .7*.7 过孔最小面积12.b 0.8 过孔间距12.d~f - 接触孔、poly-poly电容和栅 上不能打过孔12.g 0.4 金属1对过孔的最小覆盖12.h 0.5 过孔与接触孔的最小间距建议 12.k0.5 Poly与有源区对过孔的最小 间距或覆盖1.5mA 单个过孔的最大电流agbhh设计规则 metal2可用于电源线、地 线、总线、时钟线 及各种低阻连接符号 尺寸含义13.a 0.9 金属2最小宽度13.b(e) 0.8 金属2最小间距13.c 0.4 金属2对过孔的最小覆盖13.d 1.5 宽金属2与金属2的最小间距13.f - 禁止并行金属线90度拐角,用 135度拐角代替13.h 1.5mA 最大电流密度 /umac be dd Width>10um设计规则 power supply line由于应力释放原符号 尺寸含义则,在大晶片上会17.a 20.0 金属2最小宽度存在与大宽度金属17.b 300.0 金属2最小长度总线相关的可靠性 问题。

版图课程设计规则一、教学目标本课程的教学目标是使学生掌握XX学科的基本概念、原理和方法,能够运用所学知识解决实际问题;提高学生的XX技能,如观察、实验、分析、推理等;培养学生的科学态度和价值观,使其具备创新精神和团队合作能力。

具体目标如下:1.知识目标:(1)了解XX学科的基本概念和原理;(2)掌握XX学科的基本方法和技能;(3)熟悉XX学科的发展历程和现状。

2.技能目标:(1)能够运用所学知识解决实际问题;(2)具备观察、实验、分析、推理等基本科研能力;(3)学会查阅文献、整理资料、撰写科研报告。

3.情感态度价值观目标:(1)培养对XX学科的兴趣和热情;(2)树立科学精神和批判性思维;(3)具备团队合作能力和创新意识。

二、教学内容根据课程目标,本课程的教学内容主要包括以下几个方面:1.XX学科的基本概念和原理:通过讲解、案例分析等方式,使学生了解并掌握XX学科的基本知识。

2.XX学科的基本方法和技能:通过实验、实践等方式,让学生学会运用所学知识解决实际问题。

3.XX学科的发展历程和现状:通过介绍相关历史事件和前沿动态,使学生了解XX学科的发展脉络。

4.实际问题的解决:引导学生运用所学知识分析、解决实际问题,提高学生的实践能力。

三、教学方法本课程采用多种教学方法,以激发学生的学习兴趣和主动性:1.讲授法:系统地传授学科知识,为学生提供扎实的理论基础。

2.讨论法:学生进行小组讨论,培养学生的思考能力和团队合作精神。

3.案例分析法:通过分析典型病例,使学生学会将理论知识应用于实际问题。

4.实验法:引导学生动手实践,培养学生的实验技能和科研素养。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将采用以下教学资源:1.教材:选用国内权威的XX学科教材,为学生提供系统的知识结构。

2.参考书:推荐相关领域的经典著作和最新研究论文,拓宽学生的知识视野。

3.多媒体资料:利用课件、视频等资料,提高课堂教学的趣味性和生动性。