第4章 Quartus II 使用方法嵌入式逻辑分析仪

- 格式:pps

- 大小:1.29 MB

- 文档页数:120

Quartus II: SignalTap II Logic Analyzer的使用教程(基于quartus II 13.0)

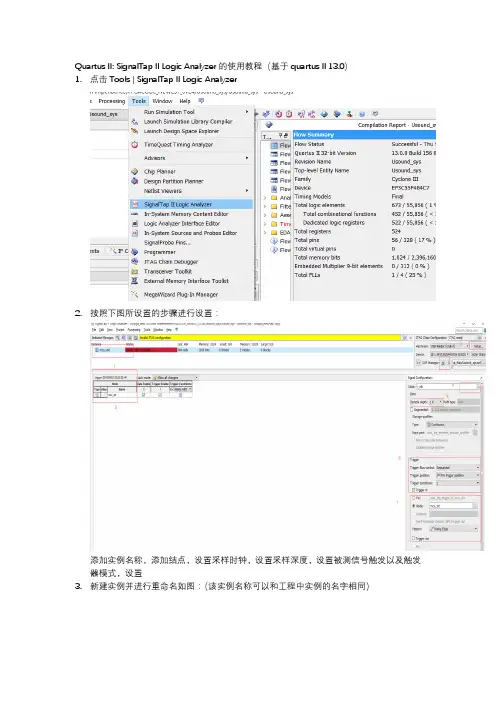

1.点击Tools | SignalTap II Logic Analyzer

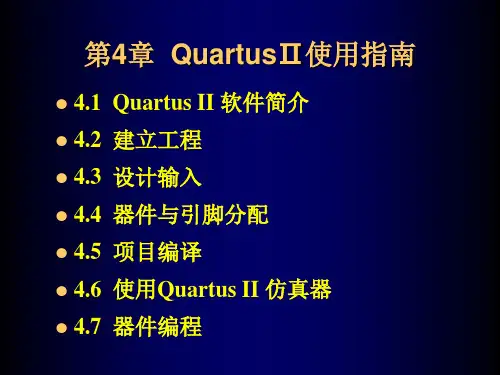

2.按照下图所设置的步骤进行设置:

添加实例名称,添加结点,设置采样时钟,设置采样深度,设置被测信号触发以及触发器模式,设置

3.新建实例并进行重命名如图:(该实例名称可以和工程中实例的名字相同)

4.为仿真实例添加结点,按软件提示新建结点

4.1打开结点查找器,将新建的实例的与工程中的信号结点绑定起来。

如图:点击1处设置过滤类型为前综合类型,点击2处的List,选择相应的结点。

4.2点击下图1导入结点,设置完成后,点击2处确定。

5.信号配置:

a)设置采样时钟:

点击1处,打开结点查找器,点击2搜索相应结点,并导入工程系统时钟,设置完

成后点击OK

b)设置采样深度,以及信号触发模式以及触发器模式按照下图进行设置即可

6.所有设置完成后点击保存,

7.按照如图下步骤进行硬件配置以及下载,然后进行JTAG调试

点击2处设置JTAG连接器硬件,

点击3处进行FPGA芯片扫描

点击4处进行下载

点击1处进行调试,观察仿真结果

8.运行结果如图所示:

9.注意:断电之后拔掉JTAG。

静电可以击穿芯片。

QuartusII软件使用说明Quartus II软件使用说明1.介绍Quartus II是一款由Intel开发的集成电路设计软件,主要用于数字逻辑电路的设计和开发。

本文将详细介绍Quartus II软件的安装、基本功能以及常用的设计流程。

2.安装2.1 硬件要求确定您的计算机是否符合Quartus II的硬件要求,包括处理器、内存和硬盘空间。

2.2 安装程序从Intel官方网站Quartus II的安装程序,并按照指引执行安装步骤。

2.3 许可证文件在安装过程中,您需要提供许可证文件以完成软件的激活。

3.Quartus II界面3.1 工程导航器工程导航器是Quartus II的主界面,您可以在此查看和管理当前项目下的所有文件和文件夹。

3.2 编辑器Quartus II提供了多种编辑器,包括原理图编辑器、文本编辑器和波形编辑器等。

您可以根据需要选择适合的编辑器进行设计和编码。

4.基本功能4.1 创建新工程在工程导航器中,选择“新建”并指定工程名称和存储位置,然后选择设计类型和顶层设计文件。

4.2 添加文件通过“添加文件”功能可以将需要的文件添加到工程中,包括原理图文件、VHDL文件和Verilog文件等。

4.3 综合与分析在设计过程中,需要进行综合和分析以验证电路功能和逻辑正确性。

4.4 时序约束通过时序约束可以设置电路的时钟频率、延迟和时序要求等。

4.5 编译报告编译报告可以查看设计的状态和一些警告或错误信息。

5.设计流程5.1 设计规划在设计之前,需要进行设计规划,包括确定设计目标、功能分析和资源规划等。

5.2 电路设计按照设计规划进行电路设计,包括原理图设计、RTL设计和模块设计等。

5.3 综合与优化对设计进行综合和优化,以达到性能和资源的平衡。

5.4 约束设置与时序分析设置时序约束并进行时序分析,以保证电路满足时序要求。

5.5 布局与布线对设计进行物理布局和布线,以优化电路的布局及信号传输路径。

使用SignalTap II逻辑分析仪调试FPGA摘要:本文介绍了可编程逻辑器件开发工具Quartus II 中SingalTap II 嵌入式逻辑分析器的使用,并给出一个具体的设计实例,详细介绍使用SignalTap II对FPGA调试的具体方法和步骤。

关键字: SignalTap;硬件调试;FPGA1 概述--- 随着FPGA容量的增大,FPGA的设计日益复杂,设计调试成为一个很繁重的任务。

为了使得设计尽快投入市场,设计人员需要一种简易有效的测试工具,以尽可能的缩短测试时间。

传统的逻辑分析仪在测试复杂的FPGA设计时,将会面临以下几点问题:1)缺少空余I/O引脚。

设计中器件的选择依据设计规模而定,通常所选器件的I/O引脚数目和设计的需求是恰好匹配的。

2)I/O引脚难以引出。

设计者为减小电路板的面积,大都采用细间距工艺技术,在不改变PCB板布线的情况下引出I/O引脚非常困难。

3)外接逻辑分析仪有改变FPGA设计中信号原来状态的可能,因此难以保证信号的正确性。

4)传统的逻辑分析仪价格昂贵,将会加重设计方的经济负担。

--- 伴随着EDA工具的快速发展,一种新的调试工具Quartus II 中的SignalTap II 满足了FPGA开发中硬件调试的要求,它具有无干扰、便于升级、使用简单、价格低廉等特点。

本文将介绍SignalTap II逻辑分析仪的主要特点和使用流程,并以一个实例介绍该分析仪具体的操作方法和步骤。

2 SignalTap II的特点及使用--- SignalTap II嵌入逻辑分析仪集成到Quartus II设计软件中,能够捕获和显示可编程单芯片系统(SOPC)设计中实时信号的状态,这样开发者就可以在整个设计过程中以系统级的速度观察硬件和软件的交互作用。

它支持多达1024个通道,采样深度高达128Kb,每个分析仪均有10级触发输入/输出,从而增加了采样的精度。

SignalTap II为设计者提供了业界领先的SOPC设计的实时可视性,能够大大减少验证过程中所花费的时间。

第1章QUARTUS II2。

1 QUARTUSII概述设计输入是设计者对系统要实现的逻辑功能进行描述的过程。

设计输入有多种表达方式,常用的用原理图输入、硬件描述语言输入、网表输入等。

1、原理图输入:原理图设计输入方式是利用软件提供的各种原理图库,采用画图的方式进行设计输入.这是一种最为简单和直观的输入方式。

原理图输入方式的效率比较低,半只用于小规模系统设计,或用于在顶层拼接各个以设计完成的电路子模块。

2、硬件描述语言输入:这种设计输入方式是通过文本编辑器,用VHDL,Verilog或AHDL等硬件描述语言进行设计输入。

采用语言描述的有点事效率较高,结果容易仿真,信号观察方便,在不同的设计输入库之间转换方便,适用于大规模数字系统的设计.但语言输入必须依赖综合器,只有好的综合器才能把语言综合成优化的电路。

3、网表输入:现代可编程数字系统设计工具都提供了和它第三方EDA工具相连接的接口。

采用这种方法输入时,可以通过标准的网表把它设计工具上已经实现了的设计直接移植进来,而不必重新输入。

一般开发软件可以接受的网表有EDIF格式、VHDL 格式及Verilog格式等。

在用网表输入时,必须注意在两个系统中采用库的对应关系,所有的库单元必须一一对应,才可以成功读入网表[6]。

2.2 QUARTUSII建立工程项目在Quartus II 中,用户的每个独立设计都对应一个工程项目,每个工程项目可包含一个或多个设计文件。

其中一个是顶层文件,编译器是对项目中的顶层文件进行编译的,项目同时还管理编译过程中产生的各种中间文件,这些中间文件的文件名相同,但后缀名不同.为了便于管理,对于每个新的项目应该建立一个单独的子目录。

指定项目名称的步骤如下:1。

打开Quartus II,在File 菜单中选择New Project Wizard 项,将出现工程项目建立向导对话框。

如图2—1 (a)所示。

2. 点击“Next”,进入到如图2-1 (b)所示的工程项目命名对话框,在最上面的文本输入框中输入为该项目所建的目录名,如本例为“E:\Clock”,在中间的文本输入框中输入项目名称,本次实验为“adder”,在最下面的文本输入框中输入最顶层模块的名称“adder"。

实验二、嵌入式逻辑分析仪注意事项:1、特别注意:在做Quartus II 工程时必须将未分配的管脚置为三态输入。

Quartus II --> Assignments --> Device … --> Device --> Device & Pin Options … --> Unused Pins --> Reserve all unused pins : AS input tri-stated 。

2、按键SW1—SW4与LED 指示灯LED1—LED4分布图如下:FPGA 管脚备注3、系统复位与系统时钟(50MHz )分配脚PORT B 信号分配表如下:5、对EP3C25-B型电路板的LED与按键测试程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY LED_BOTTON ISPORT ( BOTTON_IN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED_OUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END LED_BOTTON;ARCHITECTURE A OF LED_BOTTON ISBEGINLED_OUT <= not BOTTON_IN;END A;管脚分配为:BOTTON_IN分别接N1(SW1)、N2(SW2)、U9(SW3)、V9(SW4);LED_OUT分别接:P11(LED1)、U11(LED2)、R11(LED3)、N11(LED4)。

按注意事项1进行设置!!!之后再次编译!内容一、十进制加法计数器的设计1、设计一个异步复位和同步时钟使能的十进制加法计数器;2、VHDL代码见课本例3-21;3、管脚分配如下:CLK接V10脚(50MHz),RST接N1(SW1),EN接N2(SW2),CQ分别接:N11(LED4)、R11(LED3)、U11(LED2)、P11(LED1),COUT接N6。

EDA技术与VHDL

第4章Qiartus II 使用方法

1.创建工程准备工作

KONXIN

1.创建工程准备工作

2. 创建工程

2.创建工程

2.创建工程

3.编译前设置

3.编译前设置

4.全程编译

K X康芯科技

K X康芯科技4.1 QuartusII设计流程

5.时序仿真

5

.时序仿真

图4-10 波形编辑器

5

.时序仿真

图4-11 设置仿真时间长度

5

.时序仿真

图4-12 .vwf激励波形文件存盘

4.1.2 创建工程

图4-13 向波形编辑器拖入信号节点

5

.时序仿真

图4-14 设置时钟CLK的周期

5

.时序仿真

图4-15 设置好的激励波形图

5

.时序仿真

图4-16 选择总线数据格式

5

.时序仿真

图4-17 选择仿真控制

5

.时序仿真

图4-18 仿真波形输出

5

.时序仿真

图4-19 选择全时域显示

6.观察RTL电路

7

.引脚锁定和下载

图4-20 Assignment Editor编辑器

7

.引脚锁定和下载

图4-21 表格方式引脚锁定对话框图

7

.引脚锁定和下载

4-22 图形方式引脚锁定对话框

8

.编程下载

图4-23 选择编程下载文件

8

.编程下载

图4-24加入编程下载方式

8

.编程下载

图4-25 双击选中的编程方式名

9.AS

模式编程

图4-26 ByteBlaster II接口AS模式编程窗口

10.JTAG

间接模式编程

图4-27 选择目标器件EP1C6Q240

10.JTAG 间接模式编程

图4-28 选定SOF文件后,选择文件压缩

10.JTAG

间接模式编程

图4-29 用JTAG模式对配置器件EPCS1进行间接编程

逻辑分析仪是一种类似于示波器的波形测试设备,它可以监测硬件电路工作时的逻辑电平(高或低),并加以存储,用图形的方式直观地表达出来,便于用户检测、分析电路设计(硬件设计和软件设计) 中的错误,逻辑分析仪是设计中不可缺少的设备,通过它,可以迅速地定位错误,解决问题,达到事半功倍的效果。

逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,最主要作用在于时序判定。

由于逻辑分析仪不像示波器那样有许多电压等级,通常只显示两个电压(逻辑1和0),因此设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参考电压者为High,低于参考电压者为Low,在High与Low之间形成数字波形。

例如:一个待测信号使用200MHz采样率的逻辑分析仪,当参考电压设定为1.5V时,在测量时逻辑分析仪就会平均每5ns采取一个点,超过1.5V者为High(逻辑1),低于1.5V者为Low(逻辑0),而后的逻辑1和0可连接成一个简单波形,工程师便可在此连续波形中找出异常错误(bug)之处。

整体而言,逻辑分析仪测量被测信号时,并不会显示出

电压值,只是High跟Low的差别;如果要测量电压就

一定需要使用示波器。

除了电压值的显示不同外,逻辑

分析仪与示波器的另一个差别在于通道数量。

一般的示

波器只有2个通道或4个通道,而逻辑分析仪可以拥有从16个通道、32个通道、64个通道和上百个通道数不等,因此逻辑分析仪具备同时进行多通道测试的优势。

根据硬件设备设计上的差异,目前市面上逻辑分析仪大

致上可分为独立式(或单机型)逻辑分析仪和需结合电

脑的PC-based卡式虚拟逻辑分析仪。

独立式逻辑分析仪是将所有的测试软件、运算管理元件以及整合在一台

仪器之中;卡式虚拟逻辑分析仪则需要搭配电脑一起使用,显示屏也与主机分开。

嵌入式逻辑分析仪可以随设计文件一并下载于目标芯片中,用以捕捉目标芯片内部系统信号节点处的信息或总线上的数据流,而又不影响原硬件系统的正常工作。

1.打开SignalTap II编辑窗

2.调入待测信号3.SignalTap II参数设置

4.文件存盘

5.编译下载

6.启动SignalTap II进行采样与分析

6.启动SignalTap II

进行采样与分析

图4-33 SignalTap II数据窗设置后的信号波形

图4-34 选择高级触发条件

图4-35 进入“触发条件函数编辑”窗口

4.3 编辑SignalTapII的触发信号

图4-36 编辑触发函数

4.4.1

工作原理

图4-37 正弦信号发生器结构框图

4.4.2 定制初始化数据文件

1.建立.mif格式文件

【例4-1】

WIDTH = 8;

DEPTH = 64;

ADDRESS_RADIX = HEX;

DATA_RADIX = HEX;

CONTENT BEGIN

0 : FF;

1 : FE;

2 : FC;

3 : F9;

4 : F5;

…(数据略去)

3D : FC;

3E : FE;

3F : FF;

END;

4.4.2 定制初始化数据文件

1.建立.mif格式文件

【例4-2】

#include <stdio.h>

#include "math.h"

main()

{int i;float s;

for(i=0;i<1024;i++)

{ s = sin(atan(1)*8*i/1024);

printf("%d :

%d;\n",i,(int)((s+1)*1023/2));

}

}

把上述程序编译成程序后,可在DOS命令行下执行命令:romgen > sin_rom.mif;

4.4.2 定制初始化数据文件

2.建立.hex格式文件

图4-38 将波形数据填入mif文件表中

图4-39 ASM格式建hex文件

4.4.2 定制初始化数据文件

2.建立.hex格式文件

图4-40 sdata.hex文件的放置路径

4.4.3 定制LPM_ROM元件

图4-41 定制新的宏功能块

4.4.3 定制LPM_ROM元件

图4-42 LPM宏功能块设定

4.4.3 定制LPM_ROM元件

图4-43 选择data_rom模块数据线和地址线宽。