数字电路:4 组合逻辑电路

- 格式:pdf

- 大小:1.60 MB

- 文档页数:172

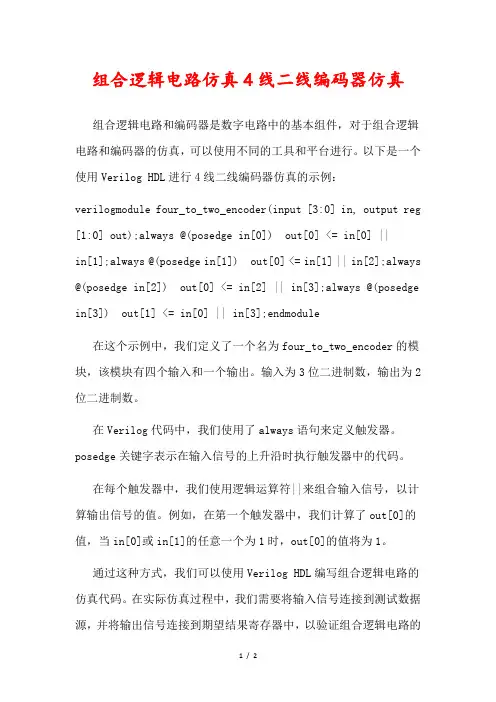

组合逻辑电路仿真4线二线编码器仿真组合逻辑电路和编码器是数字电路中的基本组件,对于组合逻辑电路和编码器的仿真,可以使用不同的工具和平台进行。

以下是一个使用Verilog HDL进行4线二线编码器仿真的示例:verilogmodule four_to_two_encoder(input [3:0] in, output reg [1:0] out);always @(posedge in[0]) out[0] <= in[0] ||in[1];always @(posedge in[1]) out[0] <= in[1] || in[2];always @(posedge in[2]) out[0] <= in[2] || in[3];always @(posedge in[3]) out[1] <= in[0] || in[3];endmodule在这个示例中,我们定义了一个名为four_to_two_encoder的模块,该模块有四个输入和一个输出。

输入为3位二进制数,输出为2位二进制数。

在Verilog代码中,我们使用了always语句来定义触发器。

posedge关键字表示在输入信号的上升沿时执行触发器中的代码。

在每个触发器中,我们使用逻辑运算符||来组合输入信号,以计算输出信号的值。

例如,在第一个触发器中,我们计算了out[0]的值,当in[0]或in[1]的任意一个为1时,out[0]的值将为1。

通过这种方式,我们可以使用Verilog HDL编写组合逻辑电路的仿真代码。

在实际仿真过程中,我们需要将输入信号连接到测试数据源,并将输出信号连接到期望结果寄存器中,以验证组合逻辑电路的正确性。

除了Verilog HDL外,还有其他工具和平台可以用于组合逻辑电路和编码器的仿真,例如ModelSim、Quartus等。

无论使用哪种工具和平台,都需要对数字电路的原理和逻辑进行深入理解,并进行适当的测试和验证,以确保数字电路的正确性和可靠性。

组合逻辑电路实验原理

组合逻辑电路的实验原理基于布尔代数和逻辑运算。

布尔代数是一种数学工具,用于描述逻辑运算的规则和性质。

逻辑运算包括与、或、非、异或等运算,这些运算可以用逻辑门实现。

逻辑门是一种基本的数字电路元件,可以用于实现逻辑运算,并将输入信号转换为输出信号。

在组合逻辑电路实验中,通常需要遵循以下步骤:

1. 确定输入和输出信号的类型和数量。

输入信号可以是数字信号、模拟信号或混合信号,而输出信号通常是数字信号。

2. 根据逻辑运算的规则和性质,确定所需的逻辑门的类型和数量。

常见的逻辑门包括与门、或门、非门、异或门等。

3. 根据逻辑门的输入和输出特性,设计电路的结构,确定逻辑门的连接方式和电路的配置。

逻辑门的输入和输出可以是单个信号或多个信号,可以串联或并联连接。

4. 进行逻辑电路的仿真和测试,验证电路的正确性和可靠性。

可以使用数字电路仿真软件进行仿真测试,并使用数字信号发生器和示波器等测试仪器进行实际测试。

以数据选择器为例,数据选择器也称多路开关,通过改变地址输

入信号,可以在多个数据输入中选择一个传送到输出。

例如,74151是一种常见的8选1数据选择器,具有3位地址输入、8路数据输入、一个使能信号以及一对互补的输出。

如需了解更多信息,可以查阅数字逻辑或计算机组织相关教材,或者咨询相关专业的老师或工程师。

组合逻辑电路仿真4线二线编码器仿真组合逻辑电路和时序逻辑电路是数字电路的基本类型。

其中,组合逻辑电路用于处理逻辑函数之间的关系,而时序逻辑电路则用于处理带有存储元件的电路。

在组合逻辑电路中,所有的输出信号都只与当前的输入信号有关,而与之前的输入信号无关。

一个组合逻辑电路的仿真过程可以通过以下步骤来完成:确定组合逻辑电路的结构和组成:首先需要明确该电路由哪些基本逻辑元件组成,以及这些元件之间的连接方式。

例如,一个四线二线编码器,它由四个输入信号和两个输出信号组成,输入信号用于选择不同的编码状态,而输出信号则用于表示该编码状态。

确定各个元件的逻辑功能:对于每个元件,需要明确其具体的逻辑功能。

例如,对于一个四线二线编码器,它的逻辑功能是将四个输入信号中的两个进行组合,以产生两个输出信号。

确定输入信号的组合方式:根据组合逻辑电路的要求,所有的输出信号都只与当前的输入信号有关,因此需要确定输入信号的组合方式。

对于一个四线二线编码器,它可以通过四种不同的输入组合方式来产生不同的编码状态。

确定输出信号的处理方式:根据组合逻辑电路的要求,输出信号需要反映当前的输入状态。

对于一个四线二线编码器,它的两个输出信号分别表示当前的编码状态和反码状态。

进行仿真测试:在明确了组合逻辑电路的所有元件和功能之后,可以使用仿真工具进行仿真测试。

例如,对于一个四线二线编码器,可以使用仿真工具来模拟不同的输入组合方式,并观察相应的输出信号。

在进行组合逻辑电路仿真时,需要注意以下几点:确保仿真工具的正确性:由于仿真工具只是模拟电路的行为,因此需要确保仿真工具本身是正确的。

确认输入信号的正确性:在模拟组合逻辑电路时,需要确保输入信号的正确性。

如果输入信号不正确,则可能会导致错误的输出结果。

确认输出信号的正确性:在模拟组合逻辑电路时,需要确保输出信号的正确性。

如果输出信号不正确,则可能会导致错误的判断和决策。

考虑特殊情况:在模拟组合逻辑电路时,需要考虑一些特殊情况,例如输入信号的噪声、干扰等。

第三章组合逻辑电路基本知识点*组合逻辑电路的特点*组合逻辑电路功能的表示方法及相互转换*组合逻辑电路的分析方法和设计方法*常用集成组合逻辑电路的逻辑功能、使用方法和应用举例*组合逻辑电路中的竞争–冒险现象及消除竞争–冒险现象的常用方法3.1概述在数字电路中根据逻辑功能的不同特点,可将其分为两大类:一类是组合逻辑电路,另一类是时序逻辑电路。

组合逻辑电路在逻辑功能上的共同特点是:任意时刻的输出状态仅取决于该时刻的输入状态,与电路原来的状态无关。

在电路结构上的特点是:它是由各种门电路组成的,而且只有从输入到输出的通路,没有从输出到输入的反馈回路。

由于组合逻辑电路的输出状态与电路的原来状态无关,所以组合逻辑电路是一种无记忆功能的电路。

由此可知第二章中介绍的各种门电路都属于组合逻辑电路。

描述一个组合逻辑电路逻辑功能的方法很多,通常有:逻辑函数表达式、真值表、逻辑图、卡诺图、波形图五种。

它们各有特点,又相互联系,还可以相互转换。

3. 2逻辑功能各种表示方法的特点及其相互转换一、逻辑功能各种表示方法的特点1、逻辑函数表达式逻辑表达式是用与、或、非等基本运算来表示输入变量和输出函数因果关系的逻辑代数式。

其特点是形式简单、书写方便,便于进行运算和转换。

但表达式形式不唯一。

2、真值表真值表是根据给定的逻辑问题,把输入变量的各种取值的组合和对应的输出函数值排列成表格。

其特点是:直观、明了,可直接看出输入变量与输出函数各种取值之间的一一对应关系。

真值表具有唯一性。

3、逻辑图逻辑图是用若干基本逻辑符号连接成的电路图。

其特点是:与实际使用的器件有着对应关系,比较接近于实际的电路,但它只反映电路的逻辑功能而不反映电气参数和性能。

同一种逻辑功能可以用多种逻辑图实现,它不具备唯一性。

4、卡诺图卡诺图是按相邻性原则排列的最小项的方格图。

它实际上是真值表的特定的图示形式。

其特点是在化简逻辑函数时比较直观容易掌握。

卡诺图具有唯一性,但化简后的逻辑表达式不是唯一的。

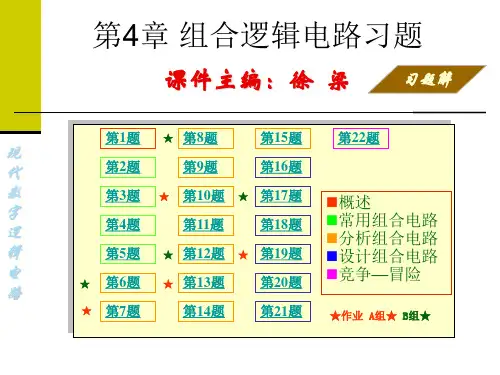

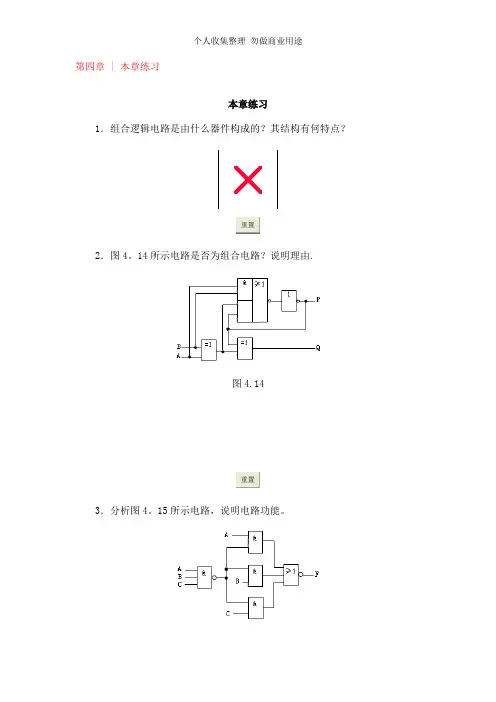

第四章 | 本章练习本章练习1.组合逻辑电路是由什么器件构成的?其结构有何特点?重置2.图4。

14所示电路是否为组合电路?说明理由.图4.14重置3.分析图4。

15所示电路,说明电路功能。

重置4.分析图4.16所示电路,试画出用异或门实现该电路功能的最简电路.图4.16重置5.分析图4.17所示电路,试列出真值表,说明电路功能.重置A B C D W X Y Z A B C D W X Y Z0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 10 0 0 00 0 0 10 0 1 10 0 1 00 1 1 00 1 1 10 1 0 10 1 0 01 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 11 1 0 01 1 0 11 1 1 11 1 1 01 0 1 01 0 1 11 0 0 11 0 0 06.分析图4。

18所示电路,设输入ABCD为8421码,试列出真值表,说明电路功能。

图4.18重置A B C D W X Y Z A B C D W X Y Z0 0 0 0 1 0 0 1 0 1 0 1 0 1 0 07.设计一个组合逻辑电路,该电路输入端接收两个两位无符号二进制数A=A 1A 0和B=B 1B 0,当A=B 时,输出F 为1,否则F 为0。

试用合适的逻辑门构造出最简电路。

8.设计一个代码转换电路,将一位十进制数的8421码转换成余3码.9.用与非门设计一个组合逻辑电路,该电路输入为一位十进制数的2421码,当输入的数为素数时,输出F 为1,否则F 为0。

重置10.设计一个奇偶检测器,当输入的4位代码中1的个数为偶数时,输出为1,否则输出为0。

重置11.组合逻辑电路中产生竞争的原因是什么?竞争可以分为哪两种类型?重置12.什么叫组合逻辑电路中的险象?有哪几种消除险象的常用方法?。